QFN封装CST仿真实例 - S参数,3D bond wire,T和F效率

QFN(Quad Flat No-leads Package,方形扁平无引脚封装)是一种表面贴装型封装,具有成本低、电热性能优良等优势。本案例展示如何高效地对bond wire铜线建模,以及精确快速地仿真QFN封装。

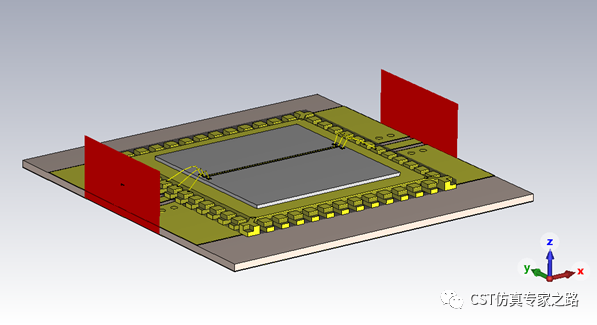

模型大致分为三个部分,上层是Die和铜线:

中层是12x12的QFN封装和引脚,总尺寸7x7mm。

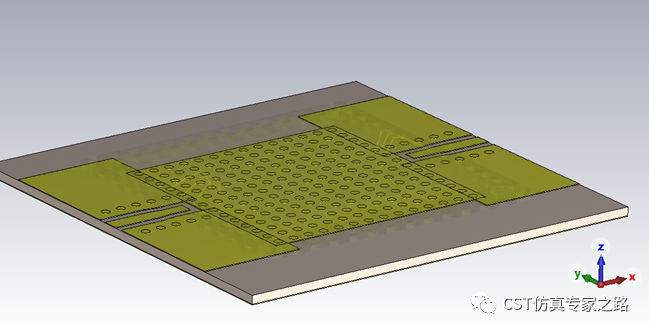

下层是CPW类型PCB,有过孔接地:

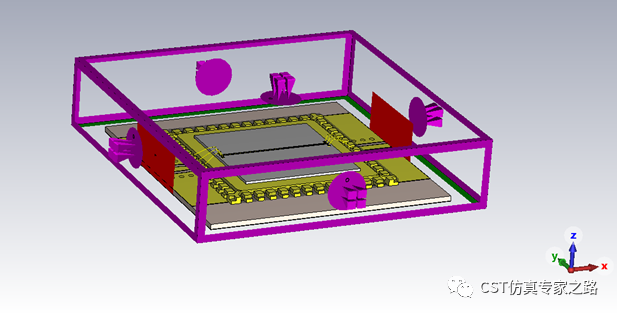

Z-方向电边界:

如何画三维的 bond wire?

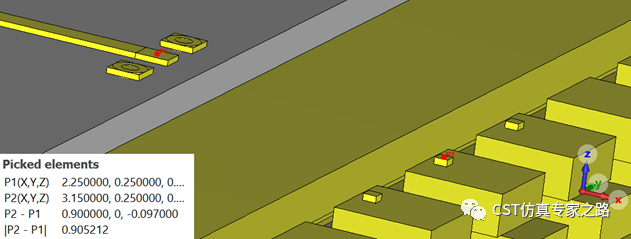

选两个点:

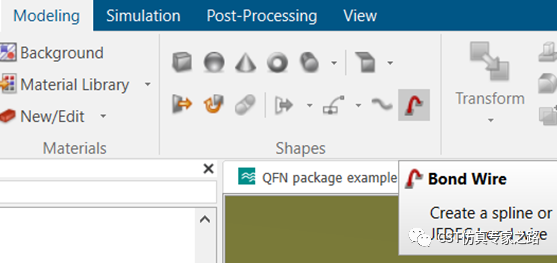

选择bondwire:

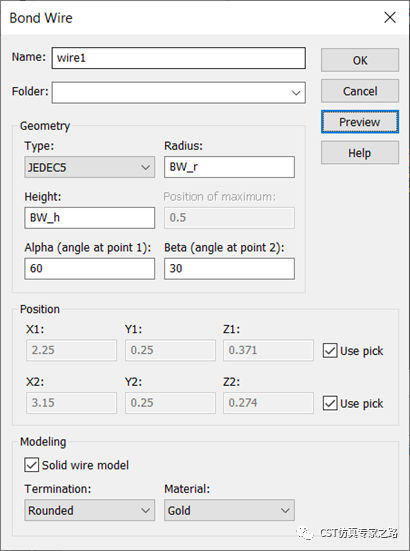

定义尺寸,可参数化:

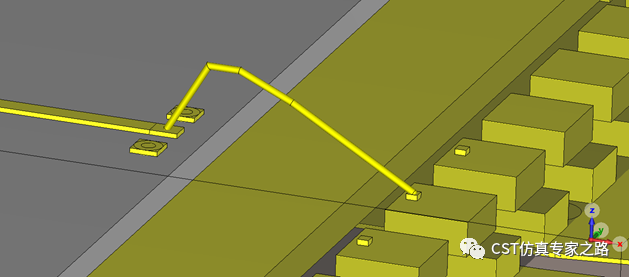

完成:

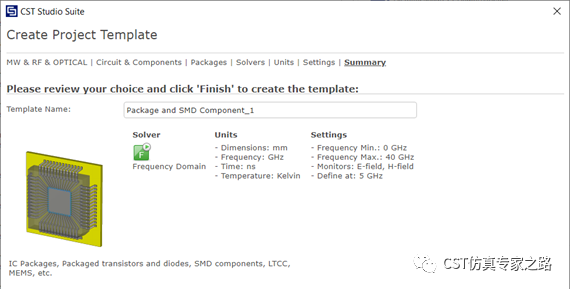

F-solver频域求解器:

仿真使用模板:

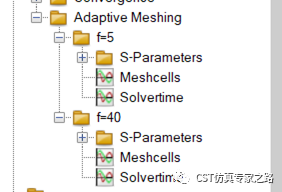

因为有一个场监视器,自动自适应频点会使用该频率和最大频率:

网格过渡比可适当调高,结果一样,提高效率:

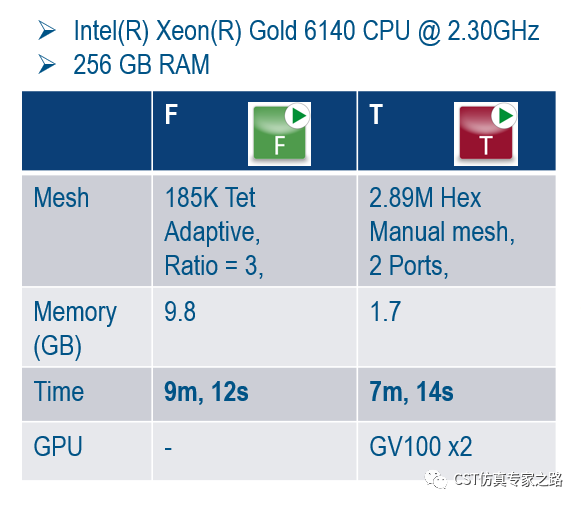

该模型四面体网格185k,40GHz宽频,工作站跑不到十分钟,最大内存消耗10GB。

T-solver时域域求解器:

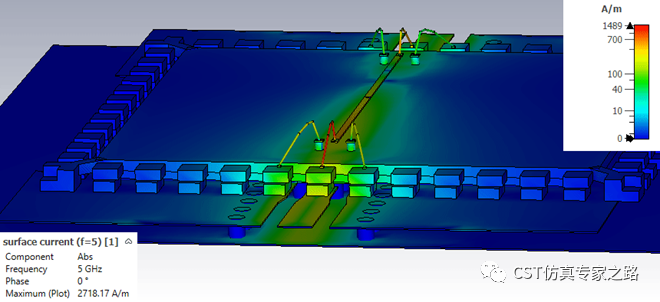

我们先对信号传输区域周围进行本地加密,也就是bond wire和PCB信号线周围:

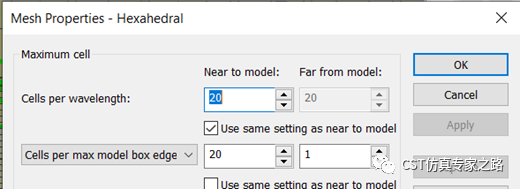

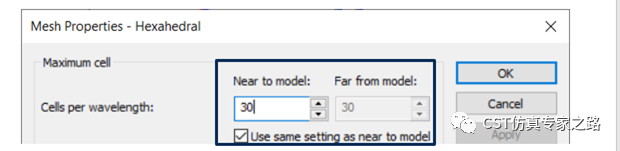

全局网格也可以适当增加:

第一次我们先用默认设置,就是-40dB收敛,全端口,无自适应。

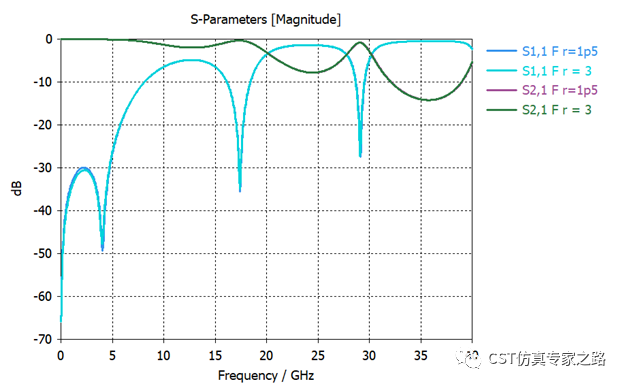

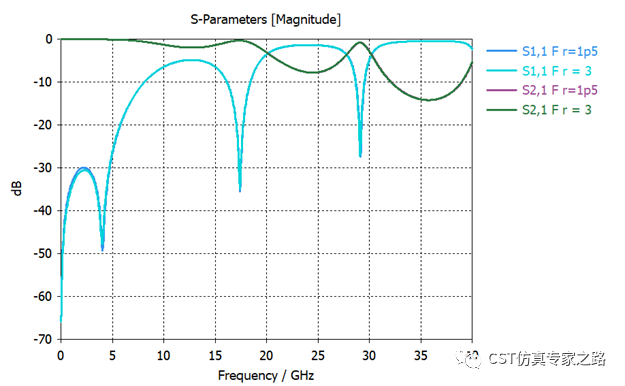

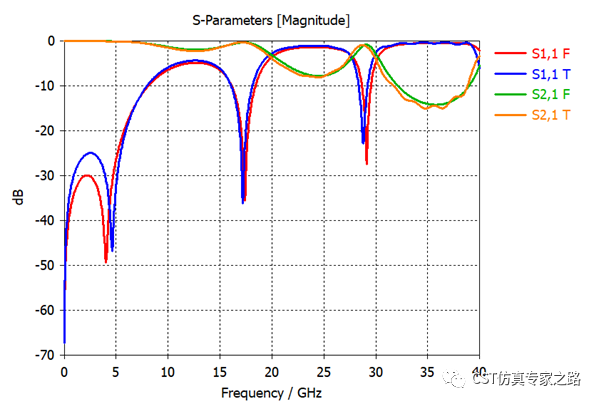

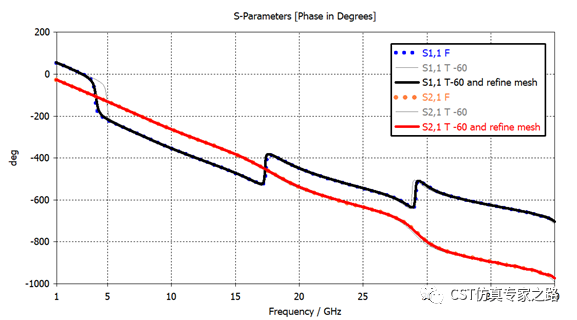

T和F第一次对比:

第一次的对比结果基本一致,用时都不到十分钟,一般这样的结果就够用了。

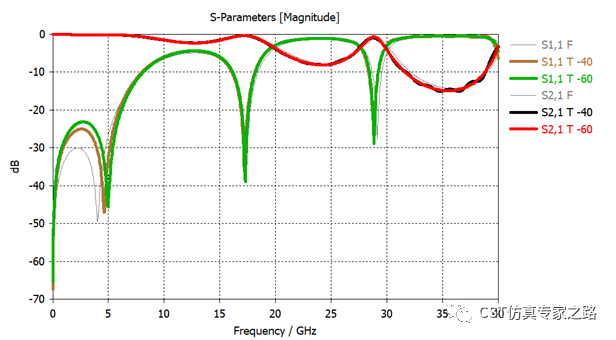

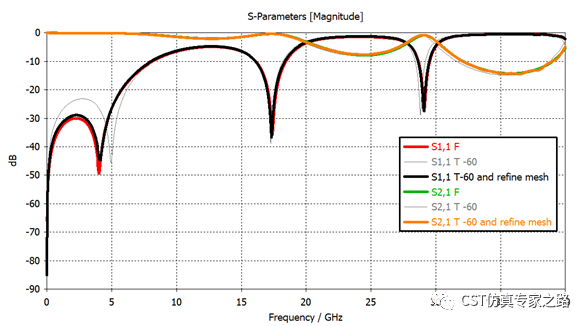

如果继续深挖,可以看到0-5GHz还有一点差别,不过考虑到以及是-20dB以下,很多时候这个差异是可以忽略。另外30-40GHz T-solver出现少量波动,可将收敛从-40dB提高到-60dB,仿真时间增加,结果对比更好。

为了提高T-solver速度,比如前期为了快速看结果,可考虑只激励一个端口,虽然S参数不完整,但是快。

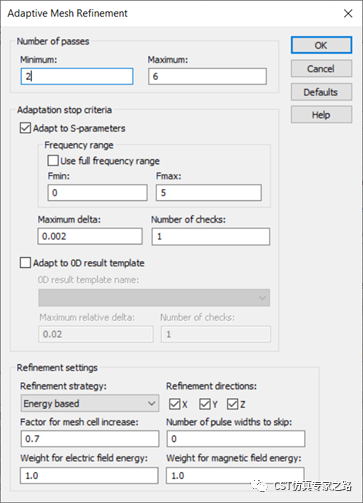

如果想把0-5GHz精确度继续调高,可考虑加密网格,这里我们用全局和自适应的组合方式加密网格:

T和F一致性就更好了:

这里T-solver快速单端口计算时,2.89M网格,GPU加速只需要5分钟。在提高精度后,需要38分钟。

由于该模型比较简单,F-solver四面体并不吃力,虽然频带宽,但扫频效率还是很高的,所以该案例推荐F-solver,当然本案例T-solver也有优势,就是使用的内存非常少。如果封装复杂,尺寸较大,则更需要T-solver。

再展示一下T和F的精确对比:

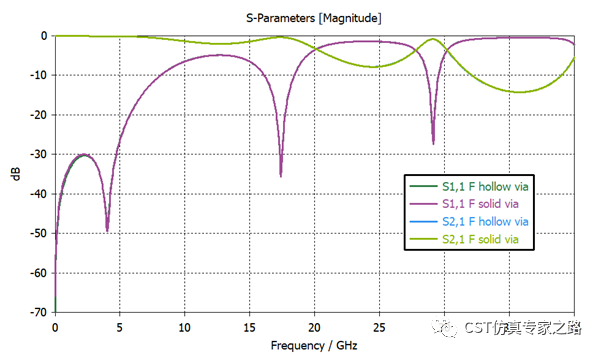

另外,可能有IC工程师习惯性把过孔做成空心,电磁仿真其实是没必要的,只会降低效率:

小结:

1) QFN封装T和F仿真均可,用户可选用不同的精确度和仿真时间。T和F结果可以对比的非常好,这样就增加我们对结果的信心。

2) T-solver适合宽频仿真,六面体能够处理更复杂的模型细节,内存需求小。

3) F-solver 可以提高速度,比如不用空心过孔,调整网格过渡比,或者是自适应的网格增加比例(本文没有展示,是可以提高效率的)。

4) QFN封装仿真就是几分钟的事情。