CST中如何使用partial RLC提取宽带SPICE

来源:CST仿真专家之路

更新时间:2024-06-23

阅读:

作者 | Wang Yuanteng

通常,单一频点导出的SPICE网表是可读的,并且只描述结构在该频率下的行为。对于不需要可读性但希望在整个频段上进行精确建模的情况,我们希望使用宽带SPICE。

虽然仿真实例013:IC封装的RLC提取以及等效电路中曾经提到过,“RLCG生成的SPICE都是单独频点的结果,想要得到宽带的SPICE需要用S参数加Idem工具进行转换”。但时过境迁,尽管关于partial RLC的内容更新较少,其实partial RLC早就可以提取宽带SPICE了。

我们以component library中的Bondwire为例,来看一下具体提取方法。

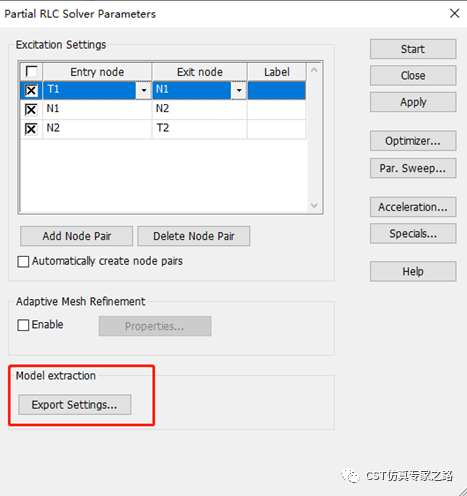

打开BondWire工程,在求解器设置界面,选择Export Settings。

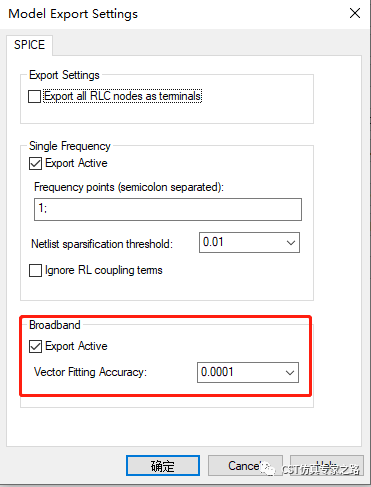

弹出设置界面:

中间是原有的单频点导出功能,可以设定若干个频点。下方即导出宽带SPICE功能。该功能中,求解器使用矢量拟合算法生成SPICE,故同时可设置拟合精度。

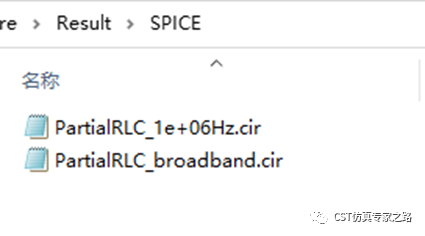

设置完成之后,点击求解器start,仿真结束后即可在工程文件夹下,Result>SPICE下找到SPICE文件。

另外,值得一提的是,相比之前仿真实例010:提取局部电感电阻(2020版新功能)和仿真实例013:IC封装的RLC提取以及等效电路中介绍的一些功能细节,目前partial RLC求解器有一些显著的更新。例如,可以支持Open 边界,增加了网格自适应功能、电流可视化等功能。感兴趣的小伙伴可以自己在新版本体验,帮助文档中亦有相关功能说明。