CST如何生成简单通用的IBIS模型文件

首先,IBIS模型是最常用、最准确的描述数字器件输入输出的模型,通常IC供应商会提供。但是,也有的时候没有提供IBIS文件,通常这种情况下做时域信号仿真便很艰难。所谓巧妇难为无米之炊,今天我们看看CST隐藏的一个小功能,生成通用的IBIS文档,做到无米但是有方便面。

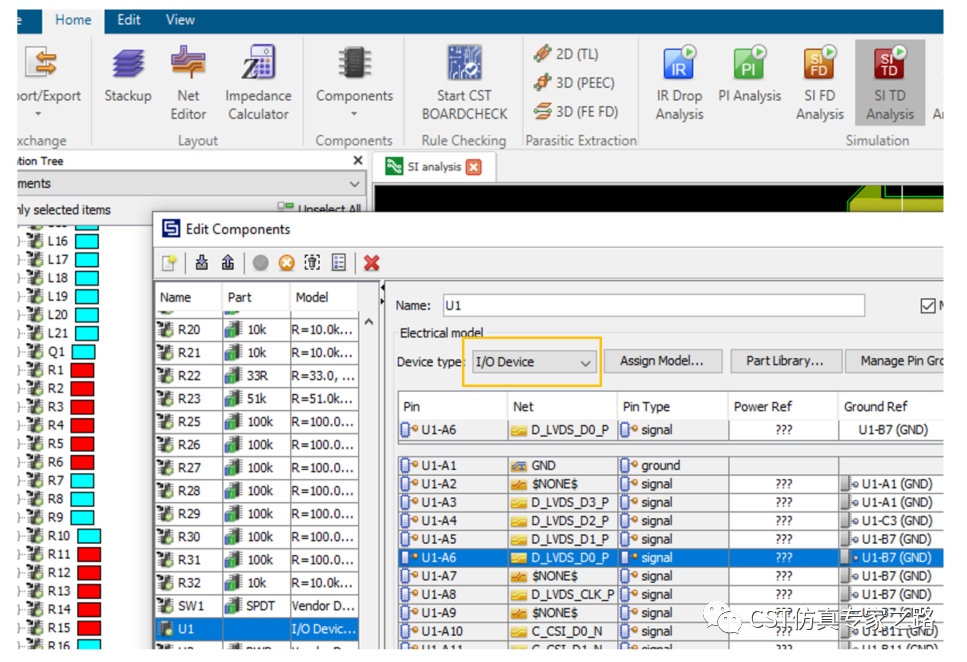

Step1. 打开PCB工作室,正常导入PCB文件,线路Auto-tagging,元件IC作为I/O输入输出,无IBIS文件,所以无法用Assign Model。

Step2. 选择SITD求解器,选择需要生成IBIS模型的针脚,定义任意激励信号Stimulus,这样才能生成仿真任务。

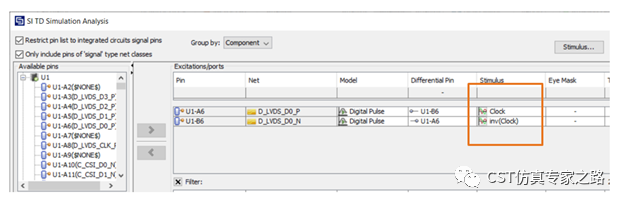

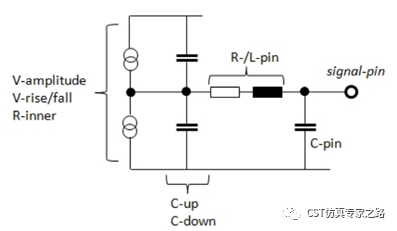

Step3. 在Model处,选择Edit编辑,里面的数字信号相关参数就是IBIS的参数。

硅芯片电容C_comp可以用C-up/down定义,封装参数可以用针脚参数定义。

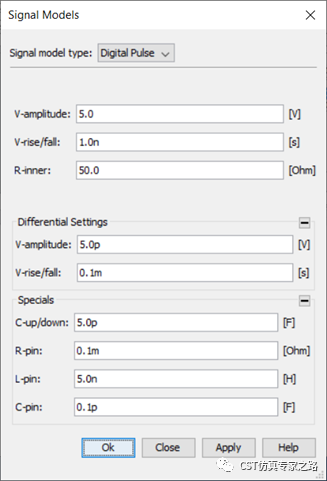

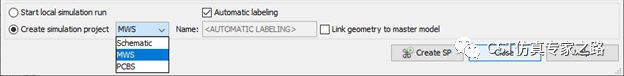

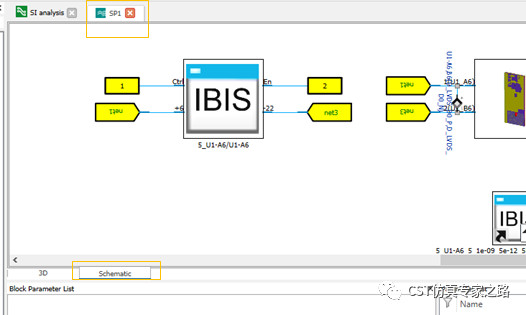

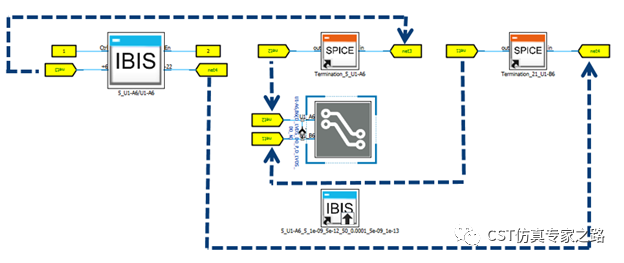

Step4. 生成三维仿真任务MWS或电路任务Schematic:

在生成的子任务的电路中,新的IBIS便自动生成:

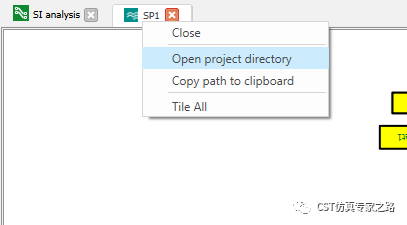

Step5. 可前去其位置查看或拷贝 :

…\ProjectFolder\SP\SP1\Model\DS\ExternalProjects\

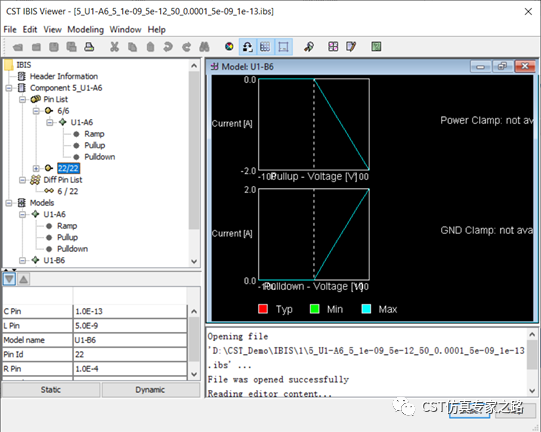

也可电路中右键开其属性,然后用IBIS Viewer查看,I/V曲线是简单的内阻模型。

具体参数定义参考帮助文档:

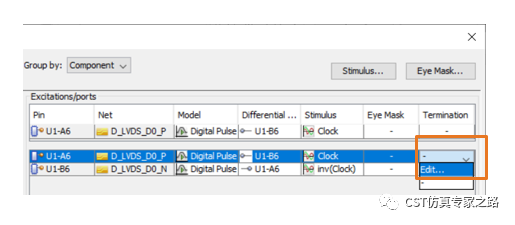

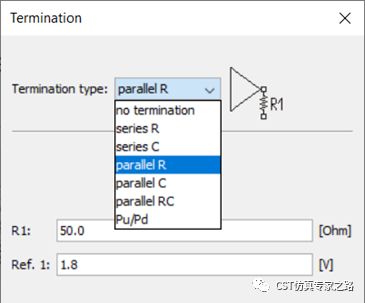

补充内容,SITD中有Termination可以修改,能够快速查看不同的负载对IBIS驱动器输出的的影响。

这个负载是自动生成的SPICE文件,处于IBIS缓冲器和三维电路之间,这种SPICE是含这里Model信息的,比如针脚in电阻和IBIS一致。

总结,该功能很多人不知道,因为生成的模型虽简单,但很救火,最重要的是能够跟实测效果吻合的非常好,很适合没有真正IBIS模型的情况。