CST系统级RS仿真(五)- EUT测试布置建模及扫频模式仿真

作者 | Zhou Ming

CST系统级RS仿真(一)——天线建模

CST系统级RS仿真(二)——RS仿真场地较准(扫频模式)

CST系统级RS仿真(三)——RS仿真场地较准(单点加扰模式)

CST系统级RS仿真(四)——生成RS调制信号

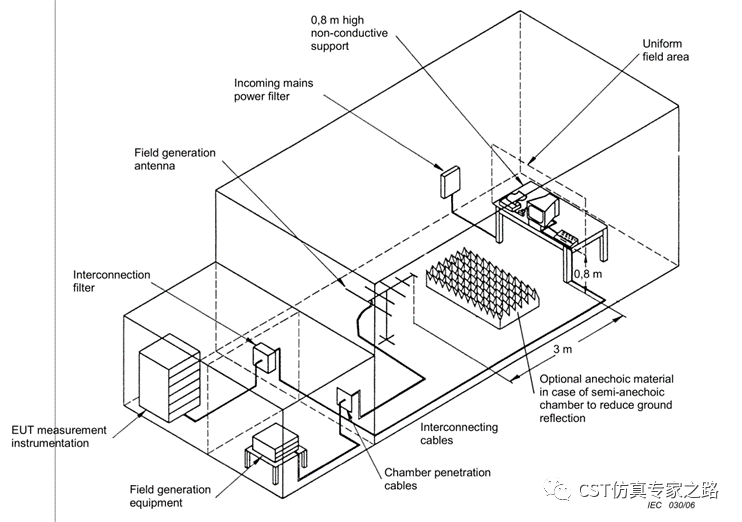

本期将继续介绍进行系统级RS仿真的方法。下面是IEC61000-4-3标准中规定的测试场景,我们3D建模的EUT布置,要符合标准的要求。

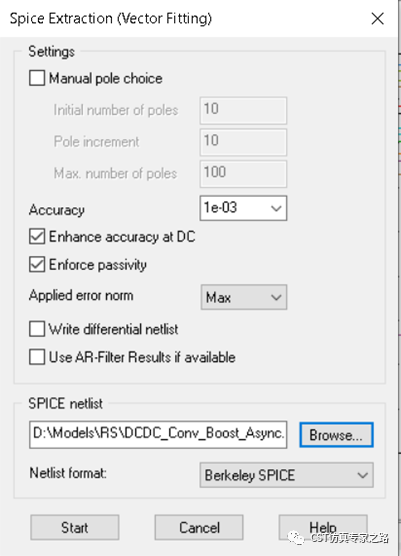

利用Spice Extraction把S参数转换成spice模型。一般来说,CST的Spice Extraction已经能够满足要求,如果需要更高精度的仿真(例如SI仿真),建议使用CST 专用的宏模型处理工具IDEM。

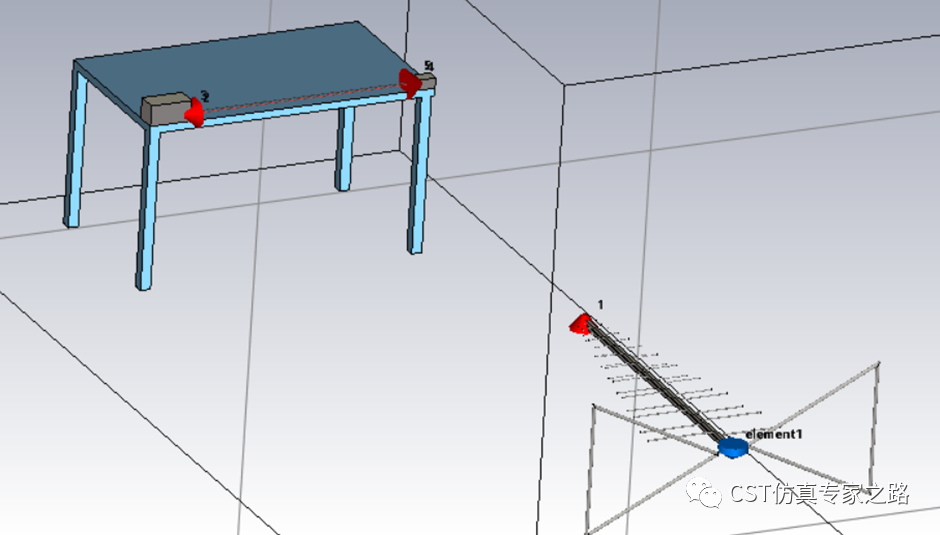

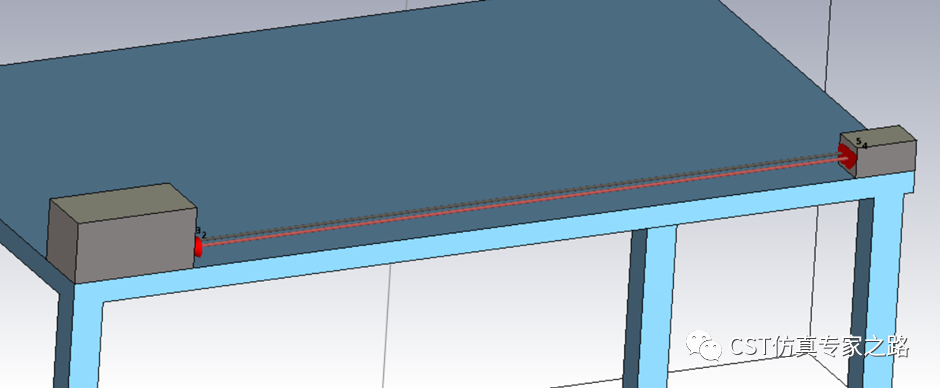

接下来创建3D模型,左侧为LISN,右侧为电源模块,中间为两根DC输入cable。

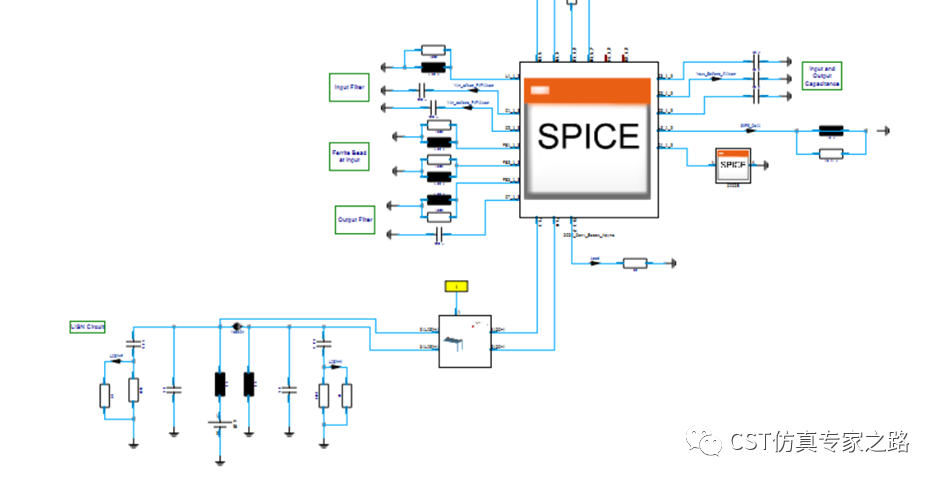

3D模型创建好之后,回到CST电路工作室,导入PCB的spice模型,完成电路模型的搭建。

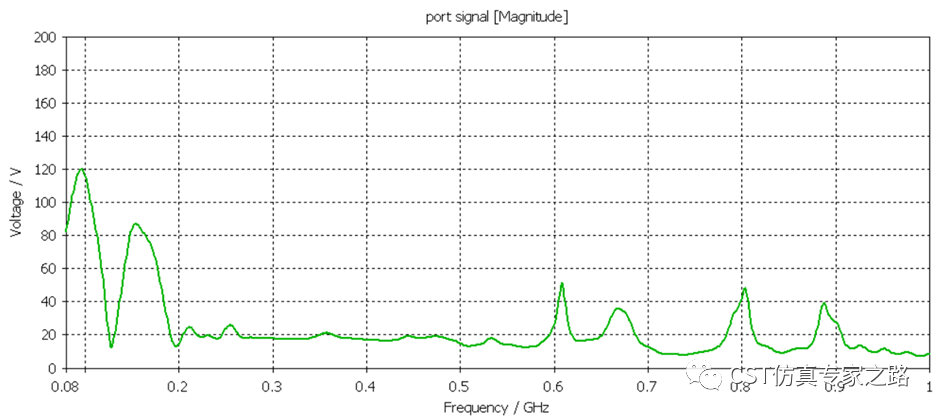

然后,我们进行扫频模式的仿真。创建一个AC task,用CST系统级RS仿真(二)——RS仿真场地较准(扫频模式)中较准后的port signal作为激励。

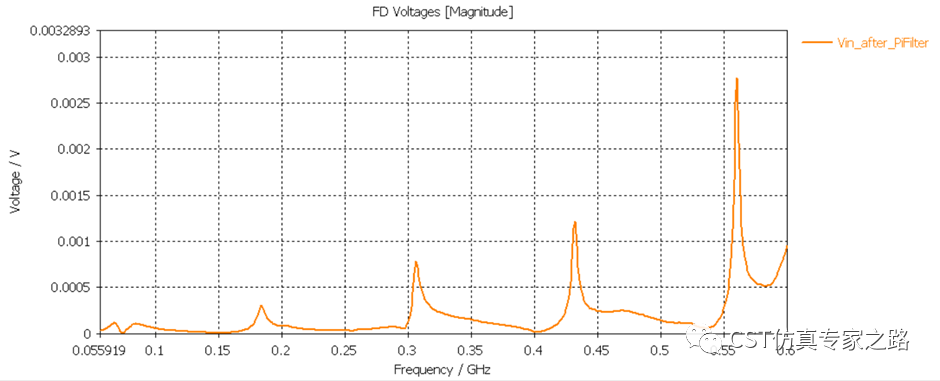

运行后我们可以看到不同位置的接收的干扰噪声量级。下图是DC+与DC-之间的差模噪声。

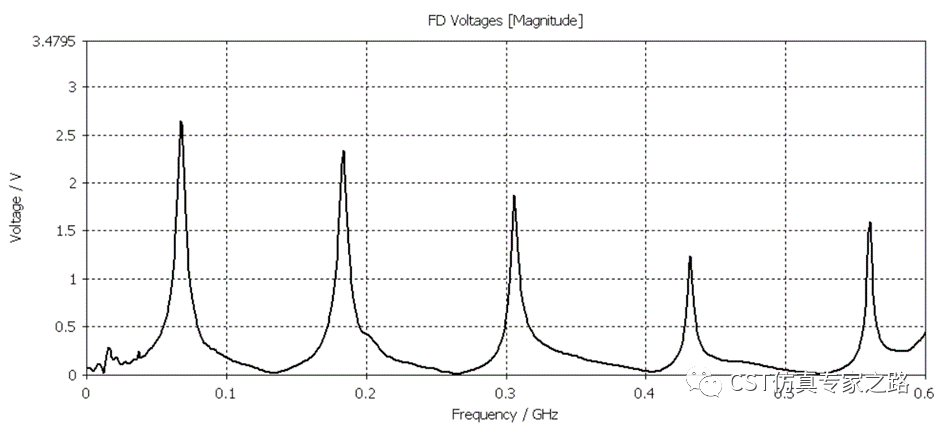

同样,我们也可以得到PCB板上C1_1_2电容上的差模噪声,如下图。