芯片封装S参数提取方法(一) - CST差分线S参数仿真实例

本期介绍CST在EDA领域里的应用案例—芯片封装S参数提取。在信号完整性仿真中,S参数是一切链路仿真的基础,CST软件在信号完整性领域里有着非常强大的实力。在介绍案例之前,先介绍一下CST软件在EDA里的优势。

(1)强大稳定的Layout导入能力,不仅支持市面上几乎所有的layout工具,并且能快速转换成三维模型,并自动划分网格。

(2)完备的仿真技术:在EDA三维仿真领域,独家的时域求解器(FIT)和PBA网格技术能处理任意复杂的结构,由于时域算法对计算资源的要求没有频域有限元那么大,可以仿真非常高频的EDA问题。同时CST也具有频域有限元算法作为低频EDA部分仿真的补充。两种算法可以相互验证,提升工程师的信心。

还有其他的优势如TDR仿真,独家的SPICE模型提取工具IdEM等,放到后续相关题目时再谈,我们先进入正题。

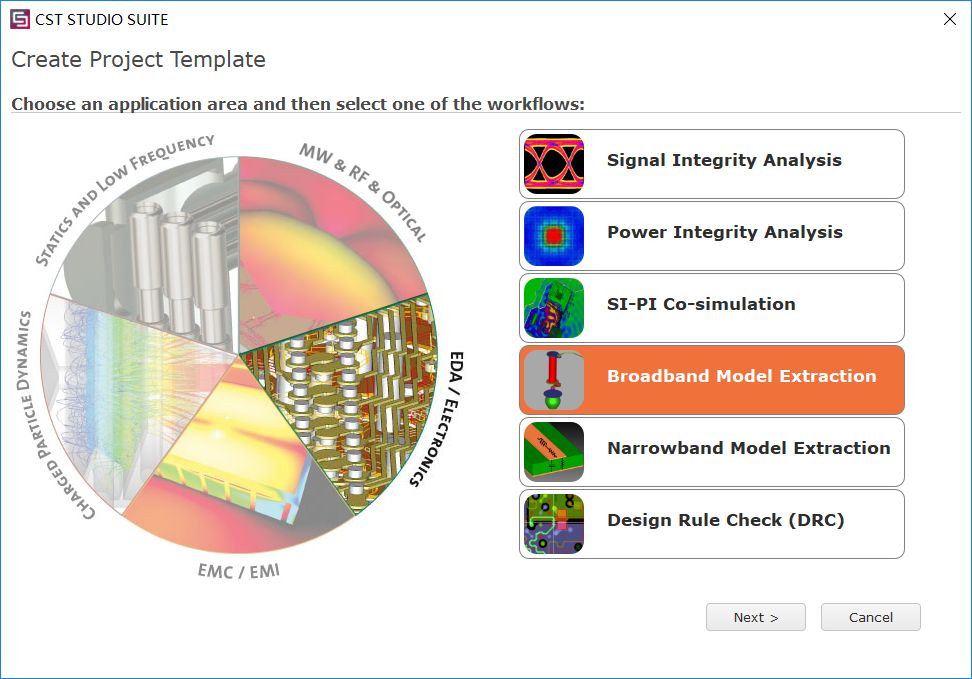

模版选择

和其他仿真一样CST仿真芯片封装时也提供仿真模版,选择模版可以简化用户对仿真参数的设置。这里模板选择宽带模型提取如下图片所示:

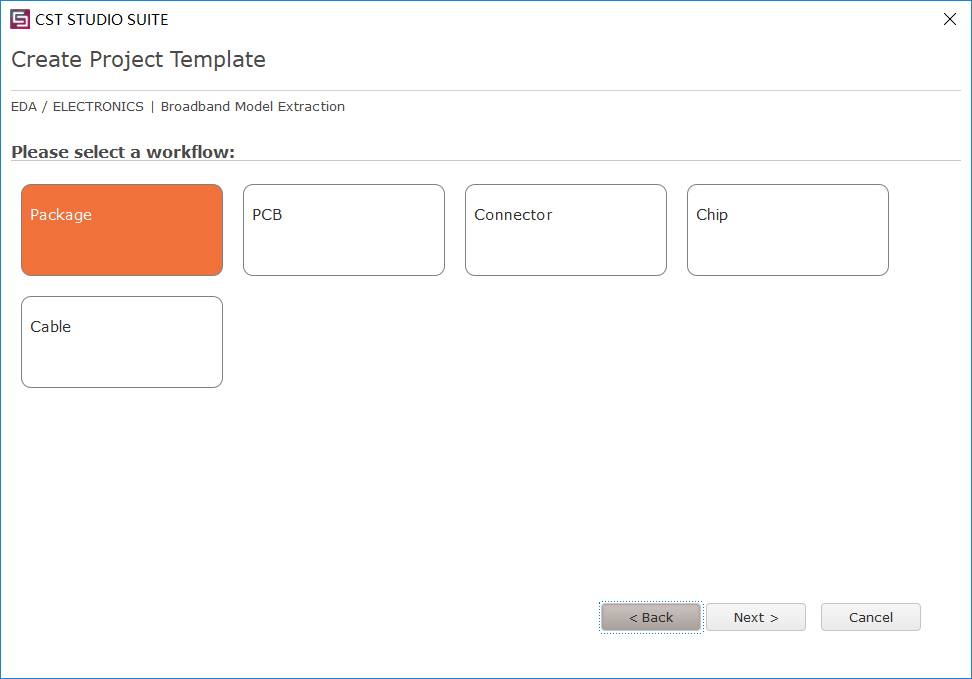

这里我们选择封装,如下图所示:

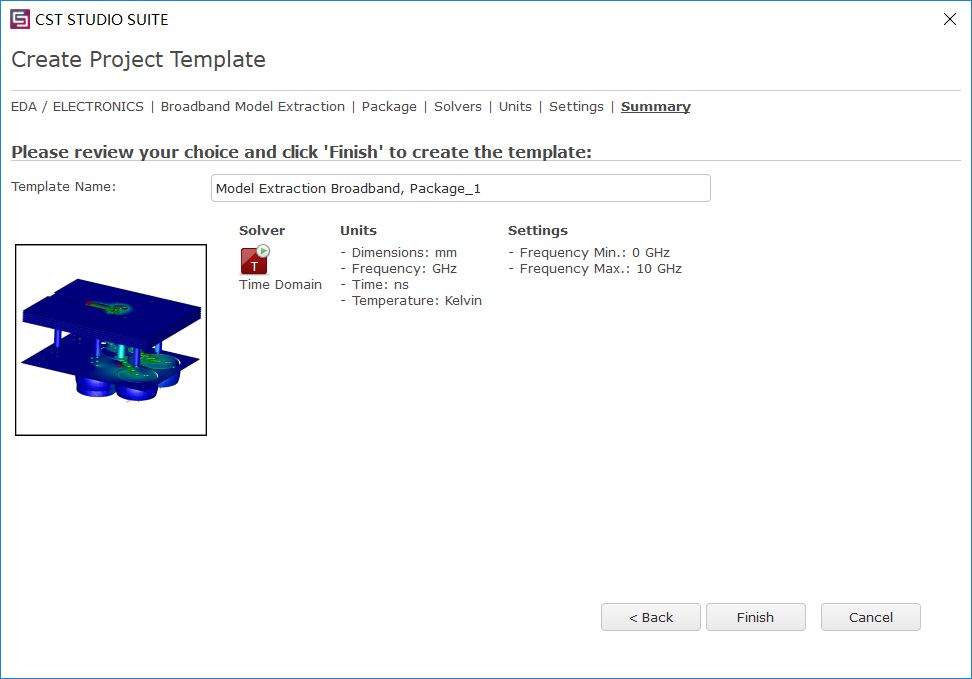

其他选择不一一赘述了,选择时域算法,单位和频率范围如下图所示:

因为是案例制作,我这里选择到10GHz,用户可以根据实际需要,选择更高的频率仿真。然后点击Finish完成模版制作。

EDA(芯片)文件导入

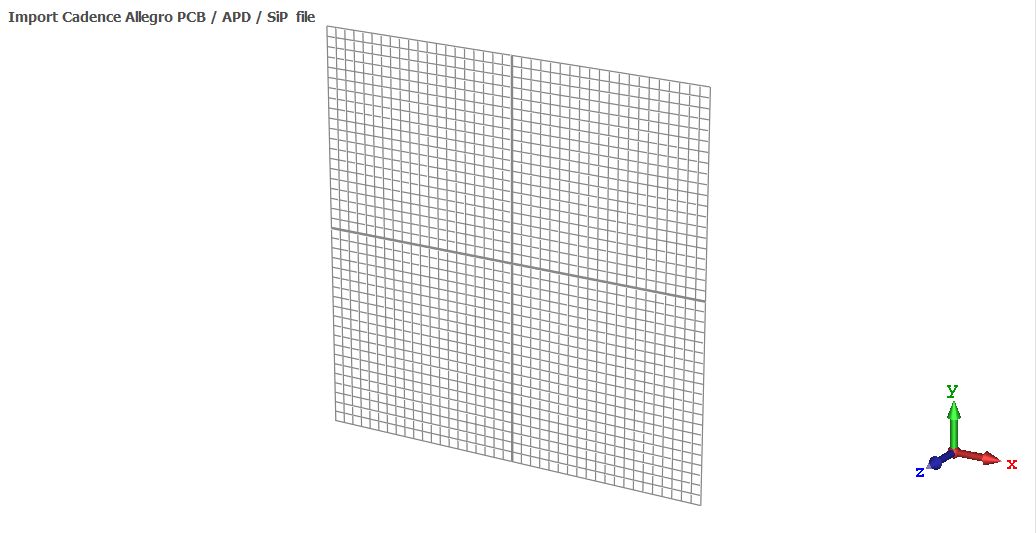

可以直接将EDA仿真文件直接拖拽到窗口内然后放开鼠标(drag&drop)来导入EDA文件,如下图所示:

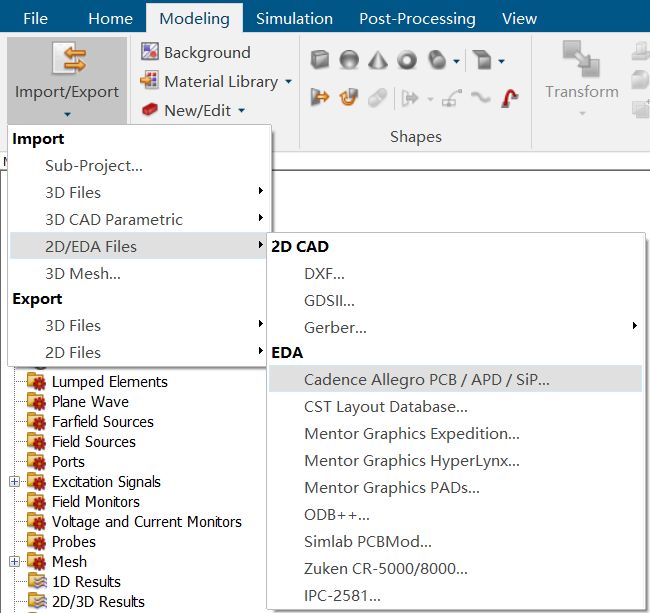

也可以通过点击Modeling选项卡下的Import,并选择EDA文件,本例中导入的是Candence的*.sip文件,如下图所示:

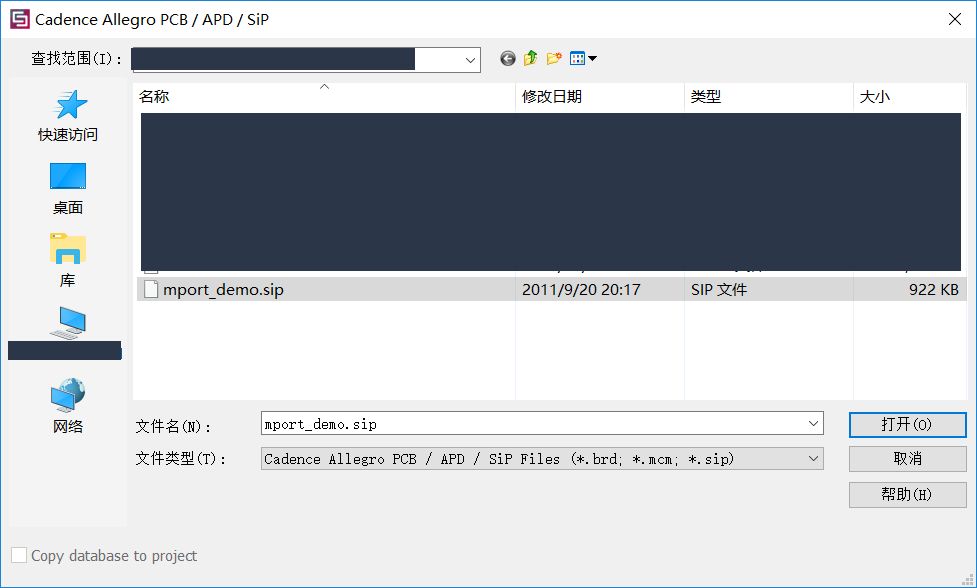

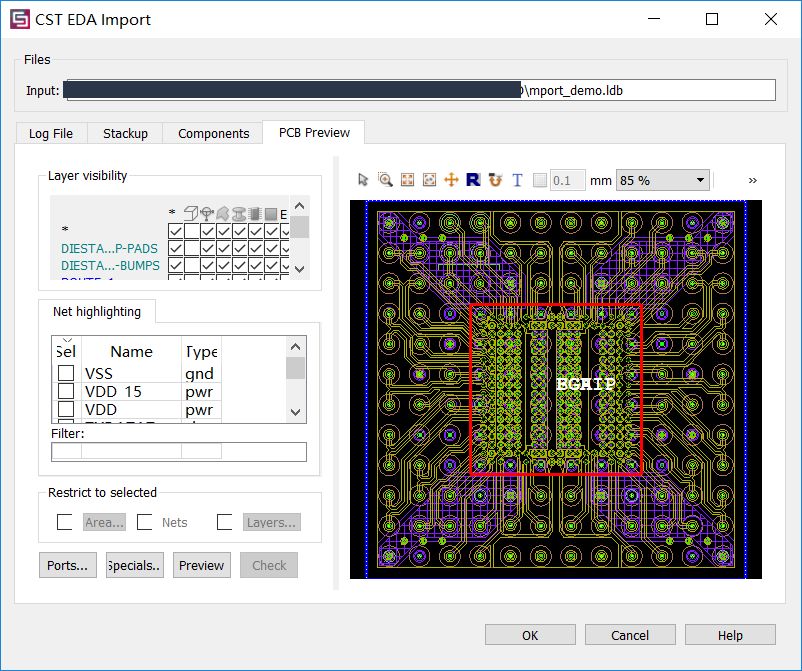

点击打开后,会弹出CST EDA-import的界面,如下图所示:

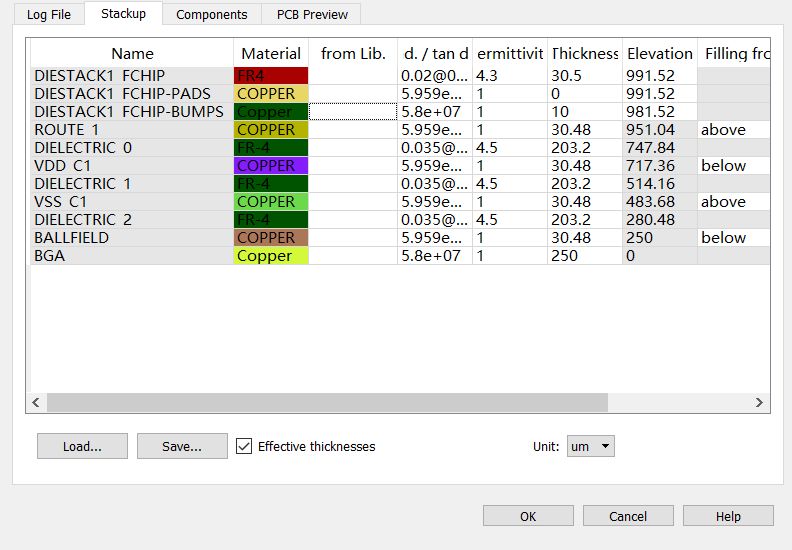

在这个界面下,可以设置包括堆叠材料特性、厚度、铜箔、键合丝、焊球、焊盘尺寸等各种信息。当然如果这些在设计时候已经设置好,导入后就不需要更改了。如本例中从模型的倒装芯片层到BGA层,都可以自定义材料特性、厚度,铜箔的形状等,如下图所示:

自动端口设置

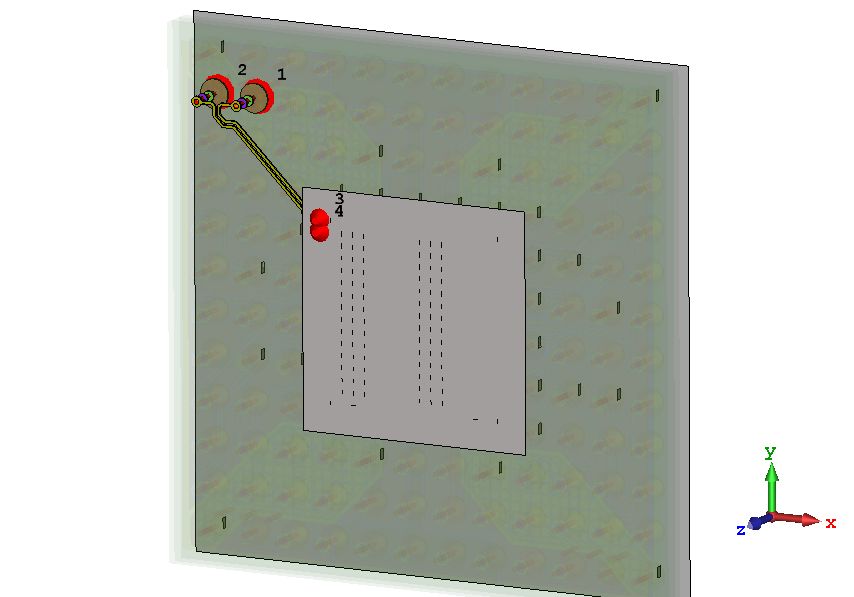

例如我们要仿真提取其中一对差分对的S参数,TXDATA0+和TXDATA0-,这对线从倒装芯片的RDL层到BGA焊球的链路,我们在PCB Preview页下的Net highlighting勾选要仿真的线,此时这对线会在预览图中,高亮显示,如下图所示:

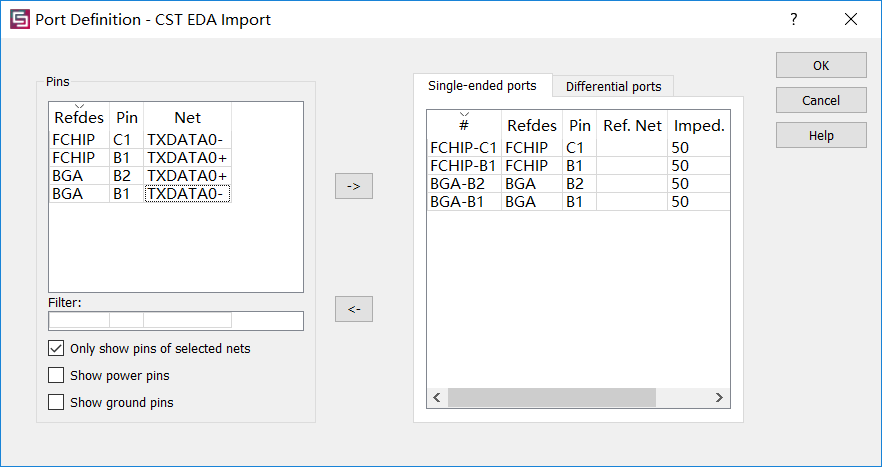

点击Ports,勾选Only show pins of selected nets,此时只会显示勾选的网络,点击->,将这对差分线的四个pin,自动设置为单端port,如下图所:

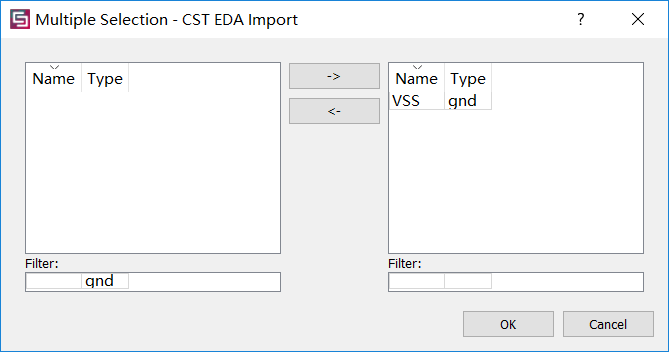

点击Ref.net,本例中,将单端port的参考地设置为VSS,点击如下图所示:

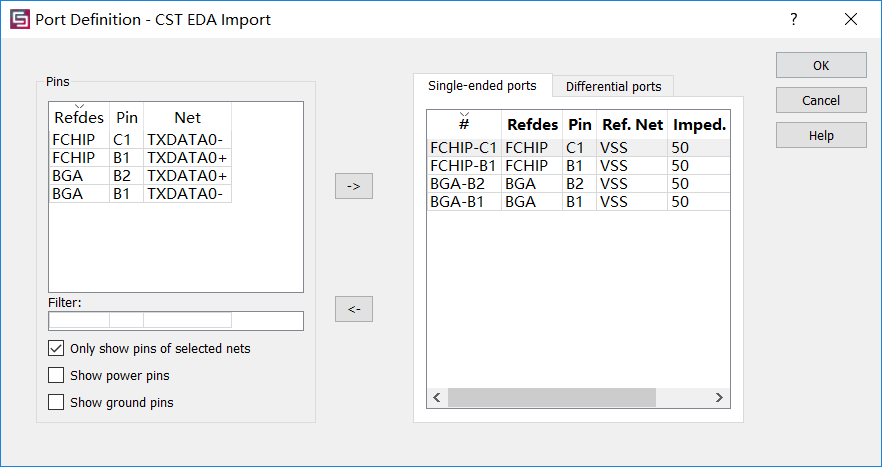

设置完成后的端口界面,如下图所示:

点击OK,此时预览图中,出现了自动设置的4个单端Port,如下图所示:

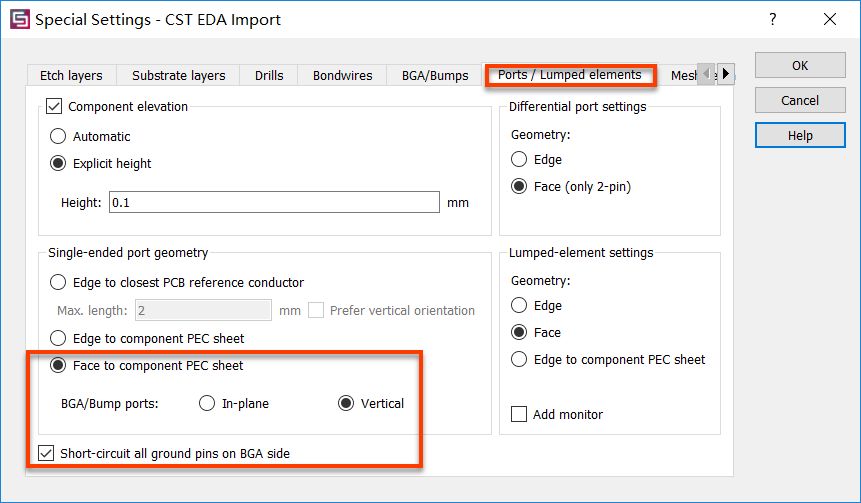

其中,需要点Specials按钮,对端口进行如下设置,软件会自动在芯片层和靠近BGA层处生成两个接地平面,并将所有的GND网络与其自动连接,如下图所示:

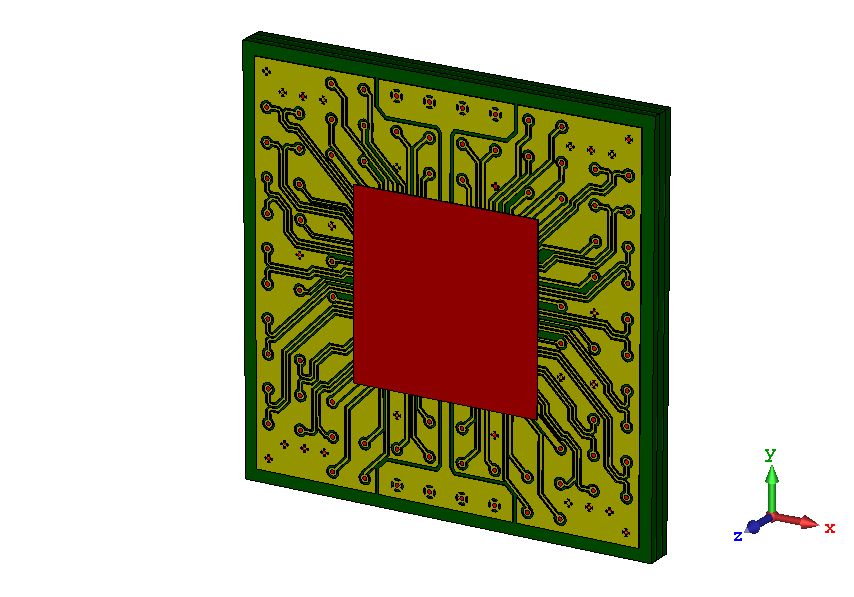

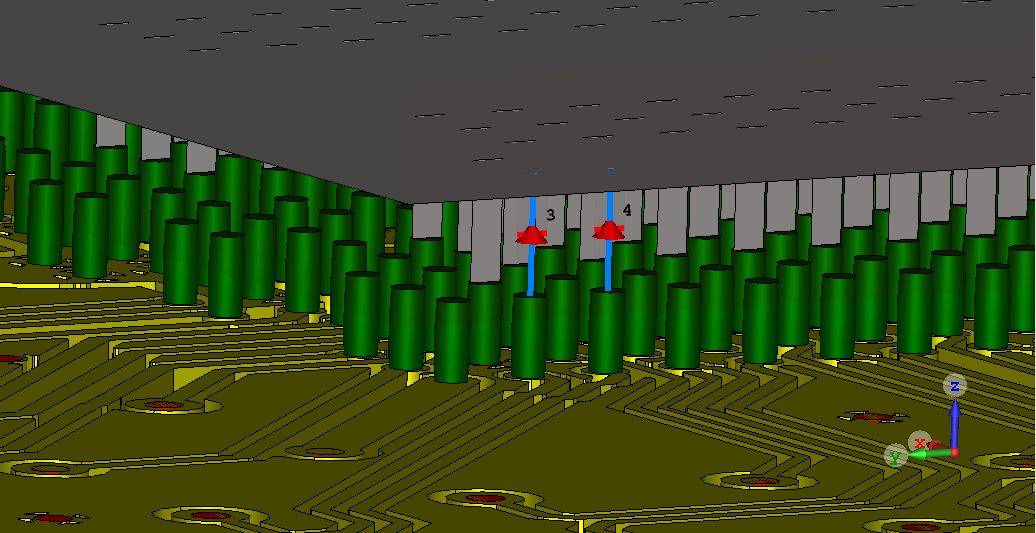

点击OK,EDA就完全导入为3D模型到CST微波工作室中了,如下图所示:

例如我们要仿真提取其中一对差分对的S参数,TXDATA0+和TXDATA0-,这对线从倒装芯片的RDL层到BGA焊球的链路,如下图所示:

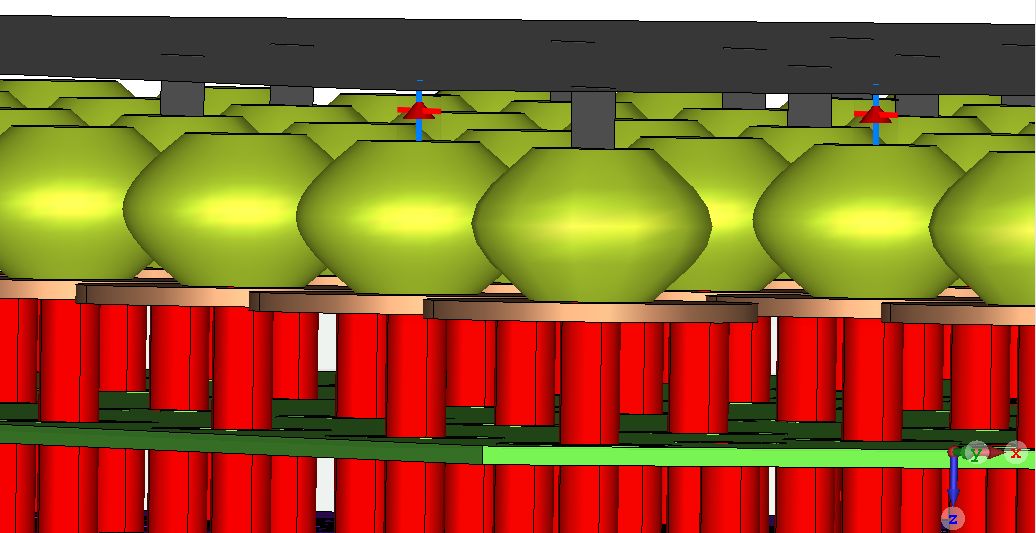

BGA处的端口是自动添加在BGA焊球和辅助接地平面之间,BGA的GND网络,自动与该辅助接地平面连接,如下图所示:

点击View选项卡下的Axes Scaling按钮,放大Z轴方向的视图,如下图所示:

我们可以看到,在视图中,Flip-Chip(倒装芯片)处也自动添加了一个辅助平面,将端口3和端口4自动添加在RDL层与辅助接地面之间,同时辅助接地面与Net中的接地网络自动连接,如下图所示:

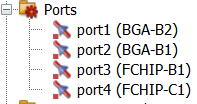

本案例中4个离散面端口都是自动设置的,如下图所示:

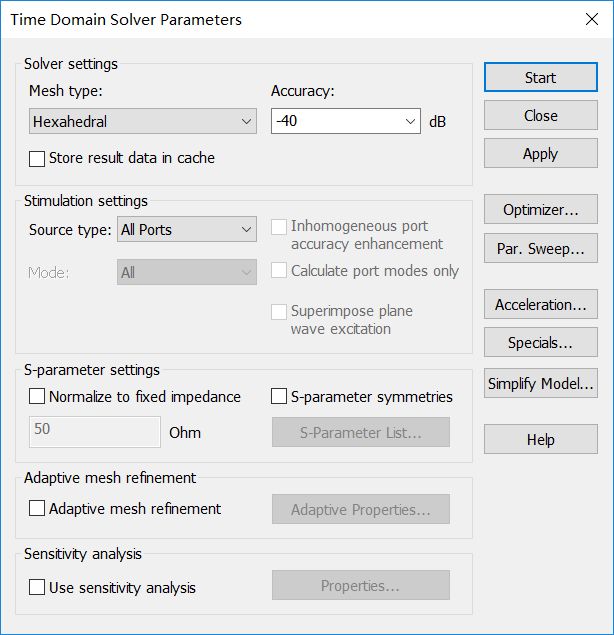

本例中,我们将频率范围设置为0GHz-10GHz,边界条件Open add space,此时这对差分线上的网格细节,如下图所示:

仿真结果和提取S参数

点击时域求解器,运行仿真,如下图所示:

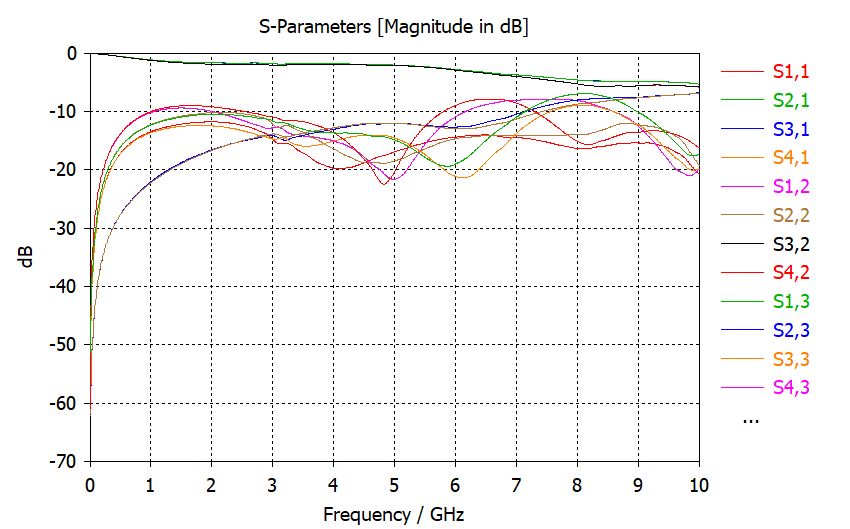

得到S参数结果,如下图所示:

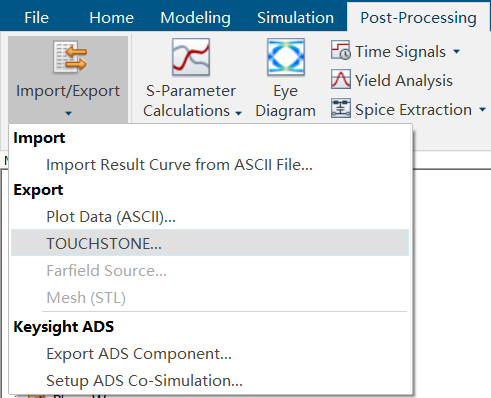

点击Post-Processing选项卡下的Import/Export按钮,选择Export TOUCHSTONE...,如下图所示:

在下图中,点击OK,如下图所示:

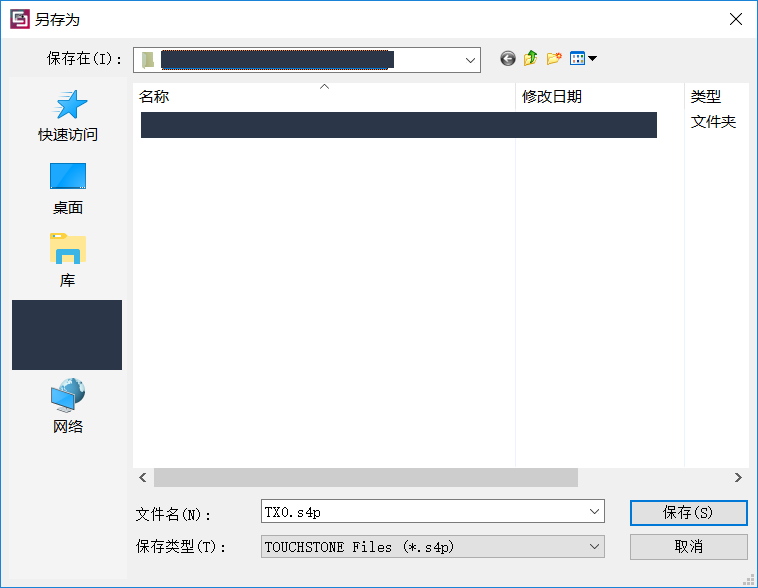

并保存*.s4p,如下图所示:

这样就提取了芯片封装上这一对差分线,四个单端端口的S参数了。

小结

本期完成了芯片封装S参数提取的仿真过程。后续我们还会介绍如何用提取的S参数做信号完整性的仿真。