如何在Chip Interface中设置沉积共形?

作者 | Wang Yuanteng

我们在“如何使用Chip Interface导入GDSII文件?”中介绍过使用Process Queue模拟IC制造的步骤。其中沉积是其中非常重要的步骤,那么如何设置沉积共形呢?

下面我们以一个具体模型为例,介绍沉积共形的设置方法。

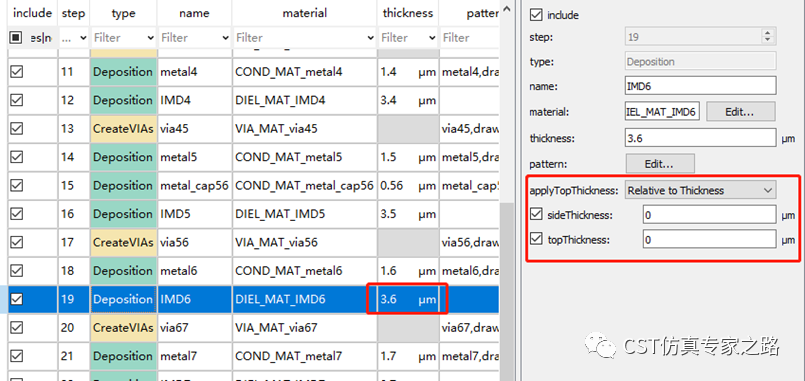

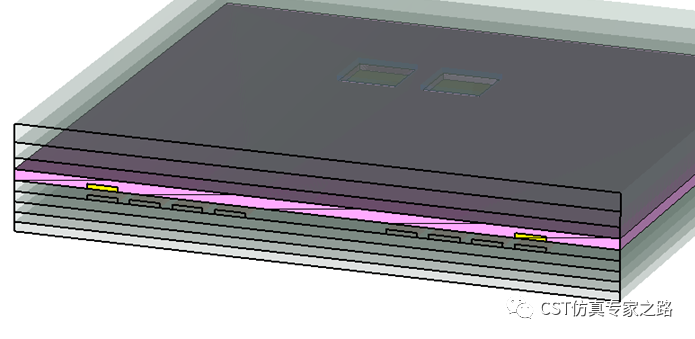

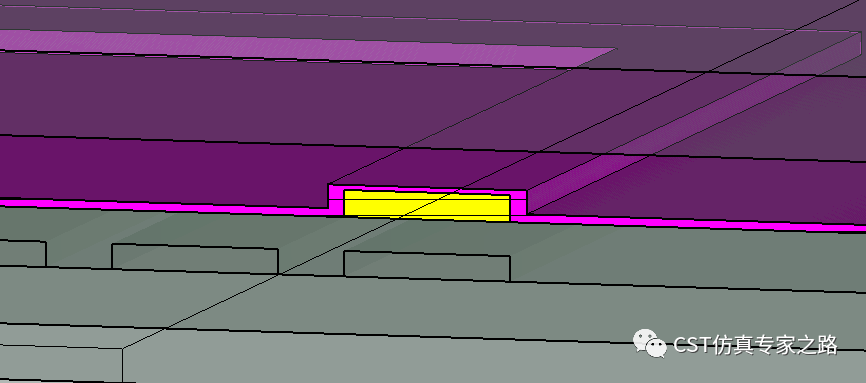

该例中,图中所示粉色部分为沉积层IMD6,厚度为3.6um,图中黄色部分为上一步生成的金属层metal6。此时,沉积层设置为默认设置,从图中可以看出并无共形。

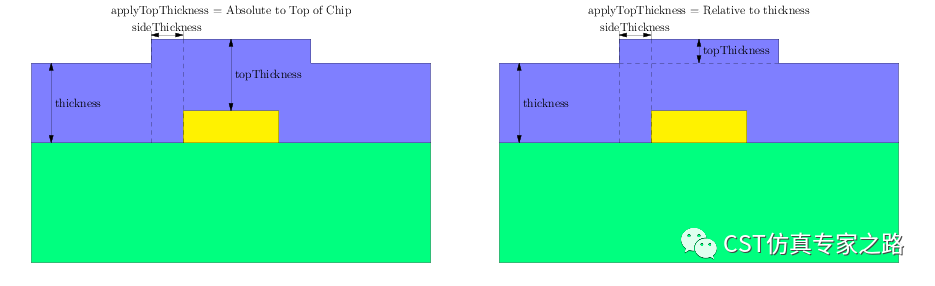

参考帮助文档,其中对沉积共形设置做了明确解释:

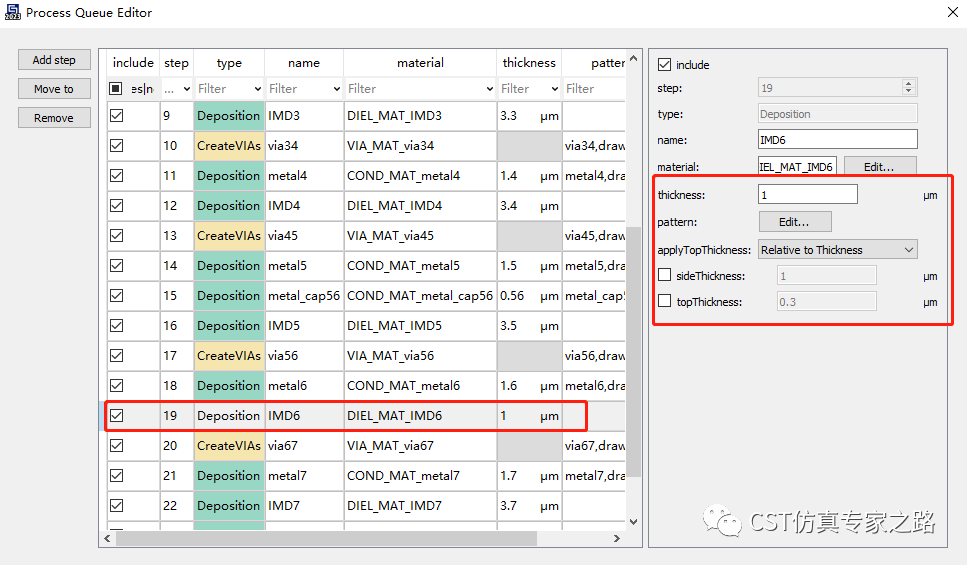

沉积共形由3个厚度决定,分别是图中的thickness、sideThickness和topThickness。其中,topThickness的定义方式有两种,可以是参考到芯片上方的Absolute to Top of Chip,也可以是参考到整个沉积层的Relative to thickness。另外,如果未指定sideThickness,那么该值与thickness相同。同样的,如果topThickness没有指定的话,也被认为等于thickness。

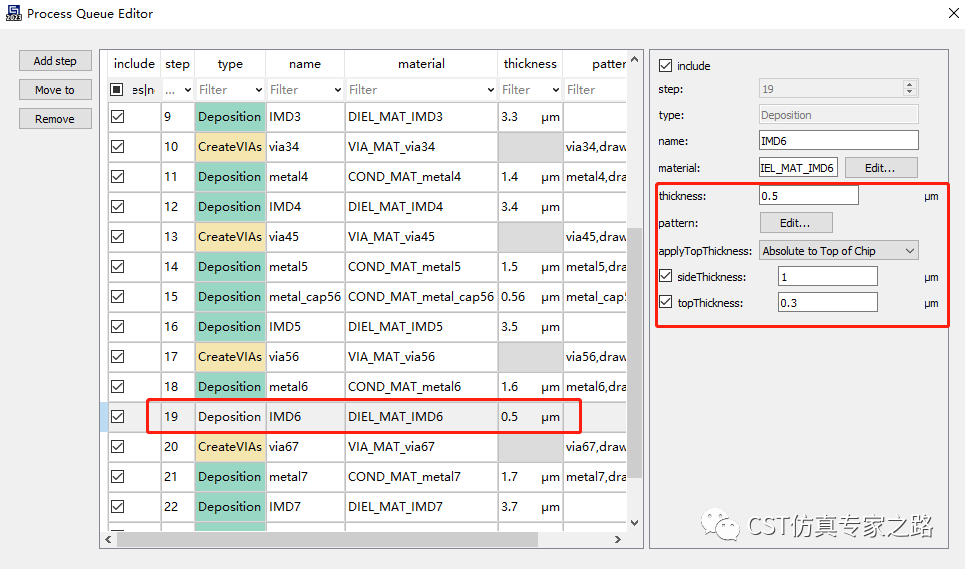

了解清楚后,我们尝试一下修改沉积共形设置如下。将沉积层整体厚度改为0.5um,sidethickness为1um,topThickness为Absolute to Top of Chip 0.3um,也就是芯片上面高出0.3um。

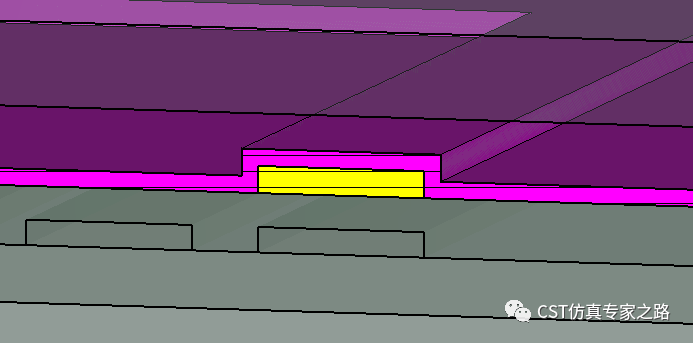

生成沉积共形效果如下:

再来看对sideThickness和topThickness都没指定设置的情况,只设了thickness为1。

从下图可以看出,正如前文所说,sideThickness和topThickness均为1um,在金属线的周围是一个均匀厚度的1um共形。

搞清楚共形如何设置之后,我们就可以根据实际需要进行共形设置了。