CST 防雷击电路EFT仿真(三)

CST的防雷仿真已经介绍了两期,分别介绍了浪涌发生器建模和典型防雷电路的仿真。

本期重点介绍基于CST的场路协同仿真方法的防雷仿真。场路协同相信大家一定不陌生,可以说是CST的看家本领了。场路协同仿真总共分三步:3D建模--->电路建模并与3D的连接--->场路协同仿真。

下面我们来详细介绍基于CST场路协同方法的防雷仿真流程。

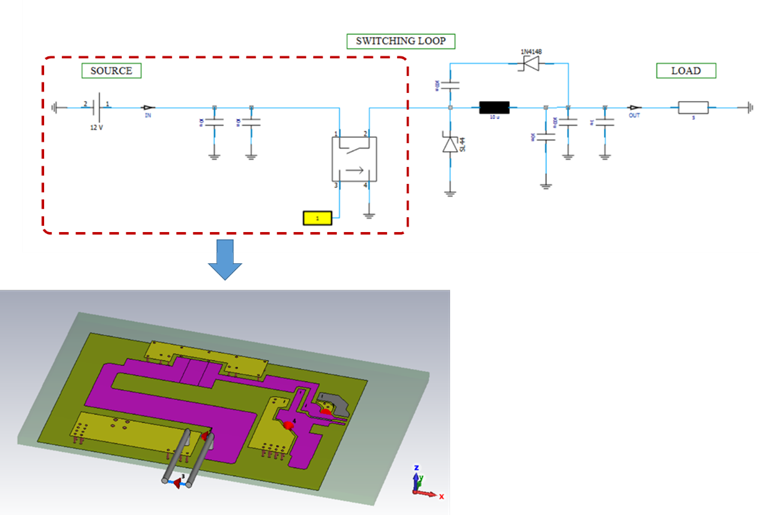

第一步:3D建模,如下图所示。

为缩短仿真时间,只截取了下面电路图中电源输入到MOS之间的部分PCB作为仿真模型。其中黄色为电路中对应的GND,紫色为Vin+。分别在电源输入pin,MOV的位置,以及MOS Vds位置增加端口。

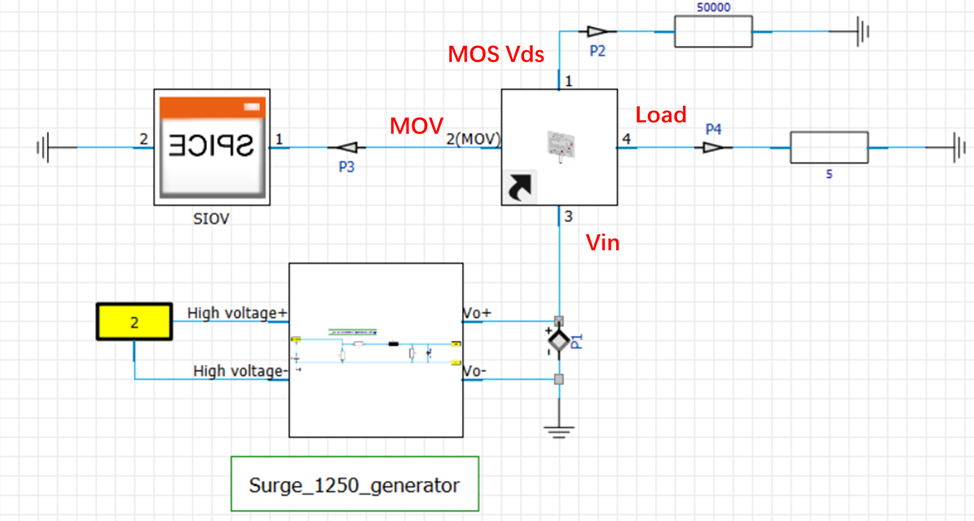

第二步:电路建模并与3D的连接,如下图所示。其中浪涌发生器电路可以参考CST 防雷仿真(一)

第三步:场路协同仿真

首先在schematic中创建transient仿真任务。在这里可以选择“传统”的场路协同方法,即Transient (Combine results),也可以选择真正的场路协同仿真,即CST transient co-simulation。如下图所示。

CST: “Traditional” Co-Simulation.

CST transient co-simulation: True Transient Co-Simulation.

由于浪涌信号时间相比ESD信号时间长得多,所以如果使用CST transient co-simulation方法,仿真时间较长。因此可以根据仿真应用场景,选择更合适的仿真方法。在这个案例中,笔者采用的“传统”的场路协同方法。

【仿真结果分析】

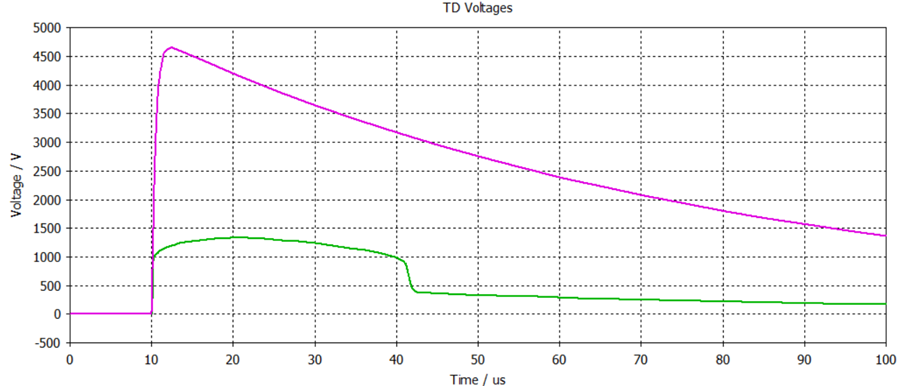

一、浪涌电压分析

观察浪涌电压注入后PCB的整体电场分布及局部MOS Vds的电场分布。有MOV的条件下,MOV后的PCB走线残压明显较小,MOS Vds的电场明显较小,也可以通过对比残压曲线得到该结论。

PCB电场分布动图对比:

无MOV

无MOV

有MOV

有MOV

局部MOS Vds的电场分布对比:

无MOV

无MOV

有MOV

有MOV

MOS Vds对比图:

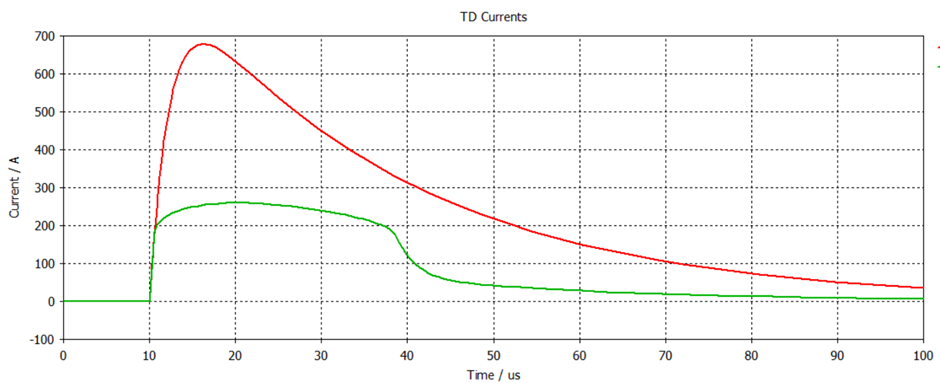

二、浪涌电流分析

观察浪涌电压注入后PCB的整体表面电流分布及局部Load上的电流分布。有MOV的条件下,浪涌电流基本集中在MOV之前,在MOV后的PCB走线上,浪涌电流明显较小,Load上的电流明显较小,也可以通过对比Load上的浪涌电流曲线得到该结论。

表面电流分布动图对比:

无MOV

有MOV

表面电流分布云图对比:

无MOV

有MOV

Load电流分布对比图:

【总结】

1. CST的场路协同仿真方法非常适合含有非线性器件电路的瞬态仿真分析。

2. 浪涌仿真由于频率较低,求解器的选择及仿真方法的选择对仿真时间的影响较大。

3. 防雷设计如同治水,堵不如疏。但即使是增加了防雷器/器件,后级仍然存在一定的残压。这就需要考虑到广义的电磁兼容性设计,让每个器件在雷击环境下都能正常工作。