CST中,IC封装的RLC提取以及等效电路实例

之前介绍了pRLCG求解器,见仿真实例010:提取局部电感电阻(2020版新功能)。本期分享一篇关于IC封装线的寄生参数提取的具体应用案例。同时也借用这个例子,看一下如何拆分等效电路模型。

Step0 导入模型

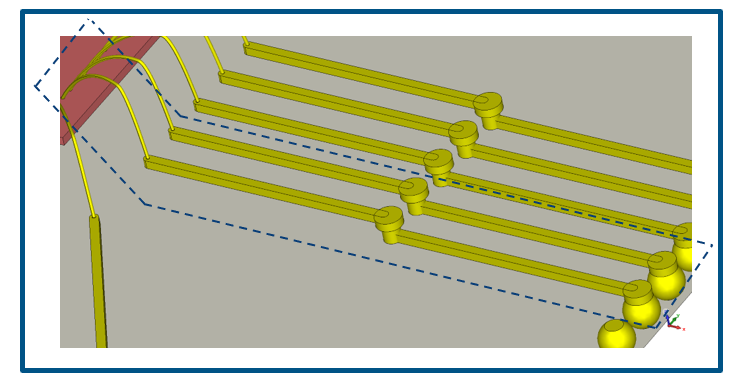

我们会介绍如何提取BGA到DIE的寄生参数,如下图所示:

我们会用pRLCG求解器来提取下图虚线出的寄生参数,从BGA->routing->Bond Wire。

Step1 设置材料,频率范围和边界条件

所有的材料无论金属还是介质都需要设置成Normal,并设置相应的电导率,如下图所示:

本例中我们仿真到100MHz,如下图所示:

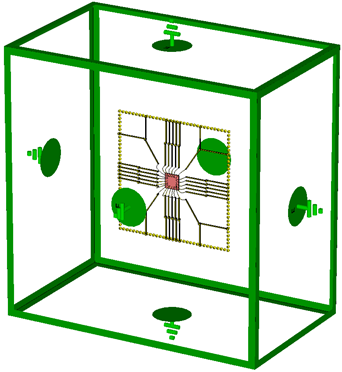

边界条件目前支持电壁和磁壁两种。如果没有设置RLC Ground的情况下,电壁上的电势为零,而磁壁则代表平均电势为零。如果设置了RLC Ground,则RLC Ground的电势为0。边界条件的大小以及类型都会影响到仿真结果,所以需要特别搞清需要的物理含义和状态。本例中的边界如下图所示:

Step2 设置Node

这一步相当于设置端口,本例中我们想要了解每一段走线的寄生参数,可以沿着走线设置多个Node。

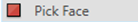

首先,先设置GNDNode,通过Pick Face选中参考地的面并设置为RLC Ground,这里的地必须是PEC。

接着设置Rounting和Bondwire上的Node,选中一个面,再选择RLC Node,如下图所示:

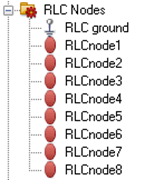

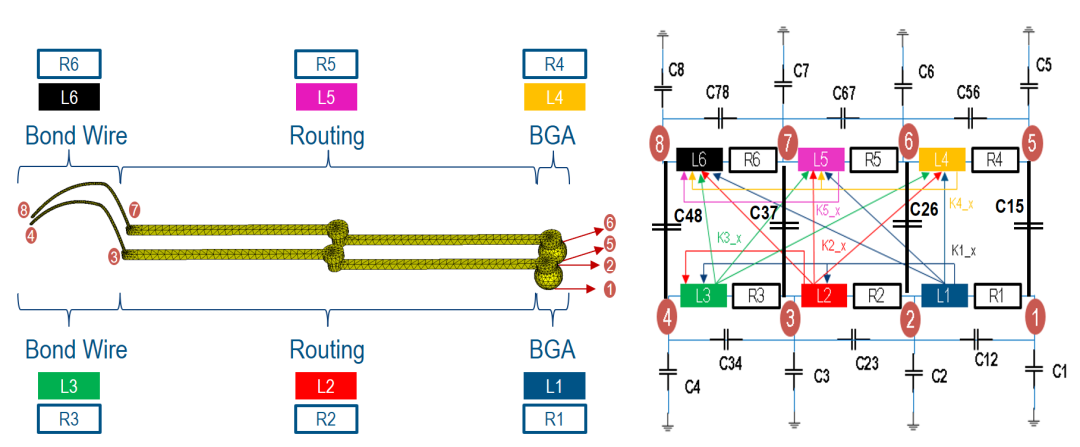

这样如下图,设置了8个Node,1#是BGA的进口,2#是Rounting线的入口,3#是Bondwire的入口,4#是到达Die的位置,5#到8#也是同样的情况,如下图所示:

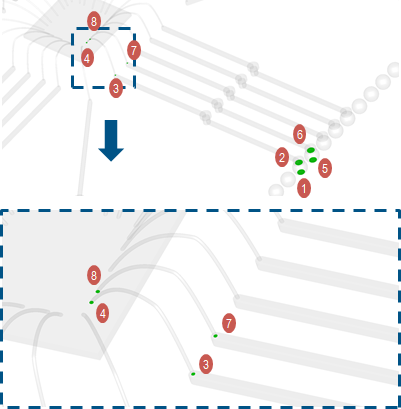

这样,最终的Nodes如下图所示:

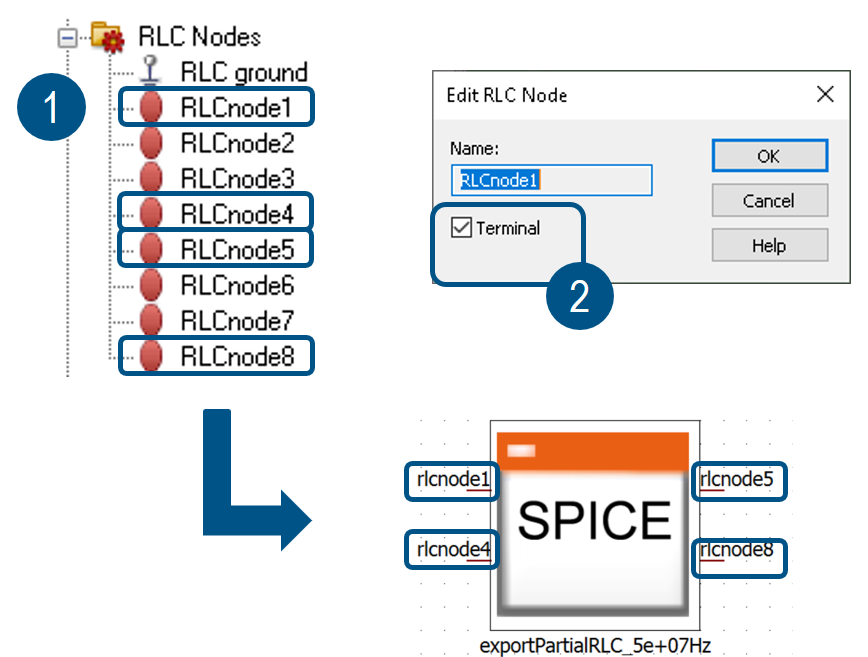

比如这里有两条平行的线,通过设置多个Node可以就可以分开计算并得到独立的RLCG寄生参数,比如走线本身的自感,电阻。平行走线之间的电容,走线和走线之间的互感和互容等,但实际的Spice模型我们只需要1#4#5#8#,四个对外的引脚,我们可以仅仅对那四个Node设置terminal,如下图所示:

Step3 设置求解器开始仿真

这里我们把那些Node都创建成一对对的Pair,总共这里是6对,并勾选上计算宽带以及寄生电容,选择需要生成Spice模型的频率,本例中设置了一个50MHz的点,如下图所示:

RLCG生成的Spice都是单独频点的结果,这里我们可以在分号后加若干个频点,会生成多个Spice文件。如果要得到宽带的Spice需要用S参数加Idem工具进行转换,见仿真实例006:用IDEMWORK提取宽带宏模型(上)仿真实例007:用IDEMWORK提取宽带宏模型(下)。

Step4 仿真结果分析

仿真完成后会得到几组RLC的结果如下图所示:

我们可以根据下图来分析一下这些结果的拓扑和含义。

本例中设置了6对pairs,那些pairs分别都有自身的电阻R1-R6和电感L1-L6,同时每个节点都有电容值C11-C88,这里的电容是8个节点对于电势为0处的结果。同时还有金属对之间的互容。这在本例中生成的50MHz的Spice模型中都反应了出来,如下图:

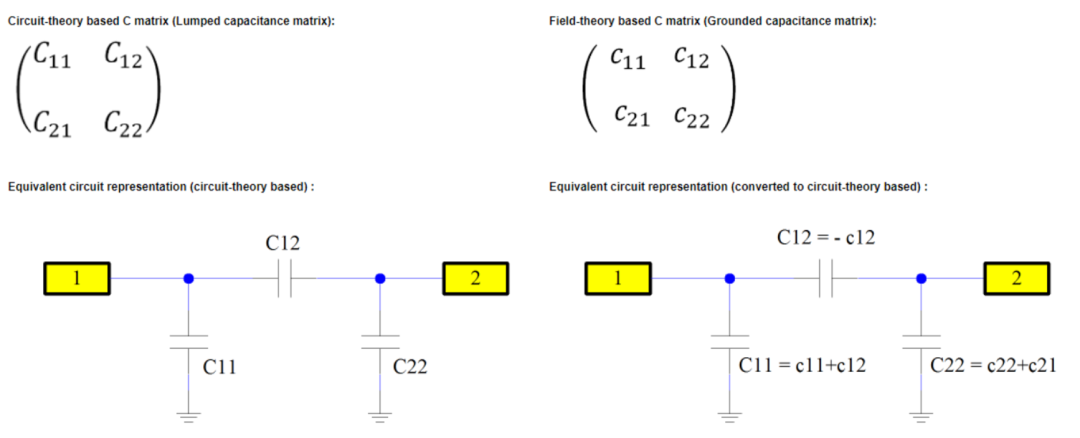

对于这里提供的节点电容补充一句,如果要计算整个线的对地电容,则需要把C1,C2,C3,C4加起来。而要计算两条线之间的电容则是需要把C48,C37,C26, C16以及更多的交叉电容都加起来。更多可参考CST帮助文档对于电容矩阵的解释,如下图:

上面两段看不懂也没关系,自动生成的Spice文件是包含了拓扑结构里的所有寄生信息了,直接用即可。

当然如果不设置Pairs,CST的pRLC求解器也可以直接得到自容和互容而不是上图中的节点电容。