CST PCB工作室基于2DTL模型的差分带状线设计与仿真实例

为了分析PCB上某个结构的电气特性,让用户对CST PCB工作室有更深入的了解。本文将介绍CST PCB工作室基于2DTL模型的差分带状线设计与仿真。

通过这个案例中,你将了解到:

1、CST PCB工作室建模设置;

2、2DTL求解器生成微带差分线的等效电路;

3、设置一个瞬态任务求解微带差分线的电气特性。

1. 建模设置

我们创建一个新的PCB 项目,并将其保存为"Differential Striplines"(相同名称的完整示例也可以从Component Library中获取) 。

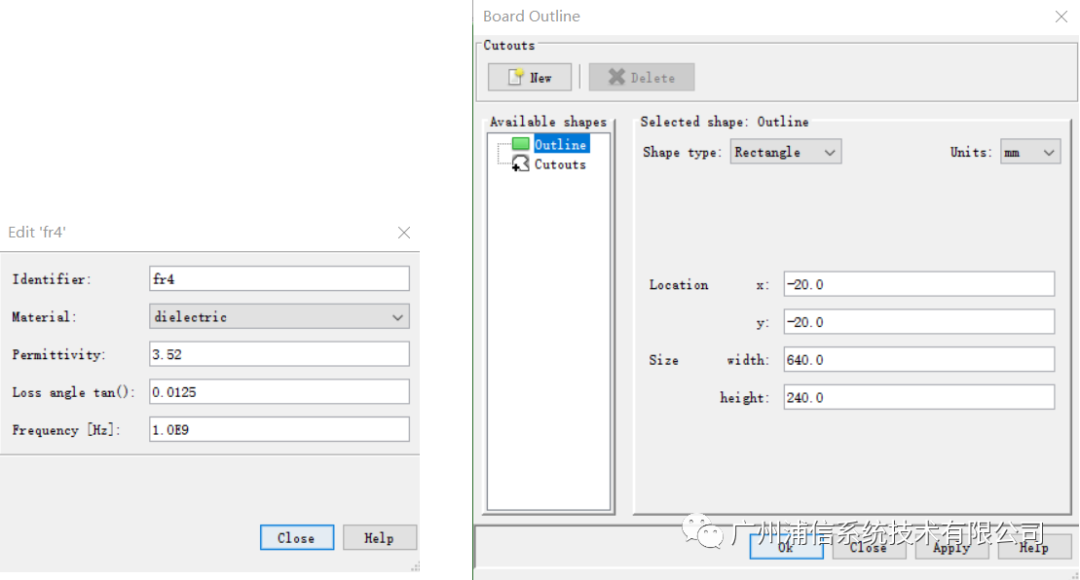

1.1 设置材料&PCB边框

在第一步中,我们进入导航树,展开"materials"文件夹调整材质"fr4"的默认值;点击"Board"文件夹设置PCB边框属性,如下图所示:

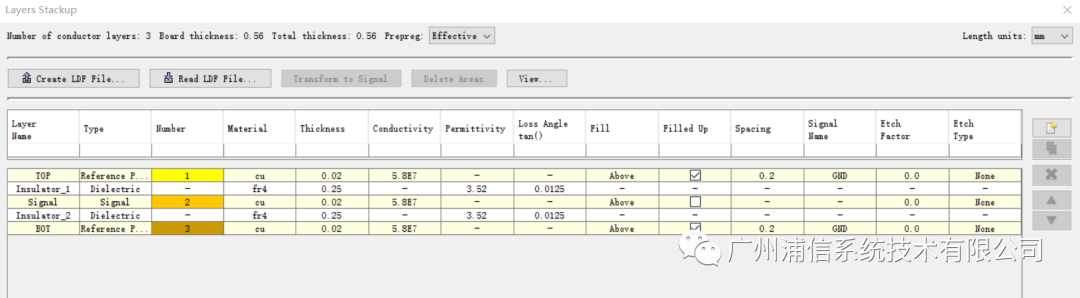

1.2 设置Layers Stackup

接下来,我们通过Home: Layout d Stackup打开叠层结构编辑器。在第一步,我们添加一层额外的绝缘层(Dielectric)和信号层(Signal)。然后将TOP和BOT层的图层类型更改为“Reference Plane”,并将两个参考平面标记为“fill Up”,软件将自动用金属填充整个层。按F5来更新主视图。完成这些步骤后,叠层应该如下图所示:

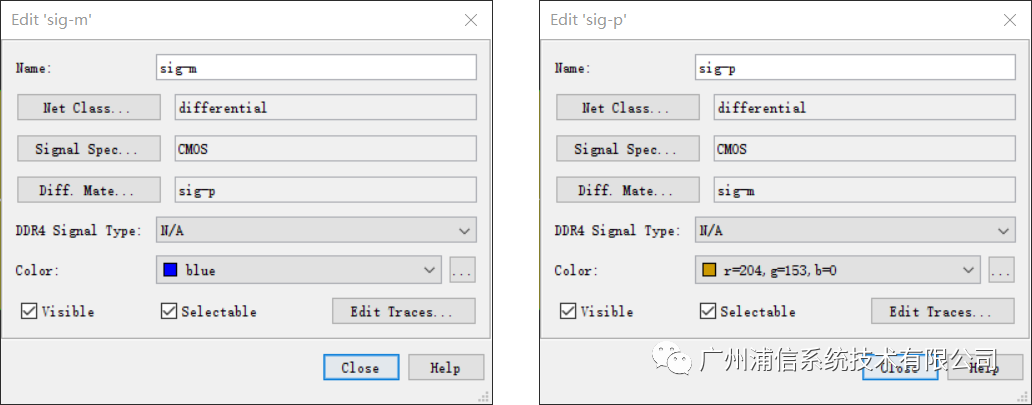

1.3 设置Net Editor

然后我们通过Edit: New Object d Net新建网络,生成如下图所示的两个网络:

通过Home: Layout dNet Editor 将两个网络“sig-p”和“sig-m”声明为相应的差分信号线:

1.4 绘制Trace

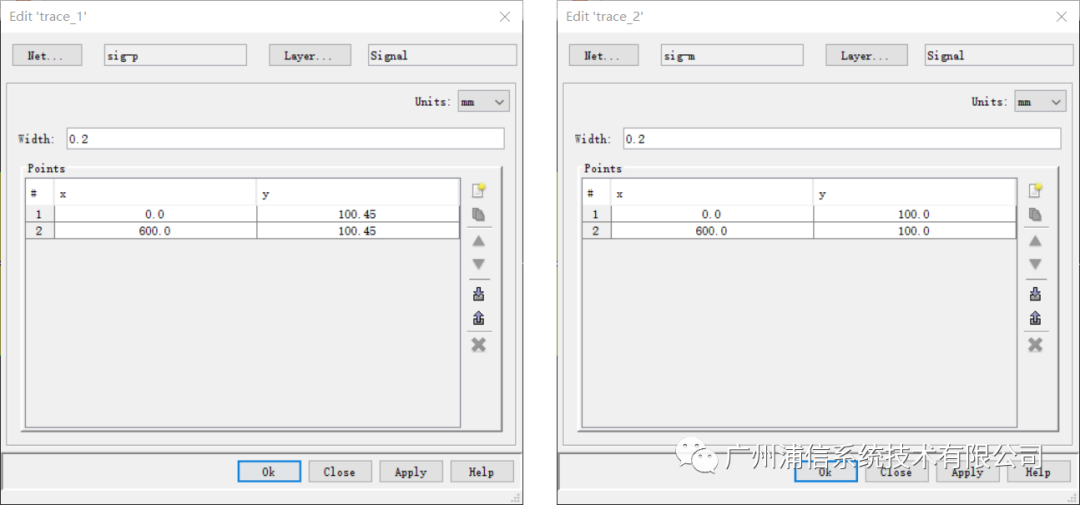

接着,我们可以绘制平行走线。通过Edit: New Object dTrace进入新建走线设置窗口(按ESC键),参考下图设置,创建的走线将是net:sig-p的一部分;第二个走线的设置与第一个走线的设置类似;

1.5 定义Terminal

现在,我们需要在两条走线的两端都放置一个终端。因此,我们通过Edit: New Object d Terminal(按ESC键)打开终端编辑对话框。我们添加的四个终端,这些终端将在后面2DTL求解器生成微带差分线的等效电路时,会产生相应的pin脚,终端值如下所示:

T1: Layer Signal, Net sig-p, x=0mm, y=100.45mm

T2: Layer Signal, Net sig-p, x=600mm, y=100.45mm

T3: Layer Signal, Net sig-m, x=0mm, y=100mm

T4: Layer Signal, Net sig-m, x=600mm, y=100mm

最后,如果你放大布局,应该如下图所示:

2.2DTL求解器生成微带差分线的等效电路;

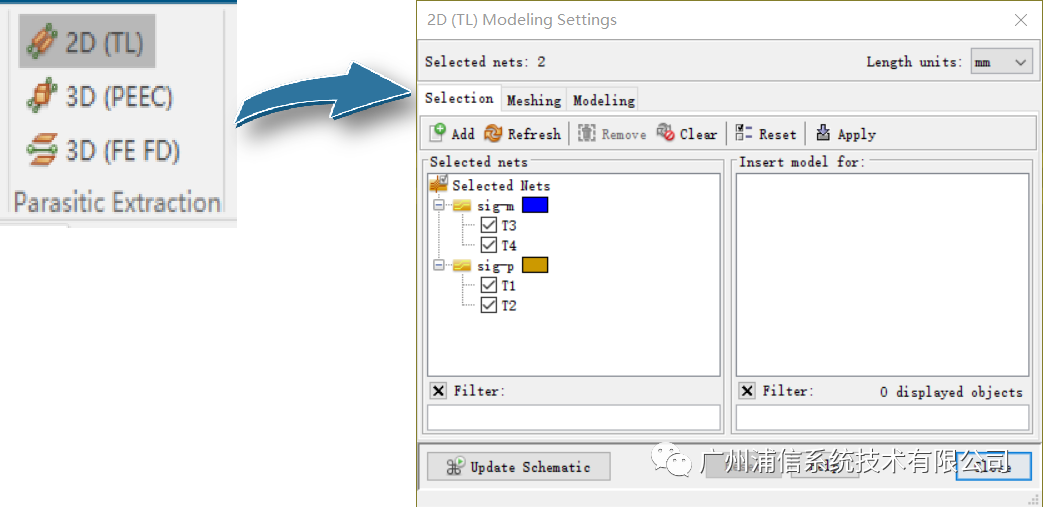

现在我们可以生成微带差分线的等效电路。首先,进入导航树,选择网络“sig-p”和“sig-m”。通过按Home: Parasitic Extraction d2D (TL)打开2D (TL)对话框。选择Selection选项栏,通过按“add”或从导航树中拖动所选项目,将这两个网添加到selected nets列表中,如下图所示:

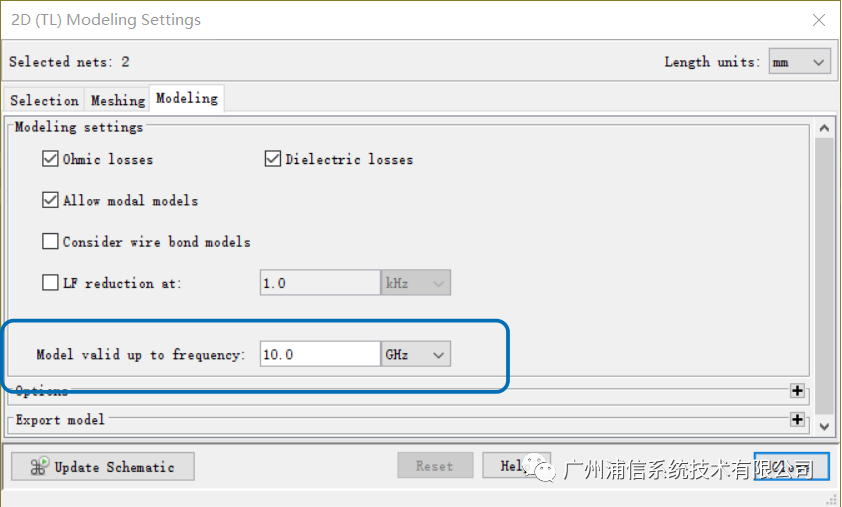

接下来我们切换到Modeling选项卡,将参数“Model valid up to frequency”设置为10GHz,如下图所示。其他设置都保持默认值(2DTL Modeling窗口的更多设置,用户可以点击相应窗口的“Help”按钮获取相关帮助文档,我们公众号也会在后面的文章中对相关设置做更详细介绍)。

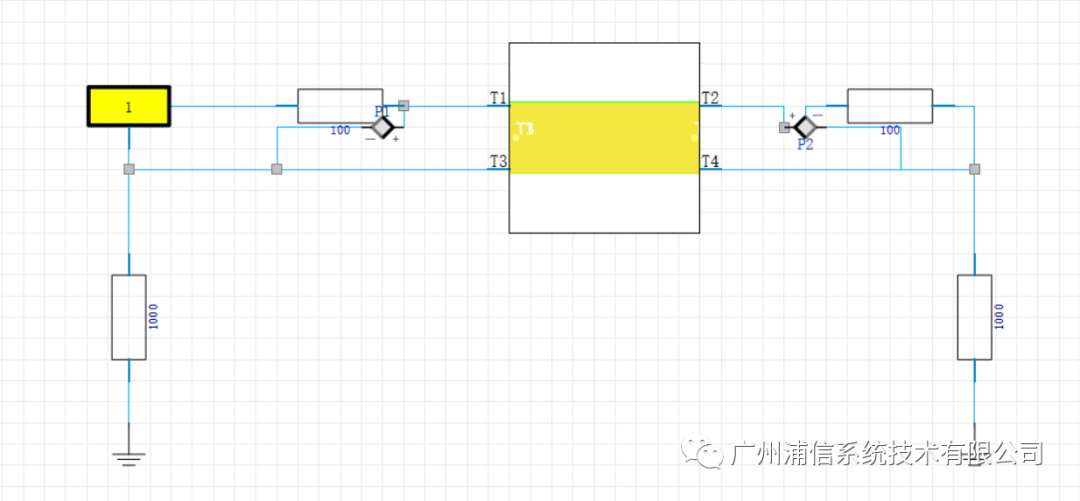

现在,按下Start按钮,在主窗口中,点击Schematic选项栏将窗口切换到CST设计工作室界面,我们可以看到带状差分线生成的原理图符号,按照下图的原理图加载器件。

其中,P1和P2为差分端口,测量t1 ~ t3和t2 ~ t4之间的电压。

3.设置一个瞬态任务

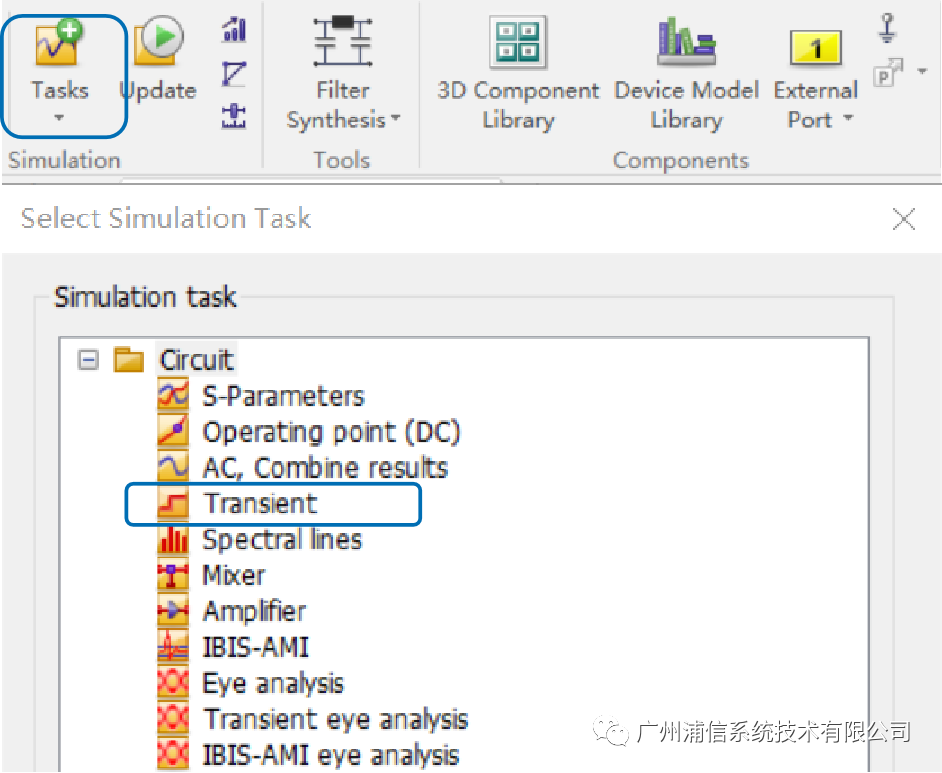

在CST设计工作室界面中,点击“New Task”,在弹出来的窗口中,选择“Transient”,如下图所示:

在对应的“Task”参数列表中我们选择“Excitations”选项栏,然后选择“Define Excitation”,一个新的对话框将允许我们定义激励,如下图所示:

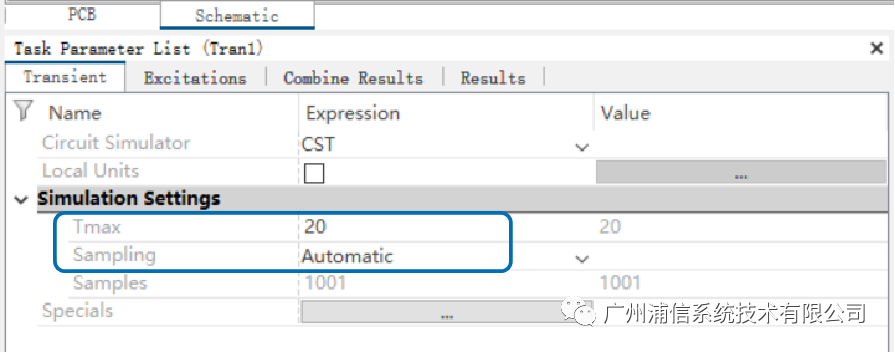

之后,我们切换到“Transient”选项栏,并将最大模拟时间更改为20ns:

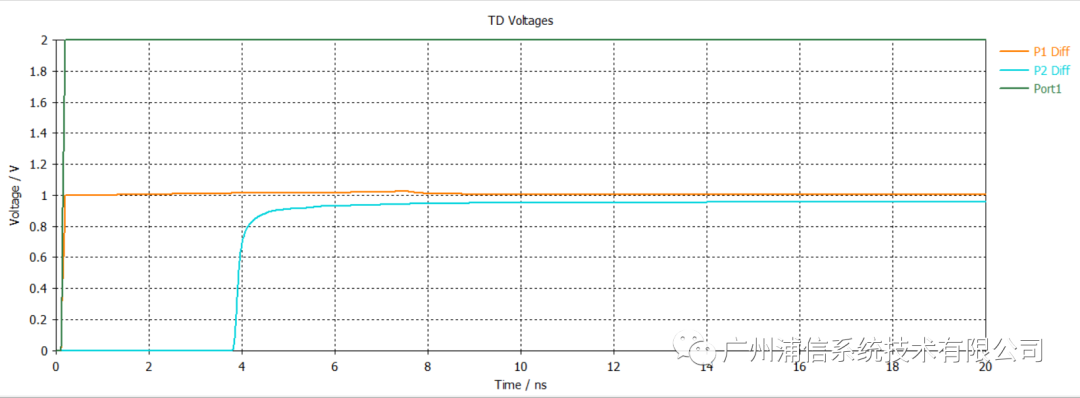

最后,按下Update图标以启动仿真。下图是仿真的结果。

可以看到,信号通过差分线大约有4ns的延迟时间,由于一些信号反射,P1端的电压略高于P2端。