电路仿真如何使用Block子电路建模功能

CST Design Studio Project Block

场路协同仿真在CST中是一个常见的应用。当电路比较复杂,元器件较多时,估计每个用户都会觉得眼花缭乱。下面介绍一个小功能,通过一个block来代表一个子电路,从而使电路界面更简洁,使电路拓扑一目了然。尤其当使用大量重复的子电路时,该功能更是让能够大量节省电路建模时间。

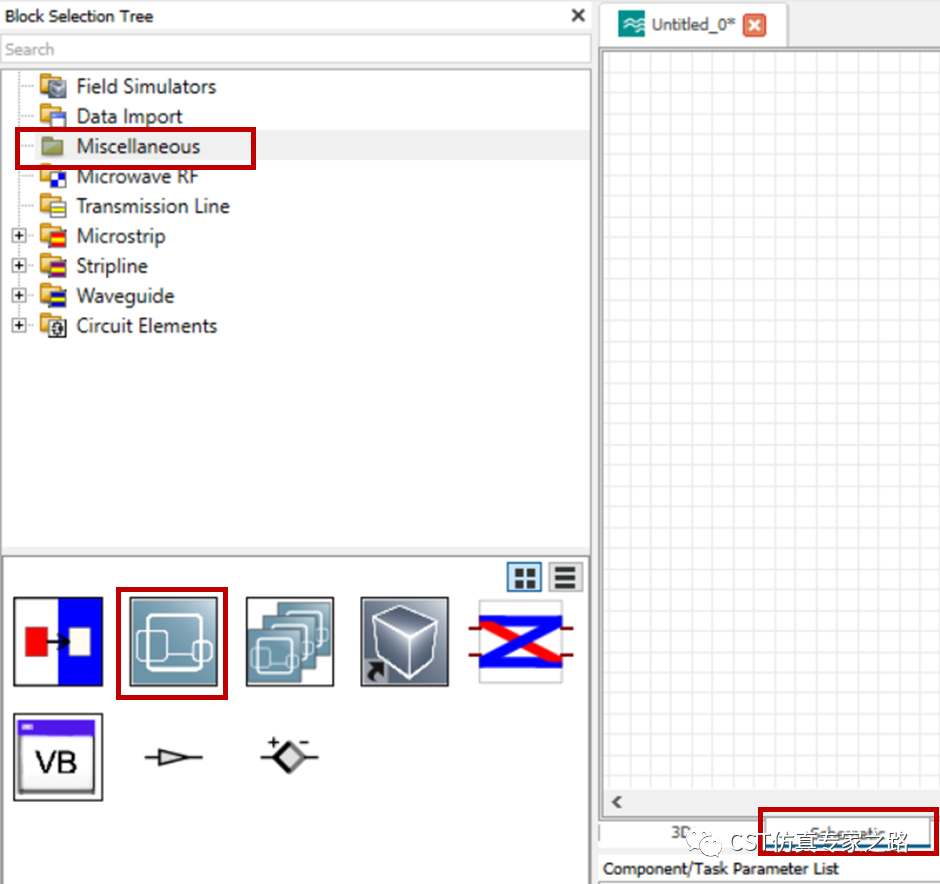

CST Design Studio Project Block如下图所示

1.把该block拖入到电路界面中,此时block没有pin脚,会在schematic选项卡旁边弹出一个新的选项卡,名字是DESPARA1。我们将Schematic作为主电路,将DESPARA1作为子电路。

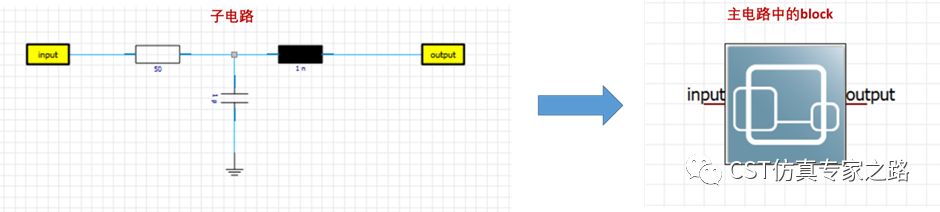

2.在DESPARA1中的创建子电路,子电路对外的pin用external port表示,同时可以修改port的名字。也就是在子电路(DESPARA1)中有几个External port,在主电路(Schematic)中的CST Design Studio Project Block中就有几个pin,如下图所示

3.此时就可以在主电路中进行仿真了。需要提醒的是,在主电路仍然需要增加External port,而子电路中的port只是子电路与主电路之间的接口。

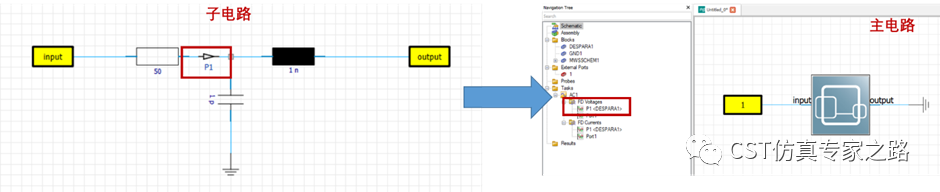

4.在子电路中可以添加probe,通过这种方法,可以查看子电路内部的电压电流波形。添加probe后,当主电路完成仿真后,会出现后缀类似(DESPARA1)的probe的仿真结果,这就是子电路上监测到的电压/电流波形。如下图所示

5.此外子电路中也可以添加CST Design Studio Project Block。子电路的block可以理解成下一层的子电路。

总结:CST有很多小功能能够助力仿真效率提升,我们一起用,一起飞。