某产品ESD静电放电设计与整改案例

1. 问题描述

某工业显示屏在进行ESD静电放电测试时,对网口、USB、串口打±6kV接触放电,每次试验系统液晶屏出现蓝屏现象,系统死机,重新上电后可以恢复,实验不通过。

本问题已经历经半年,期间客户公司内部以及方案公司进行过V1.0-V1.31共4次改板,投入了大量人力物力仍未解决,时间刻不容缓。

2. 故障诊断

考虑到本板历次分别从接地、滤波、隔离等方面对单板进行了设计整改,均未改善,怀疑单板有ESD薄弱点,因此本次确定采用敏感源头诊断和整改的方案,从源头彻底解决问题。

根据实验现象分析,判断为CPU功能单元受到干扰,分析核心子板(CPU模块电路)管脚各信号,从实践经验、信号功能等角度分析,判断表1罗列的信号比较敏感,易受静电干扰。

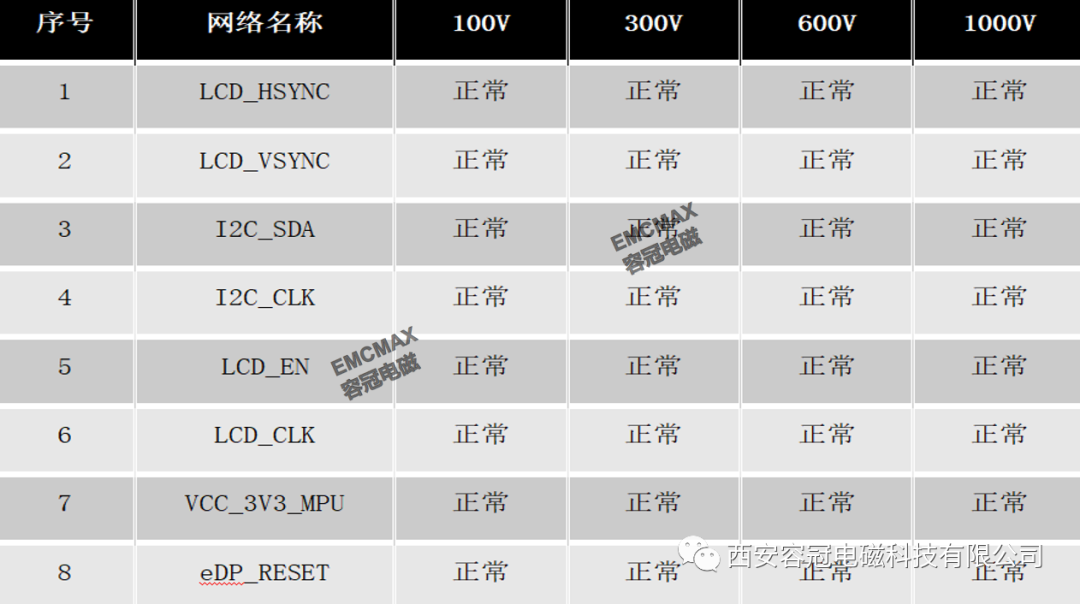

表1 易受ESD干扰的敏感信号

将ESD静电枪电压分别调至100V、300V、600V和1000V,分别对核心子板表1所示的信号管脚做接触放电,查找ESD敏感信号,如图1所示。

图2 接触打IC管脚

实验中问题没有复现,因此排除这些信号产生的问题,试验记录如表2所示。

表2 ESD敏感信号验证结果

继续分析核心子板上敏感电路,当对敏感信号DDR_CLK 100V接触放电时问题复现,且每次放电问题都可以复现。

DDR_CLK布线4mil,且布线未预留焊盘,整改手段有限,为了确定静电辐射电磁场对DDR_CLK时钟信号有无影响,则使用1根金属接地线,放在DDR_CLK线正上方,用静电枪打接地线铜鼻子,如图3所示。

图3 接触打接地线铜鼻子

按图3所示的方法,6KV接触放电时,5次放电问题都能复现,因此确认静电电磁场辐射对DDR_CLK信号和DDR器件有影响,此时使用铜箔将核心板区域屏蔽并接地,保护DDR敏感信号和模块,如图4所示。

图4 核心板模块屏蔽

将核心板模块区域屏蔽后,对I/O接口进行接触放电正负6KV、8KV、10KV,每次连续40次放电,系统均运行正常,问题解决,因此确定为核心板受静电干扰导致整机死机。

3. 原因分析

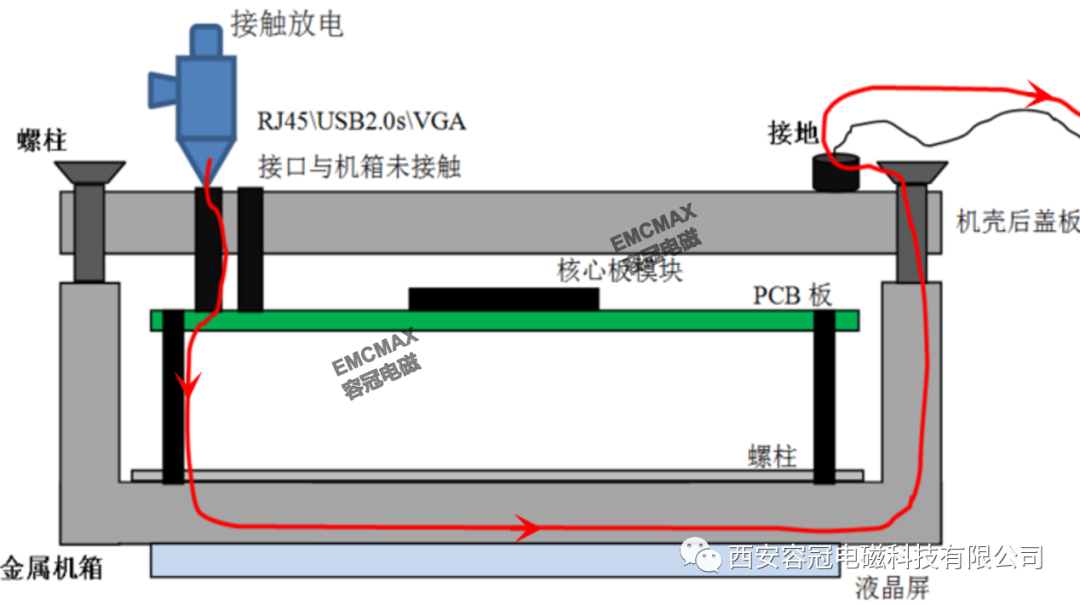

继续验证确定整机ESD为辐射耦合or容性耦合,经分析,系统静电放电泄放途径为I/O接口——单板PGND——金属衬板——金属机箱——机箱盖板——接地线,如图5所示。

图5 整机静电泄放途径

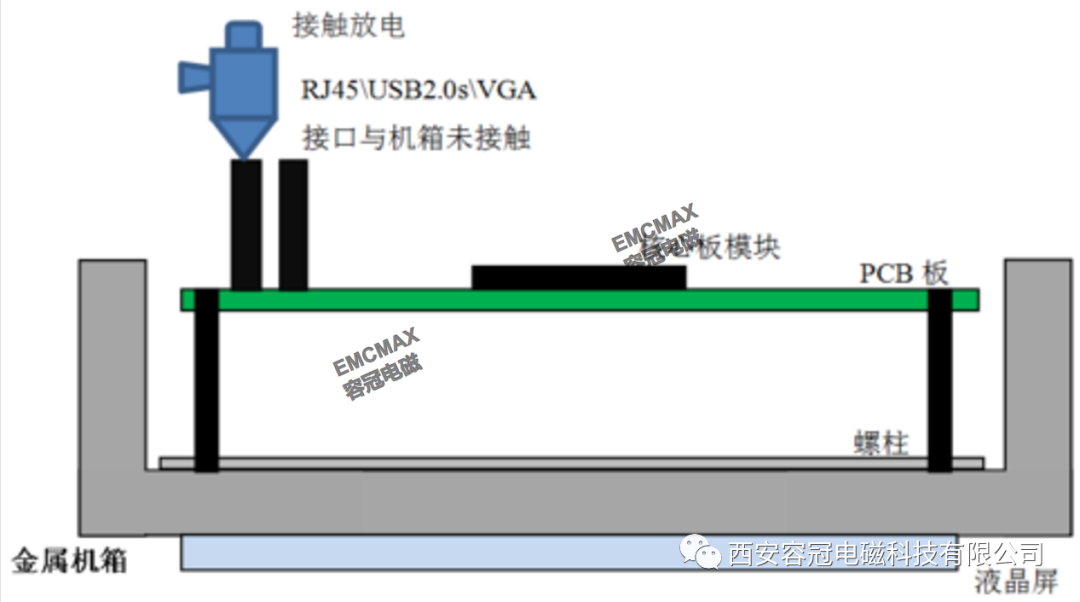

当将机箱盖板与金属机箱不拧螺丝时或者机箱盖板不盖时,发现此时静电放电无问题,因此排除辐射耦合,那么此时静电泄放途径为I/O接口——单板PGND——金属衬板——金属机箱,则相当于核心板DDR敏感部位与机箱盖板无静电容性耦合(两者距离很近),如图6所示。

图6 去掉后盖整机静电泄放途径

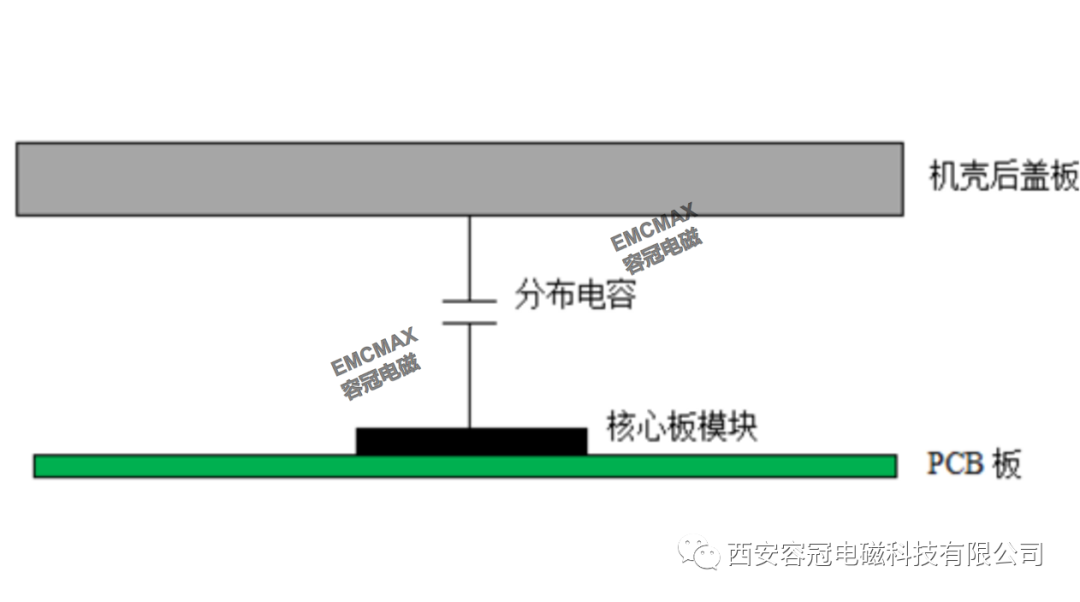

综上整机核心子板静电耦合简易模型如图7所示。

图7 核心子板静电耦合模型

诊断时核心子板加屏蔽罩后此时静电耦合模型如图8所示。

图8 核心子板静电耦合模型

从图8可以看出,核心子板加屏蔽罩后,机箱后盖板静电能量直接耦合到金属屏罩并通过屏蔽罩接地引脚到GND,从而避免ESD直接耦合到敏感的DDR模块,问题得以解决。因此根据以上分析,为机箱后盖板静电干扰容性耦合至DDR模块电路导致ESD问题。

4. 整改措施

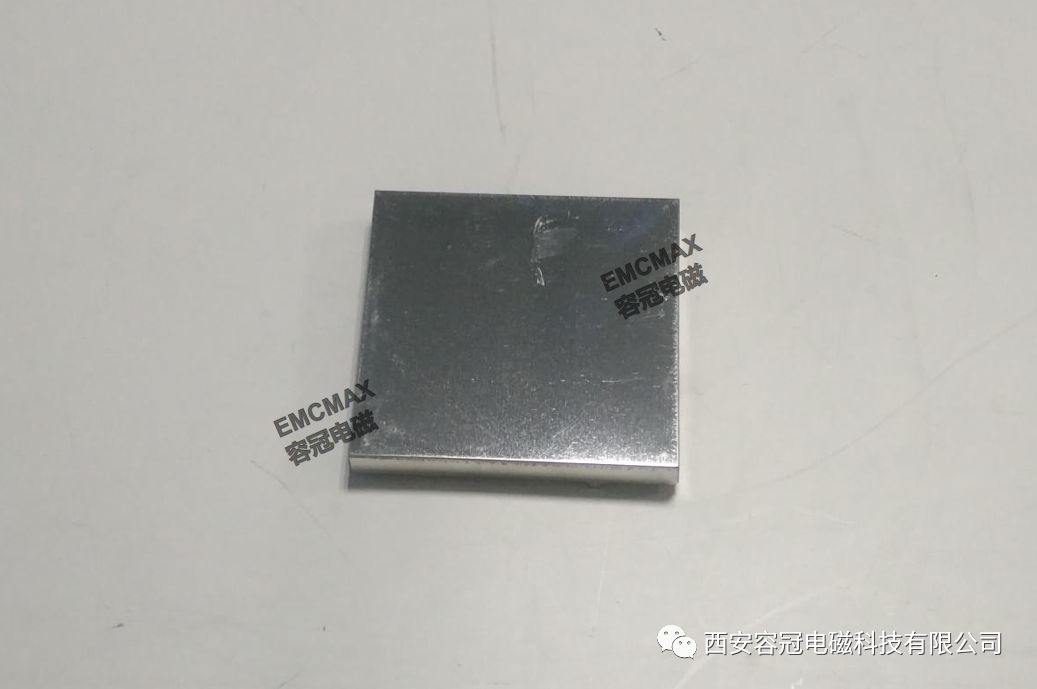

因核心子板是客户公司平台化产品,模块上DDR电路又及其敏感,推荐主板采用屏蔽罩屏蔽敏感核心子板模块的方案量产,本方案简单易行,成本增加不到0.5元,效果可靠。最后经与客户沟通,目前主板上空间充足,本方案可生产,屏蔽罩如图9所示。

图9 核心板屏蔽罩

5. 实践效果

改板后再次进行静电试验,此后系统死机问题再未复现,试验通过。

【点评/点睛】

ESD实验时,工程师经常碰到打一枪就死,整改来整改去没用,即便做了无数次PCB改板,也徒劳无功,搞得怀疑人生,自嘲下此刻想死的心都有了!何故?因为电路中有对ESD极其敏感的薄弱点,不攻要害,何来征服!本案例产品ESD问题,经过缜密的诊断和分析确定出了敏感源和耦合途径,然后通过对敏感源屏蔽成功化解。本文的整改方法和思路启示我们,打蛇打七寸,擒贼要擒王,不出手则已,出手则要直击要害,一战定乾坤。