时钟信号调试系列(一)晶振时钟信号辐射问题调试与设计

绝大部分芯片都需要使用外部晶振提供时钟信号,晶振电路的设计不仅仅影响电气性能指标,同时也会影响电磁兼容性能指标,在原理图设计阶段、PCB设计阶段应重点关注。

晶振分为有源晶振和无源晶振两种,无源晶振输出的时钟信号是正弦波,而有源晶振输出的时钟信号是方波,方波具有丰富的高次谐波噪声,是导致辐射发射超标的重要因素之一,而理想的正弦波几乎不存在高次谐波,辐射发射测试相对比较容易通过。

01、无源晶振EMC问题分析调试与设计

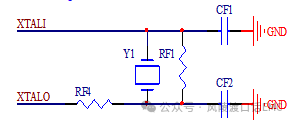

无源晶振的电路设计通常如下图所示,CF1、CF2电容是晶振负载电容,影响晶振时钟频率的偏差,RF1电阻的主要作用是防止晶振停振用的,部分晶振电路没有这个电阻,RF4电阻主要是用于晶振的输出幅度调节。

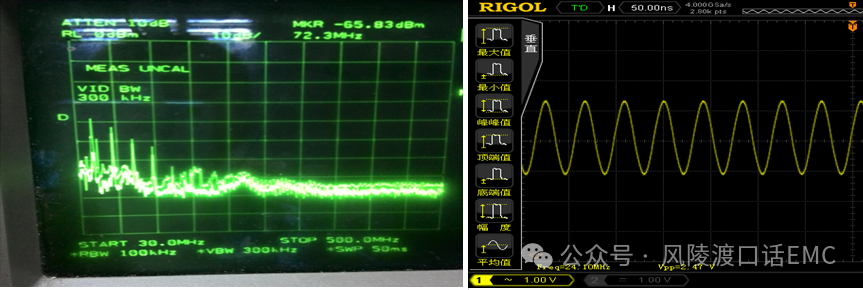

晶振输出时钟信号的波形可以通过示波器量测,频谱可以通过频谱分析仪测量。无源晶振输出幅度范围1.25V~2.5V之间,当输出幅度过大就会产生过幅失真,产生丰富的高次谐波,具体案例如下图所示:

(晶振时钟高次谐波频谱) (晶振时钟信号波形畸变)

针对晶振输出时钟信号的波形失真导致的丰富高次谐波,可以在晶振输出引脚增加串联电阻进行限幅,串联电阻参数应根据实际量测波形进行调整,选择恰当的参数,通过电阻限幅后的波形与频谱如下图所示:

(限幅后晶振时钟高次谐波频谱) (限幅后晶振时钟信号波形)

无源晶振输出时钟信号波形越接近正弦波,高次谐波就越少,实际电路应用中没有理想的正弦波,晶振输出时钟信号是存在高次谐波。

02、有源晶振EMC问题分析调试与设计

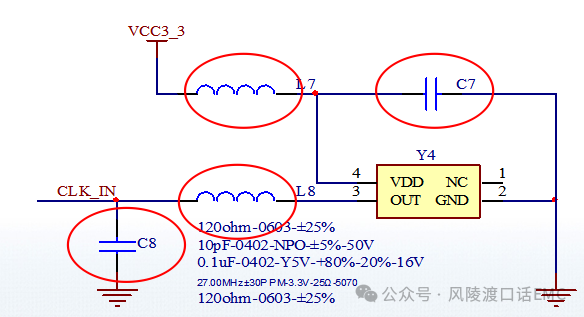

有源晶振电路设计通常如下图所示,C7、L7组成LC滤波器,目的滤除有源晶振供电电源引脚耦合的时钟噪声;L8、C8组成LC滤波器,目的滤除有源晶振输出时钟的高次谐波噪声,考虑到磁珠会产生过冲,有源晶振输出时钟信号的滤波器采用RCL滤波电路

对于有源晶振的波形可以通过示波器量测是否存在过冲、振铃、信号幅度设置是否过大等情况,有源晶振波形如下图所示:

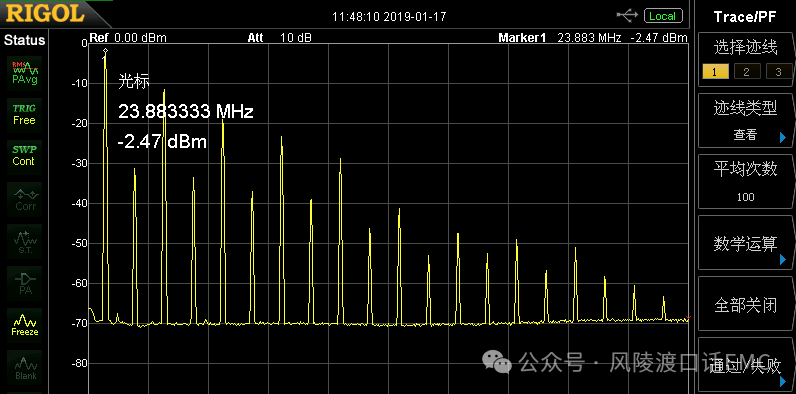

有源晶振的频谱可以通过频谱分析仪测量,根据方波的特性必然存在丰富的高次谐波,在不影响有用时钟信号质量的前提下,可以增加低通滤波器滤除高次谐波噪声干扰,有源晶振输出时钟信号频谱如下图所示:

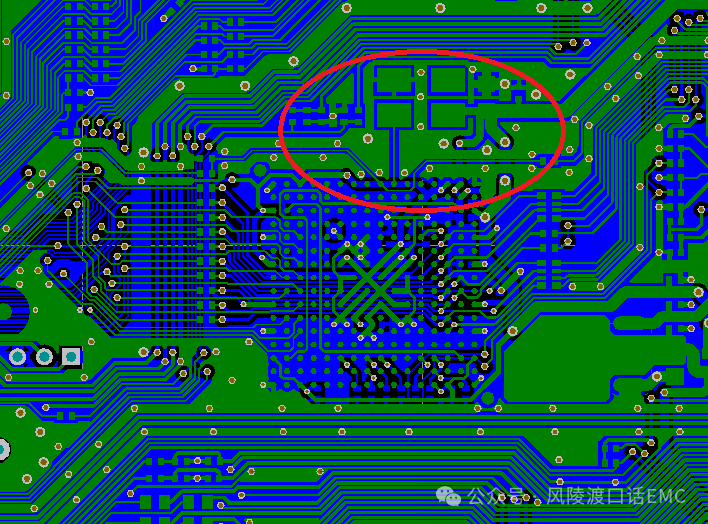

03、关于晶振PCB Layout设计要点说明

关于有源晶振PCB Layout的注意事项,是将有源晶振供电电源滤波器件,靠近有源晶振供电电源引脚放置,输出时钟信号滤波器件也同样靠近晶振时钟引脚。

PCB Layout的注意事项主要有:

一是、时钟信号两侧需要包地,或者采用邻层完整的平面做参考。

二是、时钟信号需要做阻抗控制。

三是、时钟信号的回流参考平面保持完整,避免跨分割。

四是、有源晶振本体靠近芯片引脚,缩短时钟信号布线长度。