GPIO信号介绍

一、GPIO信号基础知识

GPIO(General-Purpose input/output),通用型之输入输出端口的简称,可以通过软件控制其输出和输入,市面上绝大部分芯片都会提供一个"通用可编程IO接口",即GPIO。

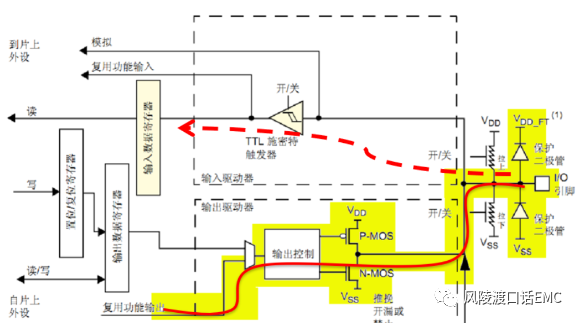

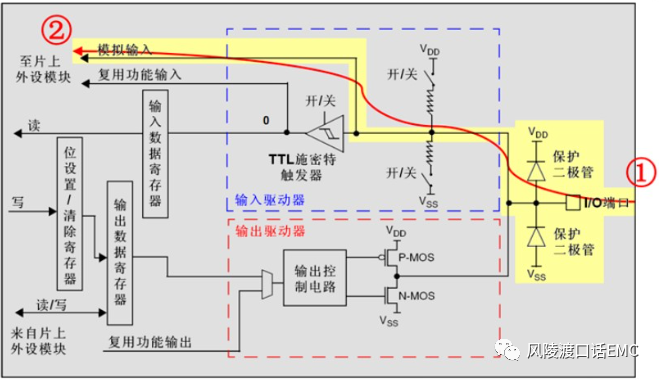

GPIO信号原理框图

目前市面上使用的芯片,其内部GPIO信号电路结构都如上图所示,其输入保护二极管用于防止引脚外部过高正电压、负电压输入,当电压高于VDD时,上方的二极管导通,当引脚电压低于VSS时,下方二极管导通,防止外部脉冲电压引入损毁芯片。

TTL施密特触发器:基本原理是当输入电压高于正向阈值电压,输出未高;当输入电压低于负向阈值电压,输出为低。IO口信号经过触发器后模拟信号转化为0和1的数字信号,也就是高低电平,并且符合TTL电平协议。

P-MOS管和N-MOS管:信号由P-MOS管和N-MOS管,依据两个MOS管的工作方式,使得GPIO具有"推挽输出"和"开漏输出模式",P-MOS管高电平导通,低电平关闭;N-MOS管低电平导通,高电平关闭。

二、GPIO信号的8种模式:

状态 | 类型 | 特征 |

浮空输入 | 数字输入 | 可读取引脚电平,若引脚悬空,则电平不稳定 |

上拉输入 | 数字输入 | 可读取引脚电平,内部上拉,悬空默认高电平 |

下拉输入 | 数字输入 | 可读取引脚电平,内部下拉,悬空默认低电平 |

模拟输入 | 模拟输入 | GPIO无效,引脚直接接入内部ADC |

开漏输出 | 数字输出 | 可输出引脚电平,高电平为高阻态,低电平接VSS |

推挽输出 | 数字输出 | 可输出引脚电平,高电平接VDD,低电平接VSS |

复用开漏输出 | 数字输出 | 由外部控制,高电平为高阻态,低电平接VSS |

复用推挽输出 | 数字输出 | 由外部控制,高电平接VDD,低电平接VSS |

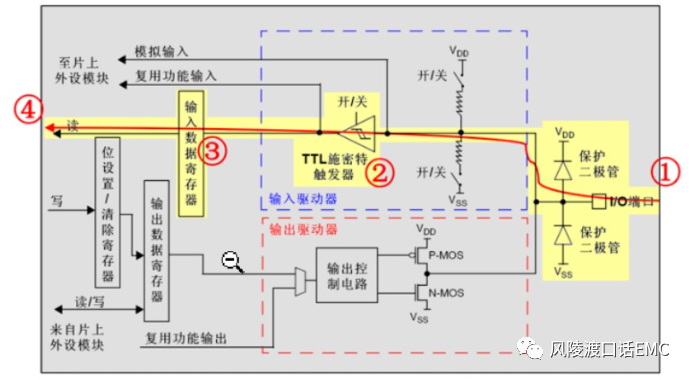

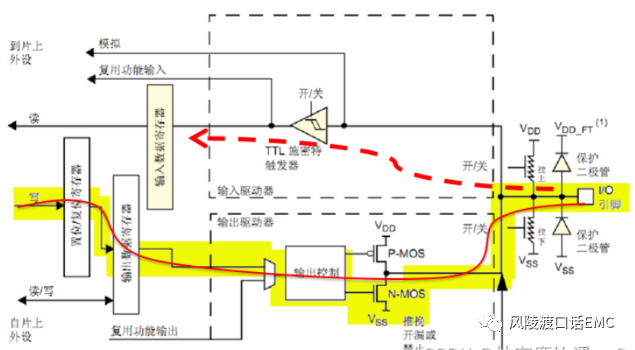

2.1、浮空输入:

浮空输入模式下,I/O端口的电平信号直接进入输入数据存储器。I/O电平状态是不确定的,完全由外部输入决定;如果在该引脚悬空(无信号输入)的情况下,读取该端口的电平是不确定的,通常用于IIC、UART等总线设备。

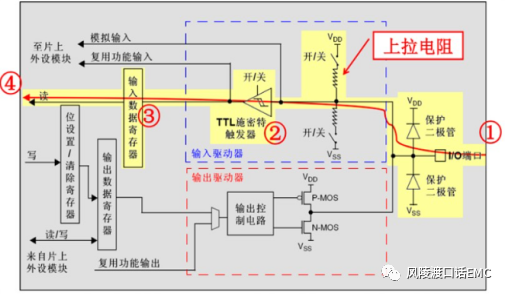

2.2、上拉输入模式:

上拉输入模式下,I/O端口的电平信号直接进入输入数据存储器。但是在I/O端口悬空(在无信号输入)的情况下,输入端的电平保持在高电平(并且在I/O端口输入为低电平的时候,输入端的电平也是低电平)

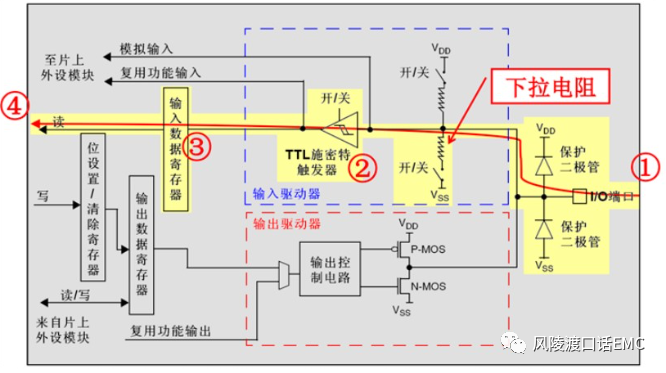

2.3、下拉输入模式:

下拉输入模式下,I/O端口的电平信号直接进入输入数据存储器。但是在I/O端口悬空(在无信号输入)的情况下,输入端的电平保持在低电平(并且在I/O端口输入为高电平的时候,输入端的电平也是高电平)

2.4、模拟输入模式:

模拟输入模式下,I/O端口的模拟信号(电压信号,而非电平信号)直接模拟输入到片上外设模块,比如ADC模块电路。

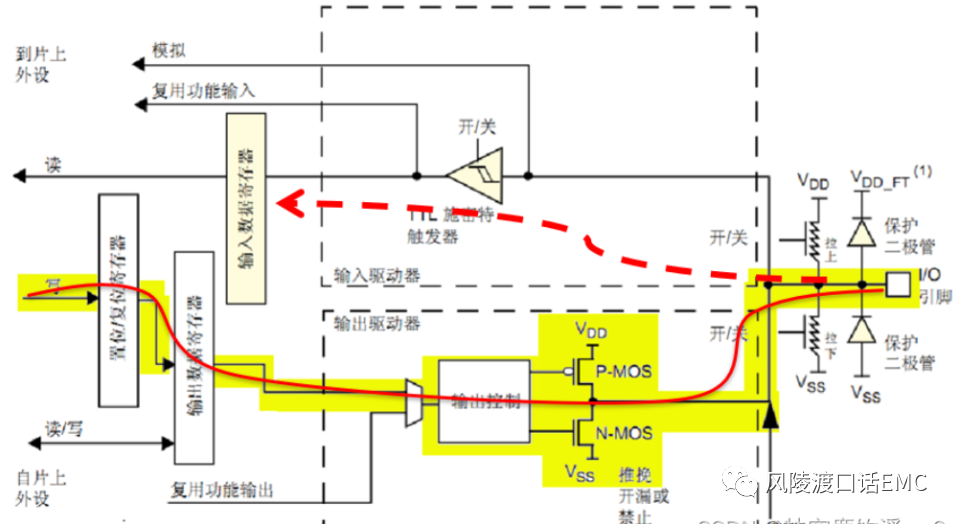

2.5、开漏输出模式:

在开漏输出模式时,只有N-MOS管工作,如果控制输出为低电平,则P-MOS管关闭,N-MOS管导通,使输出为低电平;若控制输出为高电平,则P-MOS管和N-MOS管都关闭,输出指令就不会起作用,此时I/O端口的电平由外部的上拉或者下拉决定,如果没有上拉或者下拉I/O口就处于悬空状态。

2.6、推挽输出模式:

在推挽输出模式时,N-MOS管、P-MOS管都工作,如果控制输出为低电平,则P-MOS管关闭,N-MOS管导通,使输出为低电平;若控制输出为高电平,则N-MOS管关闭,N-MOS管导通,使输出为高电平,外部的上拉或者下拉的作用是控制在没有输出时I/O电平。

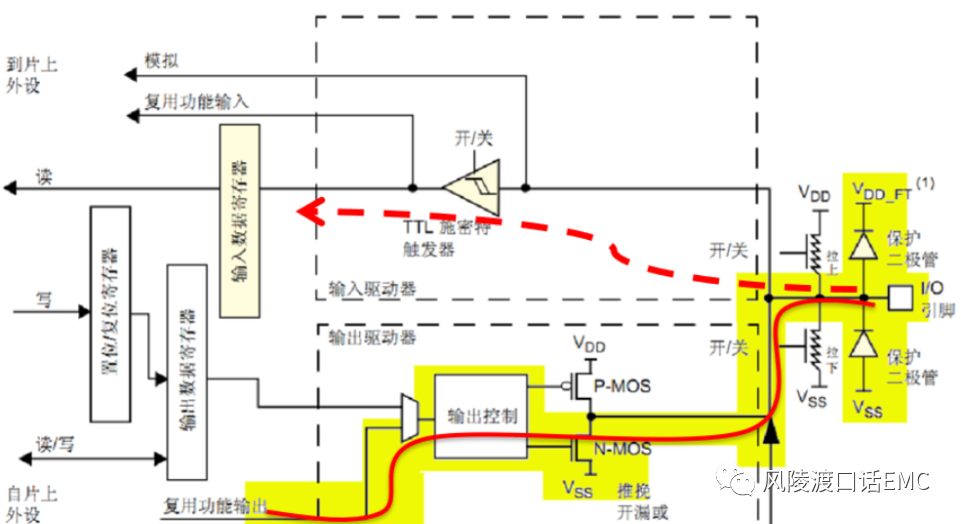

2.7、复用开漏输出模式:

GPIO复用为其它外设,输出数据寄存器无效;输出高低电平来源于其它外设,施密特触发器打开,输入可用,通过输入数据存储器可获取I/O实际状态,除了输出信号的来源改变其它与开漏输出功能相同。

2.8、复用推挽输出:

GPIO复用为其它外设,输出数据寄存器无效;输出高低电平来源于其它外设,施密特触发器打开,输入可用,通过输入数据存储器可获取I/O实际状态,除了输出信号的来源改变其它与推挽输出功能相同。