ADS下阻抗匹配后layout如何做出相应的修改?(附图)

在ADS的schematic已完成了较为理想的阻抗匹配(如下图)(感谢坛子里的兄弟的指导)

仿真结果

仿真结果

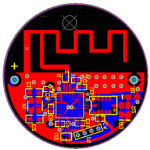

现在问题出在如何将优化的传输线绘入layout中?我自己尝试着做了一下,但效果非常不理想。(如下图)

仿真结果如下图

请各位达人予以指导,小弟在这里先谢过了。

我一般都是在LAYOUT里面匹配好以后再生成SCHEMATIC的。 SHEMATIC和LAYOUT存在差异是很正常的。

谢谢楼上的回复,不过在schematic下可以利用Goal对匹配时传输线长度自动进行优化,看过几个例子也时先在schematic下进行优化后在绘入layout的。

请问如何在layout下进行匹配?谢谢啦

我也遇到了同样问题。

楼上的兄弟解决了别忘告诉兄弟一声啊。苦苦等待中

我对微带线的匹配方式不是很熟悉(平行线基础不好),LAYOUT里的天线不匹配的话我就直接拿它的等效阻抗到SHEMATIC里用分离式元件匹配,所以也没用过SHEMATIC再导回LAYOUT的功能。不要笑话我啊。

谢谢楼上的分享。其实我刚接触微带天线不久,知道还没有楼上这位兄弟的多呢。是不要笑话我才对呢。

大家一起探讨,一起加油吧

我更菜啊!如何在layout中实现优化啊!我每次都是在SCHEMATIC中优化,然后导入layout中,发现有很大差别,可是就不会在layout中使用优化了!楼上的,以及楼上的楼上,楼上的楼上的楼上的兄弟,指导下啊!

Schematic里,端口、开路结和后面的电路三个部分是用点连接的,在Layout里则是重叠的,我习惯在Schematic里用MTEE三端口部件来连接3个部分,当然,MStep是没有尺寸的,而MTEE本身是有长度的,计算好3个端口宽度引入的长度变化再设定尺寸

另外我不知道Schematic里,11Ohm和接地的0.921pF电容串联电路,和Layout里10.09333mm后面的电路阻抗是不是一样的,如果不一样,那差别很大的。

希望对你有些帮助,

谢谢楼上这位朋友的帮助.

我个人感觉再在layout下进行匹配不仅仅是配线的长度问题可能还要受到实际的寄生电阻和电容的影响,所以经常就是layout下的匹配结果根schematic下的差得很多。

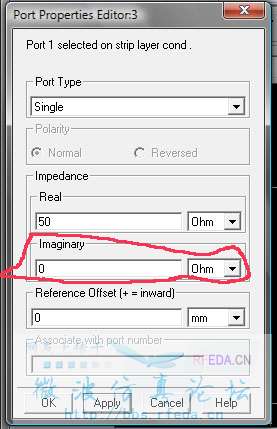

请问兄弟,在ADS中设计标签天线,由于芯片是复阻抗,因此天线阻抗要设计为芯片复阻抗的共轭,那么怎么设置天线的端口阻抗进行仿真呢?

我是用的是ADS 2005A,在此版本中,设置一个端口为参考地,一个端口为Internel,Internel端口的阻抗设置分为real 阻抗和Imaginary阻抗两部分,我曾经按照芯片阻抗和芯片阻抗共轭设置它,但是仿真结果是明显错误的,所以我不知道应该怎么设置了。

同求

相关文章:

- 天线阻抗匹配好了,放在机子里与拿出机子不一样?(05-08)

- 如何进行GSM手机双频天线的阻抗匹配(05-08)

- 求解惑,关于天线阻抗匹配的问题(05-08)

- 微带贴片天线阻抗匹配问题(05-08)

- 求有关微波阻抗匹配的英文资料(05-08)

- 微带天线的设计和阻抗匹配(05-08)