如何在PCB上给多路RF transceiver提供完全同步的本振信号

12-14

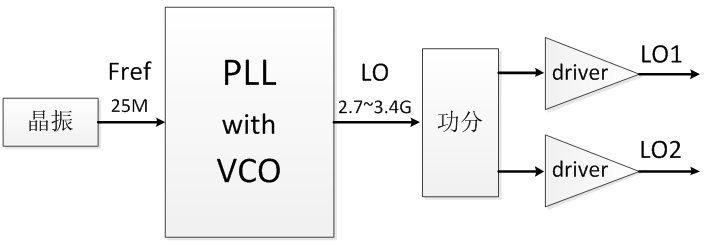

板级系统中,为了保证两路RF transceiver完全同步,准备用一个PLL提供两路本振信号,就是先用功分器将PLL的一路输出变成两路,然后再加上LO driver,像下面这样

但是由于所需本振频率较高(2.7~3.4G),找不到这样的功分器,所以想了另外两种方案:

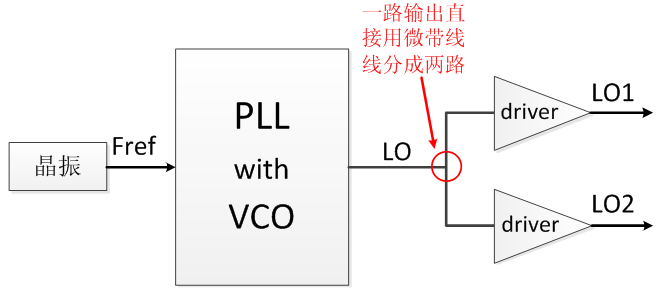

第一种,直接用PCB上的走线将PLL的一路输出变为两路,再加LO driver:

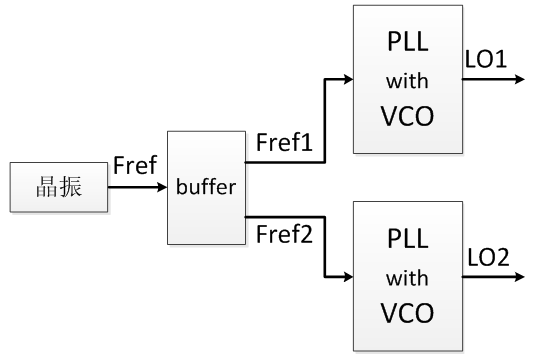

第二种,用一个晶振通过一个两输出的buffer给两个PLL提供参考输入,这样来产生两路本振信号:

请教一下上面两种方案哪种好点,或是有什么更好的方案吗?多谢了。

ADI有clock distribution的芯片,你看看有没有合适的?

第三个图两个本振的相位差不定

第二个图如果面积允许,用微带线做个功分器吧,这样两个混频器影响小一些。

.36

一、二、三都不同步,还是一的驱动,放功分器前面吧,要不有幅度和移相。

我去查了一下,clock distribution由于功率方面的原因好像不能用于本振信号

第三个图是因为两个PLL的锁定时间不确定吗

一是因为两个driver造成的不同步吗?这两个driver用的同一个型号的,走等长线也不行吗

PLL只能保证频率相同,不能保证相位相同,相位是有offset的

找到了一个可以产生四路输出的PLL(集成VCO),TI的TRF3765,datasheet里说了“Outputs are phase-locked but not phase-matched”,是不是就意味着无法保证这四路输出相位同步了...

就算他能保证输出相位同步也没啥意义,你外围电路不可能等相位的

.55

相关文章:

- 请教大牛:接收机多路射频通道之间怎样隔离?(05-08)

- 多路波导功分器怎样设计,而且要求各路功率有一定的配比 (05-08)

- 求指导多路功分器怎么做?怎么提高指标 (05-08)

- 问个异步通信中数据帧同步的问题 (05-08)

- 请问什么是 电磁兼容 和 信号完整性分析 ? (05-08)

- 做信号完整性分析好不好?(05-08)

射频专业培训教程推荐