求PLL 高手

12-13

调试一PLL,adf4157鉴相芯片,10MHz参考,环路大概100khz左右

要求锁定时间比较短,一般30us吧。

例如 让他中心频率5.99GHz, 扫宽1Hz ,扫描1万多个点,平均80us一个点。

每次都会些adf4157,即使频率是mHz级别的改变,

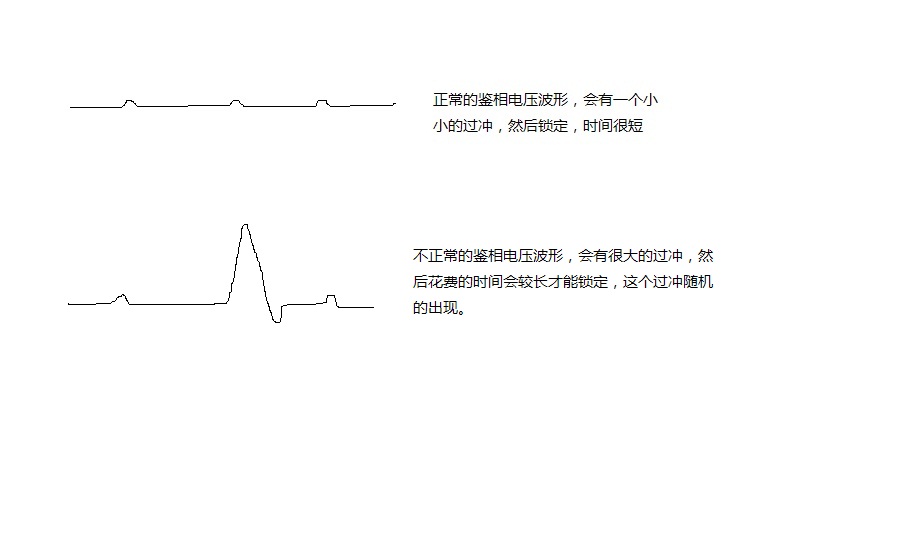

用示波器交流检测鉴相电压,可以看出大部分的频率切换点会稍微上升一点,然后就锁定。

但是随机的会出现突然的一个很大的过冲,然后在锁定。

如图所示的

在上面表示出波形出来,因为调谐得比较小,而且很大的过冲出现是随机的,虽然能锁定,但是时间比较长,导致采样的时候会出现误差。

想问下论坛里面的高手,这个问题是怎么出现的? 是硬件设计有问题吗?(个人不知道该怎么分析,如果说是硬件的问题,但是这个是随机出现的,除非说是在临界状态,但是改变环路啥的,貌似都有这种情况。

也做了其他的实验,换频率点,比如说4GHz的位置,貌似就不出现了,4G和5.99G的那个Kv貌似差别有点大,4G大概在150-200MHz/V ,5.99G大概在50-80MHz/V ,不过我改变电荷泵的电流貌似也没有改善)

所以想请坛里面的PLL高手指点下。

要求锁定时间比较短,一般30us吧。

例如 让他中心频率5.99GHz, 扫宽1Hz ,扫描1万多个点,平均80us一个点。

每次都会些adf4157,即使频率是mHz级别的改变,

用示波器交流检测鉴相电压,可以看出大部分的频率切换点会稍微上升一点,然后就锁定。

但是随机的会出现突然的一个很大的过冲,然后在锁定。

如图所示的

在上面表示出波形出来,因为调谐得比较小,而且很大的过冲出现是随机的,虽然能锁定,但是时间比较长,导致采样的时候会出现误差。

想问下论坛里面的高手,这个问题是怎么出现的? 是硬件设计有问题吗?(个人不知道该怎么分析,如果说是硬件的问题,但是这个是随机出现的,除非说是在临界状态,但是改变环路啥的,貌似都有这种情况。

也做了其他的实验,换频率点,比如说4GHz的位置,貌似就不出现了,4G和5.99G的那个Kv貌似差别有点大,4G大概在150-200MHz/V ,5.99G大概在50-80MHz/V ,不过我改变电荷泵的电流貌似也没有改善)

所以想请坛里面的PLL高手指点下。

图貌似就是上面的一个小空白,点击下可以打开~

谢谢了

让他中心频率5.99GHz, 扫宽1Hz ,扫描1万多个点,平均80us一个点。

不明白这个,步进多少,频率范围多少,环路带宽设计了多少,每次扫点是频率相邻点?

一般来说是环路问题

中心频率5.99G。扫宽1Hz ,扫描1万个点,等于说是步进是万分之一Hz,就是5.99GHz-0.5Hz 每次增加万分之一Hz的频率,一直扫描到5.99GHz+0.5Hz 。

平均80us扫描一个点,说明总的扫描时间是80us*10000 =0.8s

就是说扫频一遍最少是0.8s

仿真的环路带宽在100KHz的样子。

都能锁定,扫频的时候偶尔出现过冲,造成锁定时间长了,采样的时候就会有误差,造成指标不过

步进很小,PLL是如何改变输出频率的,改变参考or分频比,一般来说改变参考频率使得输出频率改变的方案不会出现你说的问题?建议采用DDS上变频,实现这个稳稳的。

主要就是改变控制字来改变分频比,参考是固定的10M,DSP给出来的。

我这个是要实现100K-8.5G的信号源的,低端是用DDS实现的。

问题已经解决了,是因为每次写控制字的时候,我都重置了下小数分频模块造成的。

不过还是谢谢你。

其实虽然步进很小,但是如果频率改变小于1Hz的话,就不做改变,虽然是扫这么多点,但是大概中间就变一次,但是每次都会重新写入控制字。

这个一开始不知道,后来组长和我说的,我当初也以为每次都改变那么一点点。

相关文章:

- 如何用pll实现输入信号的8倍频?(05-08)

- 请教:用PLL实现FSK解调的问题 (05-08)

- PLL里的基准频率源怎么选择?(05-08)

- 谁给推荐一个频率较高的PLL,比如10GHz以上的... (05-08)

- 请假射频技术中的PLL和VCO(05-08)

- 有没有用在pll的单独的charge pump卖?(05-08)

射频专业培训教程推荐