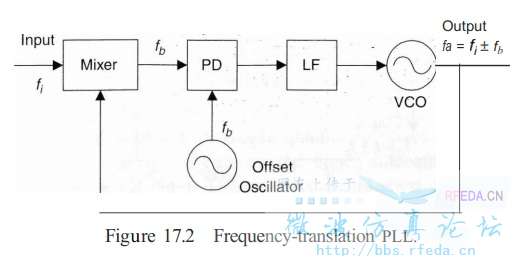

频率搬移PLL(Frequency-Translation PLL)

05-08

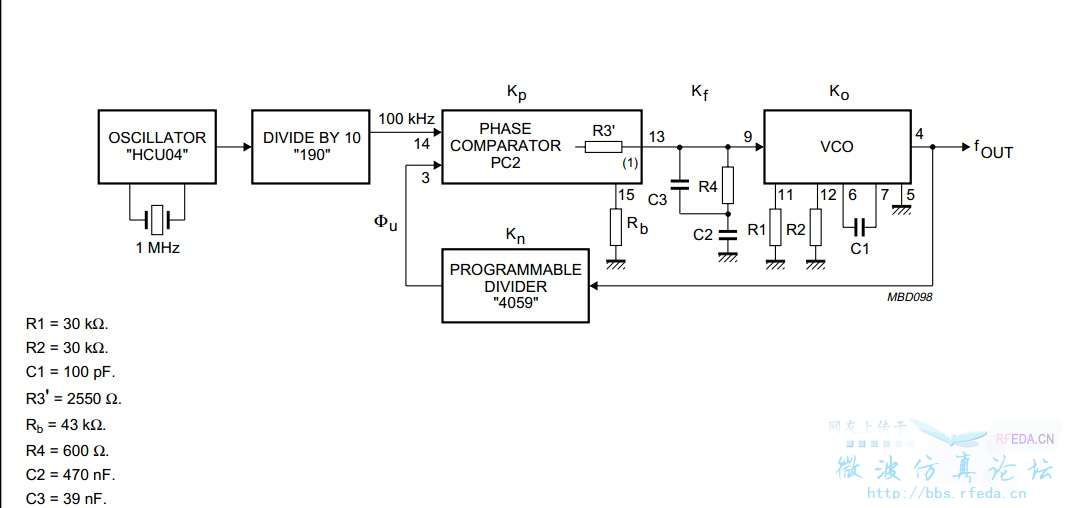

如上图是Gardner著书《Phaselock-Techniques》中411页中介绍的频率搬移的锁相环模型。将外差电路和锁相环电路结合起来,结构上就是把经典PLL模型中的分频器改成了这里的混频器。我想请教前辈们,这里的环路滤波器是怎么设计的?经典PLL模型中的环路滤波器都有现成的公式或者软件设计,环路滤波器的各参数和传输特性有关,特别是计算公式中将分频器的分频值N放在里边,而这里将分频器换成了混频器,那么原来的计算公式就不适用了。这个应用电路的环路滤波器的设计资料好少,我只好在论坛里向各位前辈请教了,先行谢谢啦!

在这种混频电路中,其实分频器 可以看做分频次数为1。环路滤波器的计算 并不涉及具体的频率。任然使用电路中的 Kv等参数就可以。若使用仿真软件,可以将VCO的频率认为降低些,Kv等参数不变进行仿真计算。 根据我的经验,仿真结果和实际测试相差不多。

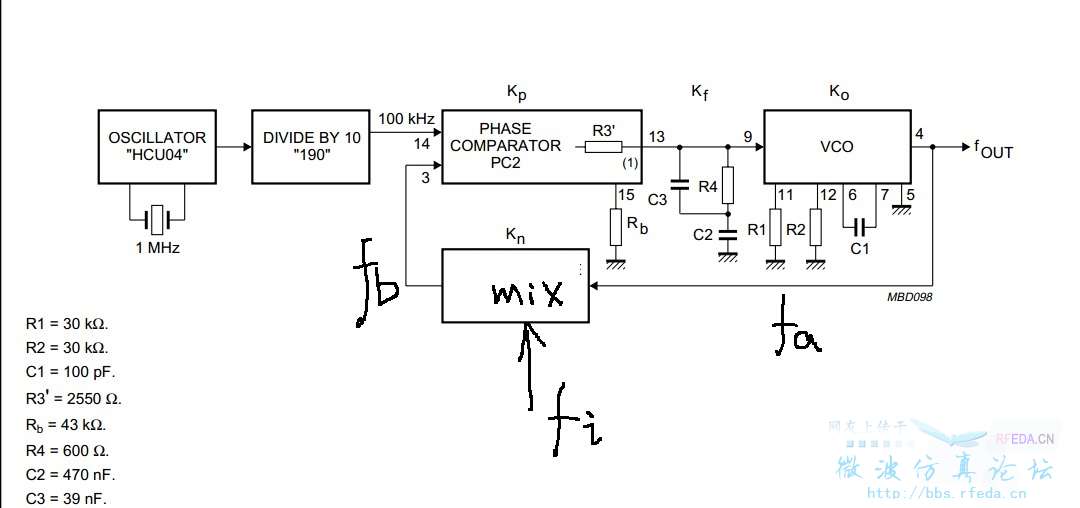

环路滤波器取决于VCO,压控电压小于5V用经典无源环路,高于5V用有源环路。如果混频器采用下变的话。公式改成fb=fa-fi。你只需将PLL控制字中频率部分写成fb的频率。VCO就会输出fa的频率。

谢谢前辈!我对您“只需将PLL控制字中频率部分写成fb的频率。VCO就会输出fa的频率。”这句话还是不太理解,我是用PLL芯片74HCT9046A中的PC2作为我的鉴相器,环路滤波器用74HCT9046A芯片资料中推荐的无源滞后超前滤波器。如上图,就是将反馈通路中的分频器改成混频器,您能否就上图帮我分析一下?谢谢啦!

谢谢gzsea前辈,我的老师也说混频器的相位增益为1.但是我涉及的VCO输出频率到了20GHz以上,KV值接近800MHz/V,这样因为混频器增益比分频器大很多,而鉴相器的增益不变,是不是要将LF的增益减小?不知道具体怎么做,目前还在摸索之中。

混频增益应该不用考虑,20G的话 压控斜率有点大,估计滤波器不好做。多试试吧,有问题再讨论

好的,谢谢您!

相关文章:

- 求助:请问用HFSS可以在多高的频率下计算?(05-08)

- 晶体管的频率!(05-08)

- 请问信号发射接收之后有个“偏移频率”,到底原因是什么呢?请(05-08)

- 无线频率资源划分(05-08)

- hfss仿真矩形微带天线,谐振频率怎么看?(05-08)

- hfss Eigenmode计算出来的频率的问题~~~~~~~~~~~!(05-08)

射频专业培训教程推荐