求救:关于ADF4107锁相环的问题

调环路滤波器

你仿真的环路带宽是不是很窄,建议宽些,一般在鉴相频率的1/20左右,我一般是这么做。仅供参考!

环路带宽我调整了好多次都不管用,郁闷死

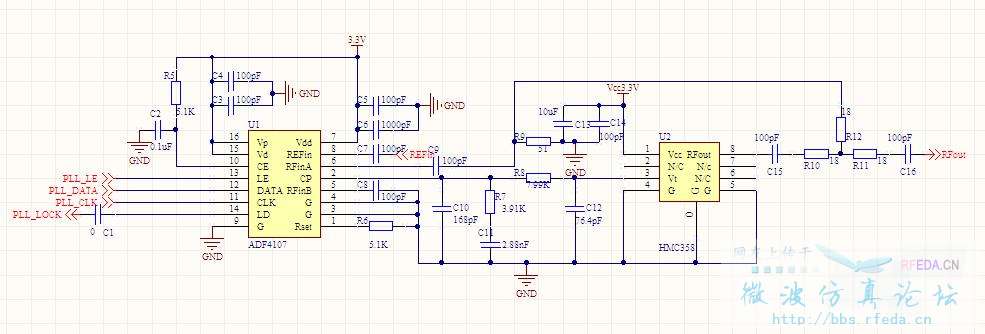

上传 看看情况

环路上有运放吗?要有的话运放应该是轨对轨

你可以看看ADF4107的CLK、DATA、LE与单片机相连的三根线有没有接错或有没有交叉。

建议你改下寄存器的值,看下LD端口在各种情况下的输出是否能跟寄存器的分频值对应上,另外环路带宽适当的调整。还有就是你画的PCB实在是不怎么样?电源线不应该跟射频信号线并行,这个在射频里是大忌。

我想问下,①LD端口的也是有频率输出么?(比如说,我用的RFref=40MHZ,R=40,那么LD端口的能测到1MHz的信号?);

②环路带宽我调整了好多次,我去的环路带宽是鉴相频率的1/20;

③PCB画的不怎么样,呵呵,初学着画,好多东西还在实践中,我这PCB大小为15*15(mm),而且端口位置不能调整、背面大面积地不能走线,所以布置走线感觉有点拥挤,还望多多指教,谢谢

LD 端口可以输出N、R等不同的形势,看PDF--Function latch map 这个寄存器中有。PCB版图确实不怎么样,怀疑能否调出来。

哦哦……PCB的问题还望这位高手指定迷津啊

这位高人,能否指点下就我贴上的PCB图上的问题,我之前画过一版确实没调出来,现在正更改,但是改来改去也不知道怎么改了,还望你给指点下,不甚感激

我也不是高手,大家相互学习,也可能有不对的地方,仅供参考;首先电源要干净,电源供电不能跟射频信号并行,尽量的远离;参考时钟不要再芯片底部走,底部走个电源就可以了;射频信号最好根据实际的板子用其相应的微带线;环路滤波之后最好不要再VCO下部走,这样会影响环路!器件之间的距离再稍微减小点,可以再节省点空间。奔着供电电源干净,参考时钟干净,环路避免受影响的思路吧,应该会有所改善,呵呵。仅供参考!

谢谢你,领教了,大家都在交流中共同进步

首先你确定程序没问题么,你先用示波器看看发的数对不对

做锁相环时好多情况都是软件要调试

还有你看看4107寄存器的值写的顺序对不对

ce端为什么加了个5.1k 应当为0的

如有需要批量需要 可以联系我哦 呵呵

建议把射频线上的51Ohm电阻去掉,射频线转弯也太多了吧,画成50欧姆微带线。电源,参考晶振,环路带宽这些应该只会影响性能,还不至于锁都锁不住吧。主要检查一下控制字及PCB版图。

4107我也用过根据我的经验,锁相环路不锁有这几方面原因

1程序寄存器设置的不对

2程序控制的IO引脚与pll的io不匹配,说白了就是单片机le接pll 的clk上等低级错误,但小编这种现象看这种情况可以排除,

3环路滤波器配置的不好

4有一点我不太明白的原理图上LD外为什么要接一电容?muxout设成数字指示信号到不了单片机啊?

来看看,有木有什么好的介意

学习了,最近正好也要做一个锁相环

你好,根据我使用的板材和频率计算出来的50欧姆微带线很宽,和我板子的尺寸相比,微带线太宽了,像这种情况你一般怎么解决?

问题解决了么?

相关文章:

- 请问高手有没有9G的锁相环(05-08)

- 求Razavi的那本讲锁相环的书 (05-08)

- 哪里可以下载《 锁相环设计仿真与应用》(05-08)

- 请推荐一本关于锁相环的书(05-08)

- 问个锁相环测试的问题(05-08)

- 求教关于锁相环带宽的问题! (05-08)