基于DDS驱动PLL结构的宽带频率合成器设计

05-08

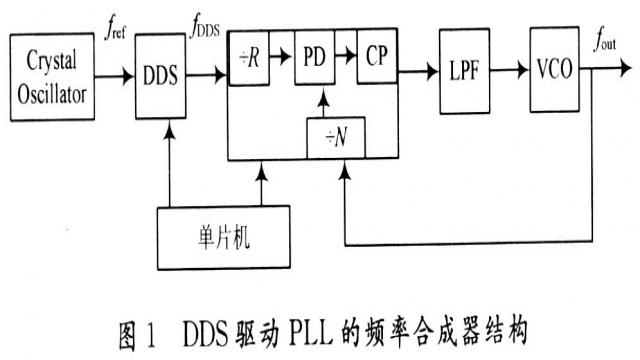

结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分 辨率、低杂散、宽频段频率合成器,并对该频率合成器进行了分析和仿真,从仿真和测试结果看,该频率合成器达到了设计目标。该频率合成器的输出频率范围为 594~999MHz,频率步进为5Hz,相位噪声为-91dBc。

电路实现

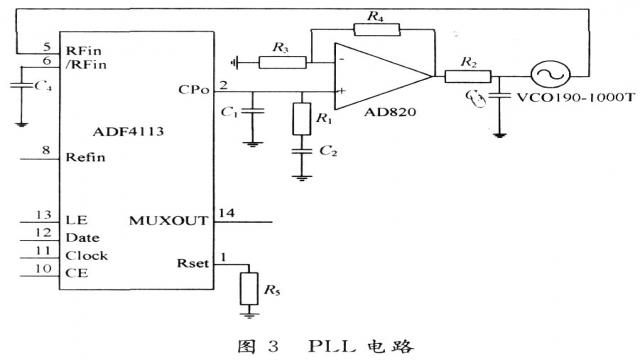

对于DDS模 块,采用了AD9954芯片产生低频参考信号。AD9954是ADI公司最新的AgiIeRF合成器,具有32位的频率控制字。在400MHz的时钟频率 下,输出频率分辨率可以达到约4.7×10-5Hz,具有14位可编程移相单元。芯片采用了先进的:DDS技术,内部集成14位的高性能DAC。该DAC 具备优秀的动态性能,相位噪声优于-120dBc/

电路分析与仿真

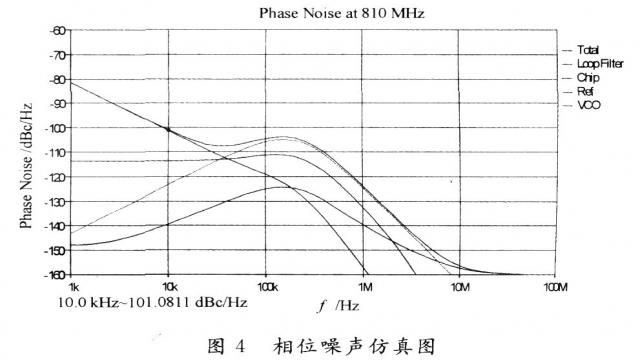

为了分析和评估提出的频率综合器性能,采用ADISimPLL软件对该方案的相位噪声模拟仿真。仿真结果如图4,图5所示。这里给出频率为810MHz,环路带宽为120kHz的相位噪声仿真图形以及锁定时间图形,从图中可以看出,该方案满足了设计目标的要求。

电路实现

对于DDS模 块,采用了AD9954芯片产生低频参考信号。AD9954是ADI公司最新的AgiIeRF合成器,具有32位的频率控制字。在400MHz的时钟频率 下,输出频率分辨率可以达到约4.7×10-5Hz,具有14位可编程移相单元。芯片采用了先进的:DDS技术,内部集成14位的高性能DAC。该DAC 具备优秀的动态性能,相位噪声优于-120dBc/

电路分析与仿真

为了分析和评估提出的频率综合器性能,采用ADISimPLL软件对该方案的相位噪声模拟仿真。仿真结果如图4,图5所示。这里给出频率为810MHz,环路带宽为120kHz的相位噪声仿真图形以及锁定时间图形,从图中可以看出,该方案满足了设计目标的要求。

本帖非原创,但是觉得写的蛮好的。如需继续阅读,请点击:http://rf.eefocus.com/article/id-DDSPLL?p=1

LZ 你知道帖子是谁写的吗

ID都木有,,,,

感谢分享,非常不错

相关文章:

- HFSS9计算简单天线的频率很准!其他结构如何?(05-08)

- 这样的天线用什么结构合适(05-08)

- 请问在ads中如何将电路转化成微带线电路结构?(05-08)

- 在HFSS9中SHEET类型的结构不能使用SUBSTRACT?(05-08)

- 问:MMIC放大器PHEMT源极自偏置电阻和电容版图结构处理?!(05-08)

- 问一下功分器的结构(05-08)

射频专业培训教程推荐