DDS扫频源

最近工作室做了一个小项目,25M-70M扫频源,正好坛子里有活动,也拿上来秀一下,也希望有感兴趣的童鞋们多提意见,交流才有进步嘛!

这个项目看起来简单,但确是最近做的最恼火的项目之一,无他,运气实在太差,调试电脑坏了两台,重装系统,重装软件,恢复数据,再联想到因为买芯片停车被贴条,哎,不说了,说多了都是泪啊……..

转入正题,该项目是个扫频源项目,要求25M-70M扫频输出,1M步进,3MS完成转换,30dB以上的杂散,相噪无硬性要求。说到这里大家看出来了,这是个功能性的项目,对指标的要求是比较低的。

那么,直接上DDS吧,选一款DDS芯片再说,…..AD9851?

呃,这是个什么鬼呢,datasheet的general description部分说了,带高精度DA转换器和比较器,可用作频率综合器和时钟产生器哦亲,32bit频率控制字,0.04Hz精度,最大180M参考时钟哦亲,内部还带6倍频器哦亲,哎,真是居家旅行必备神器啊,好吧那就是你了。

控制部分就简单了,51就搞定了。直接上图吧

file:///C:/DOCUME~1/ADMINI~1/LOCALS~1/Temp/msohtml1/01/clip_image002.jpg

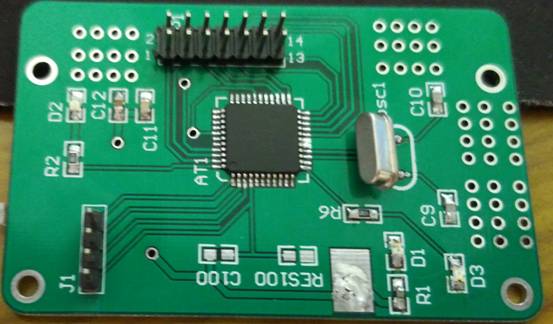

下面就是控制板的PCB

为什么要做成两块板子呢,因为做之前觉得单片机的12M晶振谐波可能比较大,做一块板子的话怕泄露比较厉害,落到输出带内,形成比较严重的杂散,做完之后发现,这个问题就好像小时候纠结是上北大还是上清华一样,想多了!

DDS核心板,主要是DDS+低通滤波器,低通滤波器怎么办呢,上ADS仿一个吧,FILTERDESIGN GUIDE还是好用的,下面是个仿真的响应,凑合着用吧file:///C:/DOCUME~1/ADMINI~1/LOCALS~1/Temp/msohtml1/05/clip_image002.gif

DDS板的PCB

file:///C:/DOCUME~1/ADMINI~1/LOCALS~1/Temp/msohtml1/07/clip_image002.jpg

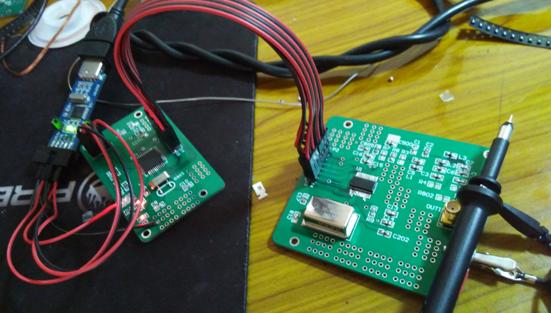

再来一个全家福

file:///C:/DOCUME~1/ADMINI~1/LOCALS~1/Temp/msohtml1/09/clip_image002.jpg

好,大功告成。最后,看看测试结果吧,先看个25M的,这个点杂散就比较好了,但是二阶,三阶谐波就比较大

file:///C:/DOCUME~1/ADMINI~1/LOCALS~1/Temp/msohtml1/11/clip_image002.jpg

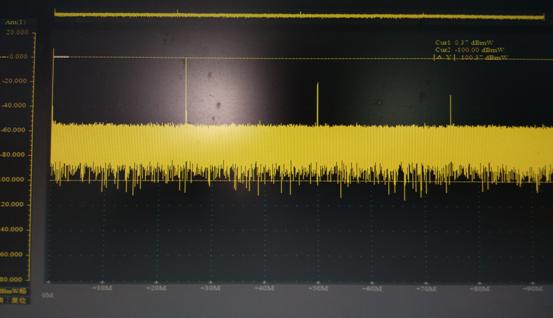

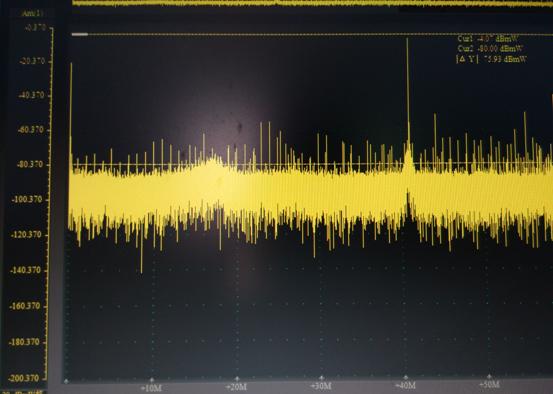

再来个41M的,杂散一片

file:///C:/DOCUME~1/ADMINI~1/LOCALS~1/Temp/msohtml1/13/clip_image002.jpg

DDS的杂散说起来还是比较复杂的,什么相位截断误差啦,DA的交调啊,量化效应啊,采样带来的镜像啊,我就不罗嗦了,这些说起来可以写一篇论文的。

最后再讨论下DDS的零阶保持效应带来的高频幅度压低的问题,这种效应如果是FPGA+DA的方式的话可以用预失真补偿掉,但是DDS的话怎么办?输出加均衡器,这个没试过,不知道好不好弄,或许不太要求杂散的话可以加个饱和放大推平?

赞!感谢支持

赞!坚持就是胜利,有这样不气馁的精神,什么事做不好呢!

赞,谢谢分享!

相关文章:

- 射频模块/中频模块接口(05-08)

- 请问如何在ADS中建立一个模块电路然后进行仿真?(05-08)

- 请问ADS中有倍频模块吗?(05-08)

- 有没有前辈用GPRS模块做过数据远传系统(05-08)

- 请问DAB有哪些射频接收模块产品?(05-08)

- 不同射频模块使用同一天线的问题 (05-08)