PA与ASM的匹配如何影响PA的线性度的?

我还是菜鸟

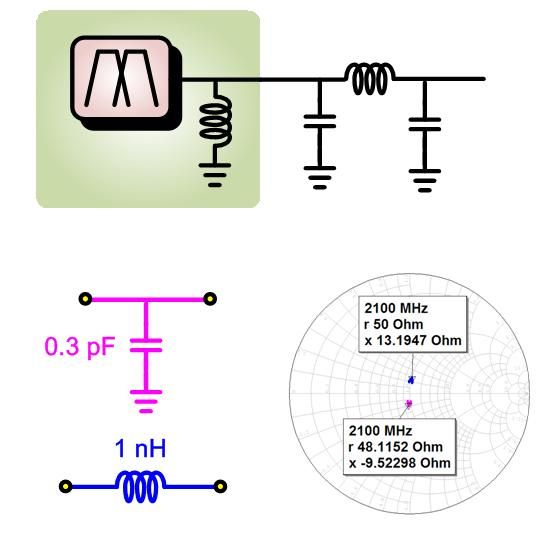

1. 双工ANT Port出来的落地电感 离双工太远或值乱调

通常收敛度只会更差 不会更好

2.后面的Matching电路 可以进一步用串小电感 或并小电容的方式

来加强收敛度 由图可看出 这两种方式 基本上对你阻抗没啥太大变化

但可以加强收敛度

3. 至于落地电容 是两颗都放 还是两颗都不要放

还是只放一颗 若只放一颗 要放哪一颗

这要看实际调校结果而定

4. 当然Layout也有关系 所以ANT Port的Trace

走表层为佳 因为内层是上下都有GND

寄生效应比表层线严重 挖空又没空间 加上内层线阻抗控制通常不好做

而表层走线 在阻抗控制为50奥姆前提下 与两旁GND的间距不要太近

不然也会有寄生效应 甚至双工的ANT Port的Pad 下方Layer2可挖空

减少寄生效应

同问,学习

我的理解是,比如在校准时,校准到的饱和功率不够高?到一定值上不去了,或者高中低信道校准到的功率不平

ASM作为开关本身是有S参数的,并不是50欧姆,从PA到ASM这段网络都作为PA的load,失配的话相当于PA的load偏掉了,当然会影响线性度。一般PA到ASM之间会经历双工器,PA到双工器调位置,双工到ASM调收敛性

PA到双工器调位置,双工到ASM调收敛性?为什么双工到ASM只影响到收敛性?理论上如何解释,不理解,麻烦解释下,谢谢

我自己的理解是,失配会导致输出post loss偏大,相对应PA的输出功率也要更大,这样也就越接近饱和点,线性度也就差了,不知道对不对?

我自己的理解是,失配会导致输出post loss偏大,相对应PA的输出功率也要更大,这样也就越接近饱和点,线性度也就差了,不知道可不可以这样理解?

这个是实践出来的,但是也是有理论支持的,可以用S参数网络的互易性原理,比较复杂;简单的说,双工器本身是容性器件,在射频的电路里存在阻抗发散,导致从PA输出看过去的S11圆变的很发散,不收敛,调试双工到ASM这边的匹配,是为了把双工的容性中和过来,所以常见并电感这种匹配。

可以这么说,但loss并不是绝对的,PA的输出有效率圆,ACPR圆和增益圆,阻抗的实部和虚部决定的位置才能决定PA的性能

谢谢您的解答

多谢!

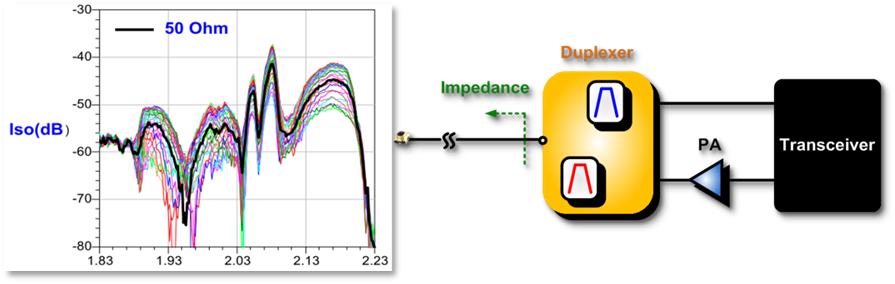

1. 从PA输出 一直到天线 都是PA的Load-pull 都会影响PA线性度

所以常遇到情况是 传导量测时 其CSE很低 因为阻抗在50奥姆附近

但作Wireless测试时 因为天线Matching加进来

使PA的Load-pull偏离50奥姆 以至于RSE Fail

2. PA输出走线过长 走线过细 以及阻抗失配 这些都会让PA的Post-loss变大

走线过长或过细 其传输能量会变热能消耗掉 所以Loss变大

阻抗失配 其传输能量会反射掉 所以Loss变大

而如上图 同样的Target Power 好比24 dBm好了

Post-loss越大 PA输出越大 当然线性度越差

3. 双工器因封装结构之故 多半会呈现电容性

所以ANT Port会需要一颗落地电感 来补偿其电容性

使其ANT Port看出去的阻抗可以收敛

有些双工器 会把这落地电感 直接作在里面

因此ANT Port出去 就不需要再额外挂一颗落地电感

但有些双工器 可能无法把这落地电感作在里面 所以需要自己外挂

因此我们知道 这落地电感 要跟双工器视为一体 若离双工器太远

其阻抗一样会不收敛

另外 要自己再额外放T型或pi型Matching

这落地电感的值是固定的 不能视为Matching来随意调动

否则其阻抗一样会不收敛

非常感谢!

xiexie C da

大神,你的这个框图这么好看,是用什么软件画的?谢谢!

谢谢大神

谢谢分享经验

nice..

大神你好,我上周尝试用网分调w2100的TX收敛圆,发现在其他matching组件不动的情况下,只改双工落地电感的值,从3.3nh改到4.7nh范围,发现收敛圆大小差不多,但改变双工后串的位置的电感值从3nh改到1nh,收敛圆变化较明显。是否可以说串的位置电感对收敛圆大小影响较大。

我觉得你可以把落地电感去掉看看

嗯,我知道落地电感是收敛的前提,后面串的电感主要调收敛圆的大小

1. 双工ANT Port出来的落地电感 离双工太远或值乱调

通常收敛度只会更差 不会更好

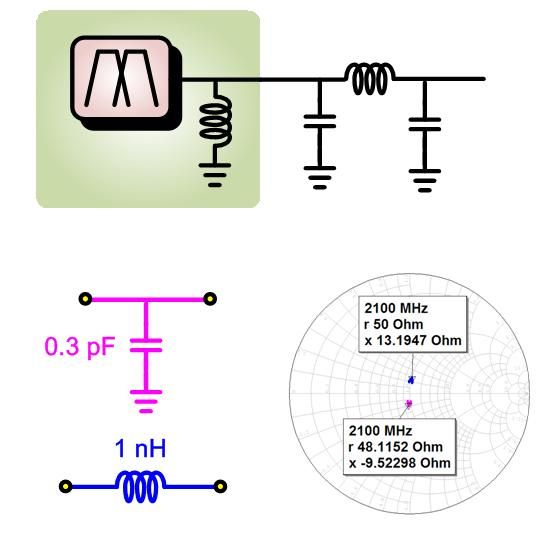

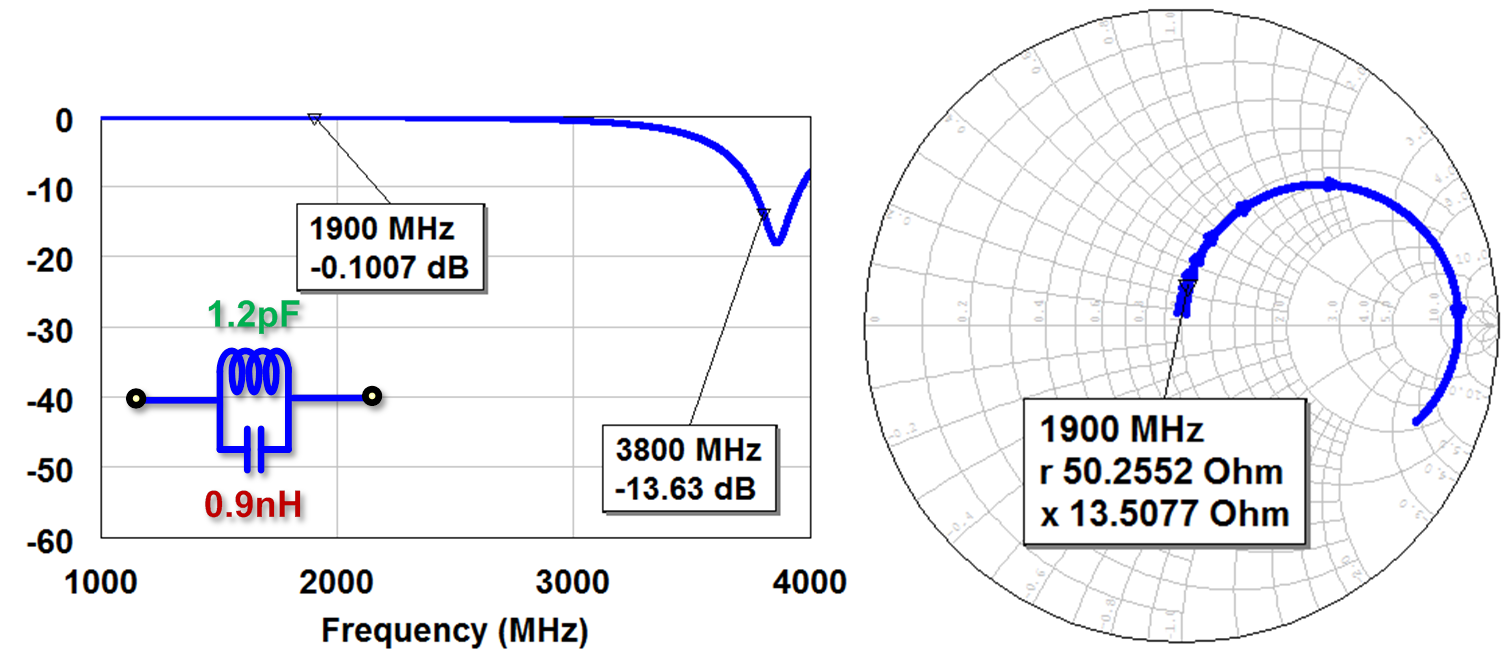

2.后面的Matching电路 可以进一步用串小电感 或并小电容的方式

来加强收敛度 由图可看出 这两种方式 基本上对你阻抗没啥太大变化

但可以加强收敛度

3. 至于落地电容 是两颗都放 还是两颗都不要放

还是只放一颗 若只放一颗 要放哪一颗

这要看实际调校结果而定

4. 当然Layout也有关系 所以ANT Port的Trace

走表层为佳 因为内层是上下都有GND

寄生效应比表层线严重 挖空又没空间 加上内层线阻抗控制通常不好做

而表层走线 在阻抗控制为50奥姆前提下 与两旁GND的间距不要太近

不然也会有寄生效应 甚至双工的ANT Port的Pad 下方Layer2可挖空

减少寄生效应

谢谢大神的解答,还想请教一下MTK平台S22的网分调的话需要连meta打通来看么,还是不用连meta直接从测试座连网分看进去,直接先调双工到ASM的匹配,兼顾着连通情况下S11,将收敛圆调到50欧姆附近。就是S11看连通,S22不连通直接看。这样可以么。

应该是用meta打通开关吧,好像还可以直接接50欧姆然后接地

大神正解,好好学学。

本质上是调节PA的lOADPULL

学到不少知识

大神!小弟请教下关于匹配方面的问题:

一项目上有 W band2的传导二次谐波问题(宽频PA AP7218M DPX MURATA)

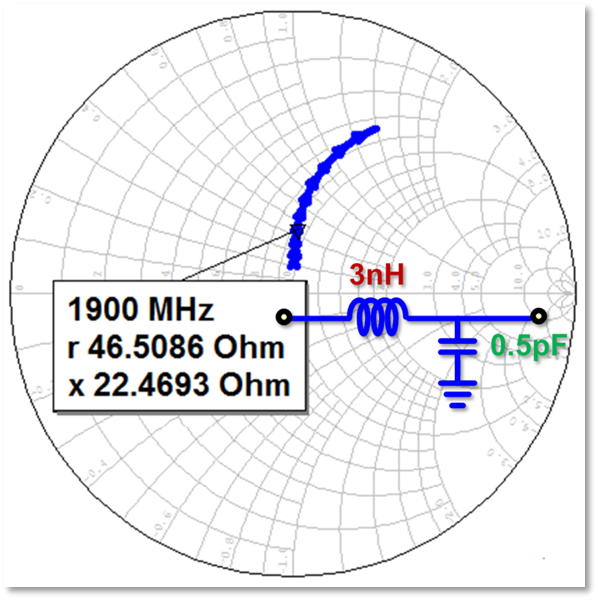

1.在DPX的ANT Port端并3.6NH后,额外加L C低通滤波(串3NH 并0.5pf),二次谐波从-30降到-40 但收敛性变差

2.清空PA到DPX TX端匹配,只将L C低通滤波(串3NH 并0.5pf)这种形式放在DPX的TX端 ,二次谐波没有改善还是-30左右

同样的滤波形式,为什么只有放在DPX ANT端才对谐波有抑制作用?

学写了

从仿真来看 串3NH 并0.5pf 会让阻抗远离50奥姆

这是假设你原始阻抗完全50奥姆的情况下

更何况你实际的原始阻抗不可能完全50奥姆

再加上实际上PCB会有寄生效应之类

也就是说 实际上有可能这组低通滤波 是有可能会让你阻抗离50奥姆更远

在这情况下 Load-Pull移到了二阶谐波较差的位置

让你二阶谐波恶化

在此情况下

低通滤波 : 抑制二阶谐波

低通滤波 : 改变Load-pull 恶化二阶谐波

一来一往抵销情况下 很可能较就像你观察到的一样 完全没改善

但就像你问的 那为啥放DPX ANT端 是有用的?

难道放DPX ANT端 PA看出去的Load-pull就不会改变?

当然也是会改变 但是改变程度会比较小

因为你放DPX ANT端 跟PA输出 还隔了一个双工器

跟你直接放DPX的TX端 也就是PA输出 当然影响程度有差

原则上离PA输出越近 其影响程度越大

有几点要注意

1. 你ANT Port端并的3.6NH 是Murata建议的值吗?

因为这个值会影响收敛度 最好依照厂商建议值 不要随意更换

2. 不太建议你放DPX ANT端 因为这边同时也是RX路径

也会影响RX阻抗 你救了谐波 却牺牲灵敏度

这你要考虑值不值得 要测试才知道

3. 灵敏度的恶化 不只来自RX阻抗改变 也来自隔离度的劣化

因为DPX ANT端的阻抗 是会影响隔离度的

刚由仿真已知 这组低通滤波器 确实是会影响阻抗

使其远离50奥姆 有可能因此隔离度变差

TX Leakage的危害变大 当然灵敏度变差

除此之外 TX Leakage的危害变大 也会影响Blocking的性能

4. 既然这组低通滤波器 确实是会影响阻抗 使其远离50奥姆

在此情况下 有可能ACLR跟EVM也一并变差

你救了谐波 却牺牲ACLR跟EVM

这你要考虑值不值得 要测试才知道

5. 如果你只Fail二次谐波 三阶谐波Pass的话 你可以直接兜Notch Filter

对主频只有0.1dB的Loss 阻抗也不会偏太多

虽然只砍13 dB 不过若顺利 原则上也够了

当然 这组Notch要放DPX的TX端

我知道你电路图没有预留Notch Filter 你可以直接迭罗汉

当然 你若要兜落地的Notch Filter 也是一样手法

貌似B1得匹配一般是并2.2NH吧

@criterion 感谢! 佩服!

小弟上次反馈的WCDMA B2 二次谐波问题,现补充如下:

1.DPX的ANT端并3.6NH 是不考虑二次谐波问题 用网分实际调试确定的值(MURATA规格书推荐值3.3NH)

2.大神提到该LC滤波形式加上的DPX的ANT端后,要考虑带来RX LOSS和TX leakage方面的问题

这个确实要考虑,不过小弟实际调试结果还好,只是收敛性差带来高信道的电流较大(650mA左右)

3.实际测试是只有二次谐波超标,你建议 上Notch Filter。

这个小弟再实际尝试,看下效果。 (放在DPX的TX端,是出于Notch Filter对阻抗影响不大,但于DPX的ANT,对收敛性影响大?)

4.仔细排查,发现引起二次谐波的主要因素是 所用PA的二次谐波较大(-7dBc) MURATA对二次谐波的抑制也不够(21dB)

这对后期项目设计,器件选型方面有一定指导意义

谢谢分享

1. 从PA输出 一直到天线 都是PA的Load-pull 都会影响PA线性度

所以常遇到情况是 传导量测时 其CSE很低 因为阻抗在50奥姆附近

但作Wireless测试时 因为天线Matching加进来

使PA的Load-pull偏离50奥姆 以至于RSE Fail

2. PA输出走线过长 走线过细 以及阻抗失配 这些都会让PA的Post-loss变大

走线过长或过细 其传输能量会变热能消耗掉 所以Loss变大

阻抗失配 其传输能量会反射掉 所以Loss变大

而如上图 同样的Target Power 好比24 dBm好了

Post-loss越大 PA输出越大 当然线性度越差

3. 双工器因封装结构之故 多半会呈现电容性

所以ANT Port会需要一颗落地电感 来补偿其电容性

使其ANT Port看出去的阻抗可以收敛

有些双工器 会把这落地电感 直接作在里面

因此ANT Port出去 就不需要再额外挂一颗落地电感

但有些双工器 可能无法把这落地电感作在里面 所以需要自己外挂

因此我们知道 这落地电感 要跟双工器视为一体 若离双工器太远

其阻抗一样会不收敛

另外 要自己再额外放T型或pi型Matching

这落地电感的值是固定的 不能视为Matching来随意调动

否则其阻抗一样会不收敛

点评回复

支持

反对

可以这么说,但loss并不是绝对的,PA的输出有效率圆,ACPR圆和增益圆,阻抗的实部和虚部决定的位置才能决定PA的性能

相关文章:

- PA后匹配问题(05-08)

- 关于LNA输入匹配的问题!(05-08)

- mt6139的SAW FILTER 匹配问题(05-08)

- 6139接收端的50 ohm SAW匹配问题(05-08)

- saw filter 匹配求助(05-08)

- 功率底应该调哪边的匹配? 匹配在没有其他仪器的情况下,应该怎么从哪方面开始调,请高(05-08)