求助,求助。网分使用疑问

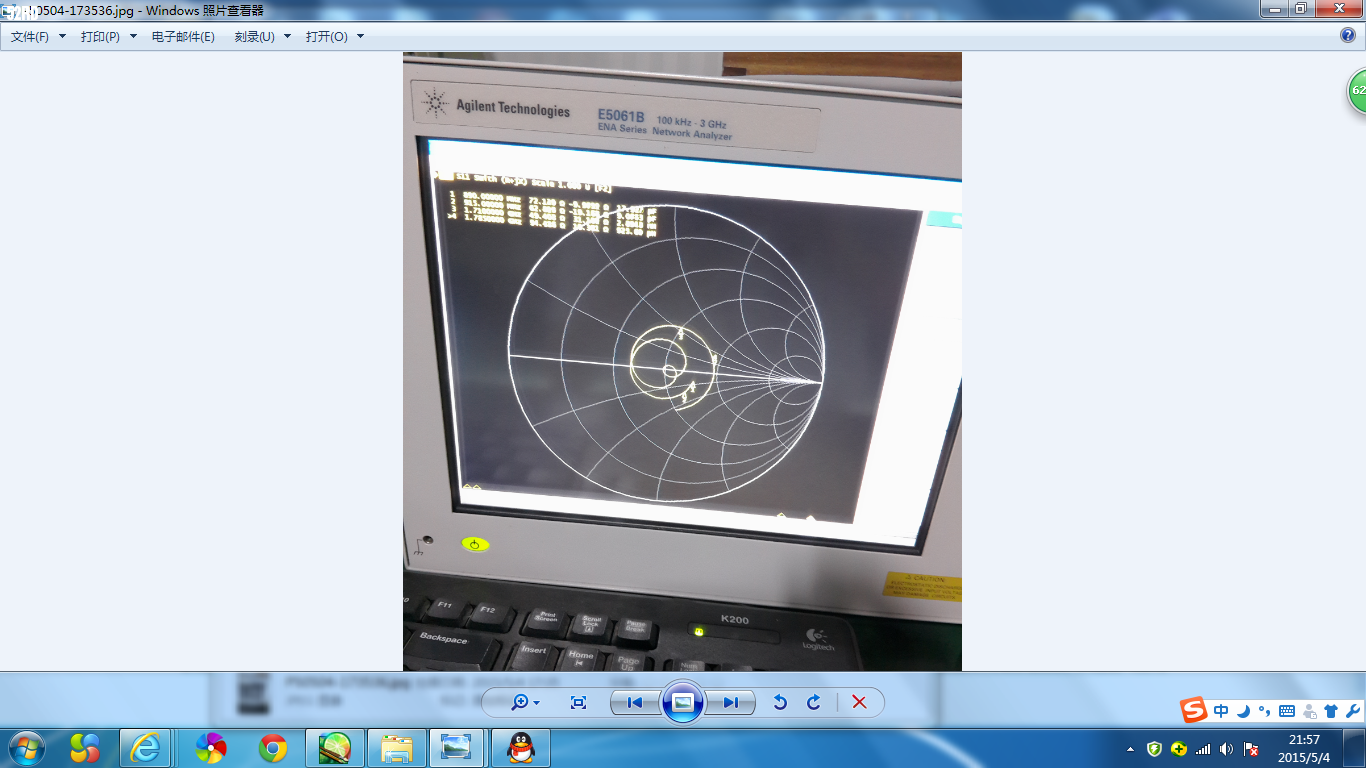

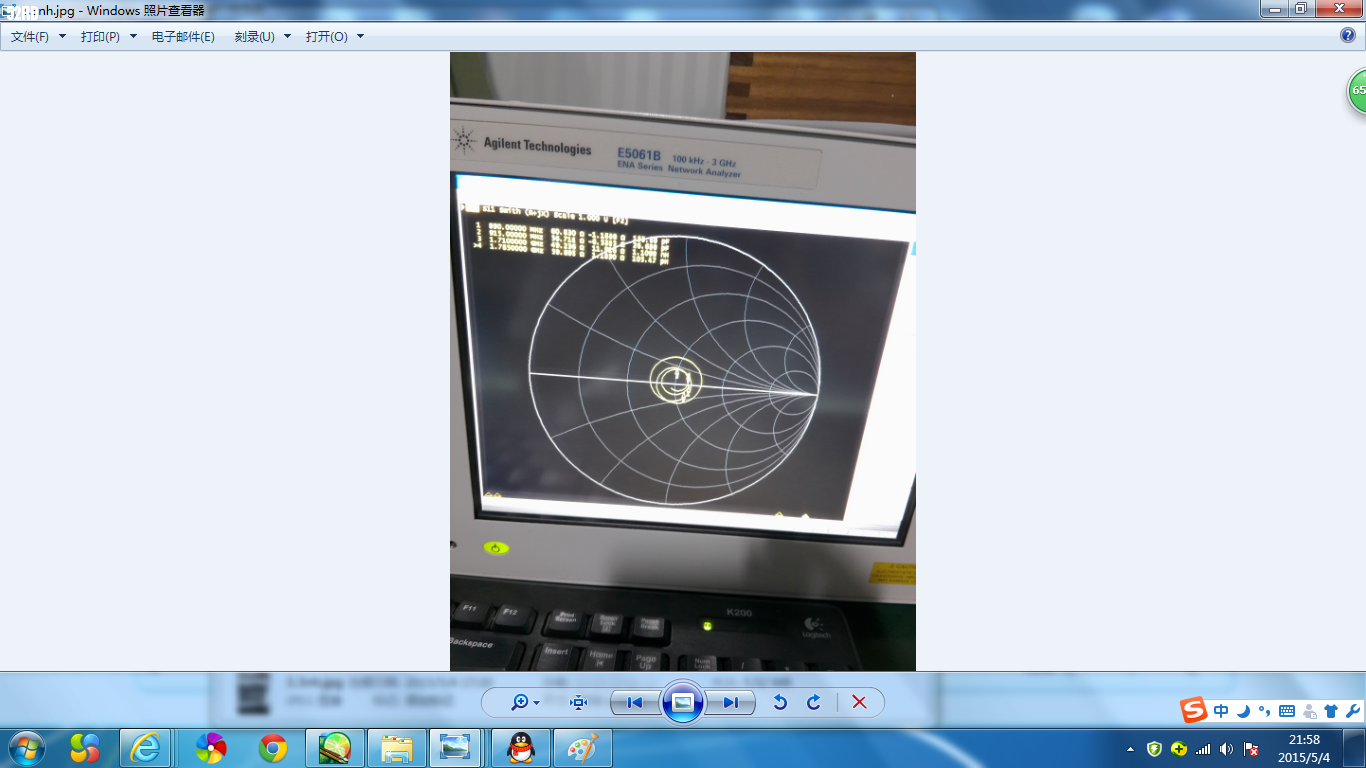

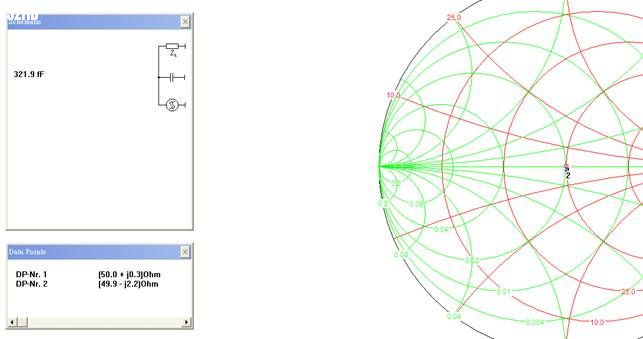

刚开始学习网分调试匹配,完全根据论坛里《PA效率优化》文档操作,但是实际结果和串联电感顺时针旋转串联电容逆时针旋转这个规律不符啊,下面是我在板子上串联0欧姆,3.3nH,5.6nH,后的图,怎么解释,哪位大神教教。

另外 量测跟仿真不准

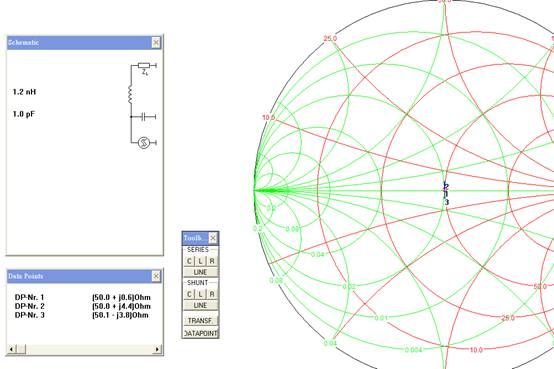

还有一个因素 那就是你的RF频率

是否超过电感/电容的SRF

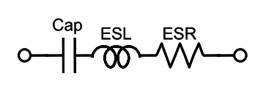

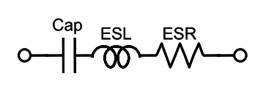

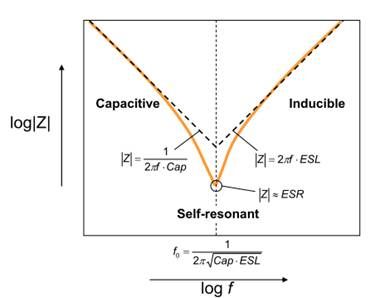

电容的等效电路与频率响应如下:

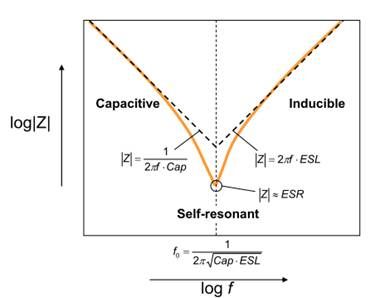

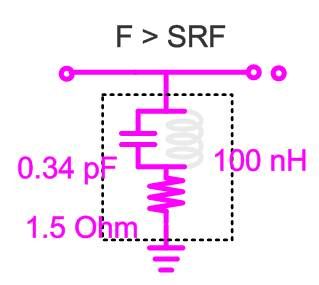

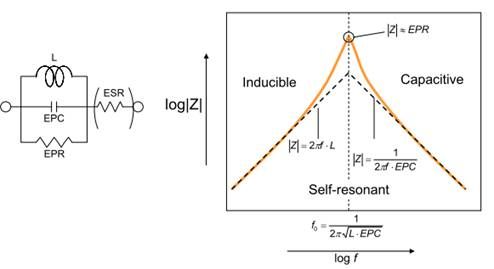

电感的等效电路与频率响应如下:

所以我们由上图可知

电感不是一直呈电感性 若频率超过SRF 就会变电容

电容不是一直呈电容性 若频率超过SRF 就会变电感

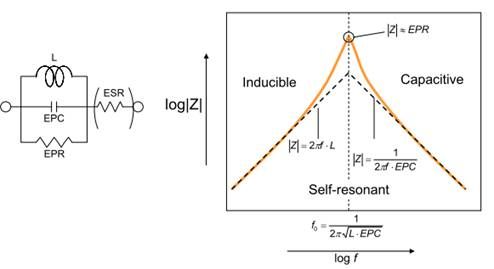

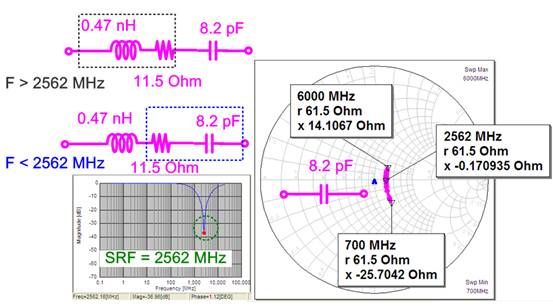

我们以串8.2pF电容为例 频率范围是700 MHz到6000 MHz

我们由上图可看到 其SRF为2562 MHz

换言之 当频率大于2562 MHz时 该电容会变电感

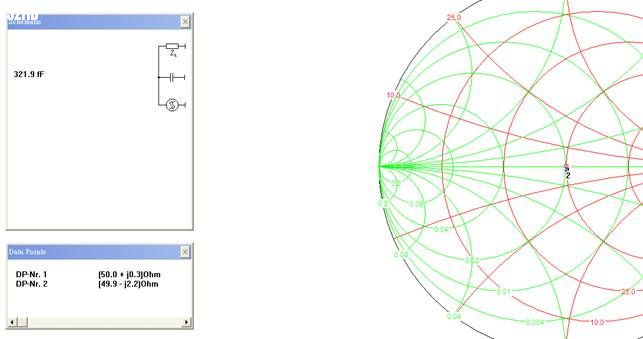

而由Smith Chart也证实这点

当频率小于2562 MHz时 此时是电容 确实就是按照串电容的趋势在走

但当频率大于2562MHz时 此时是电感 反而是按照串电感的趋势在走

而由上图也知 不管频率点为何 都会有电阻

这表示你只要串联组件 不管电容或电感

其内阻就是会造成讯号损耗

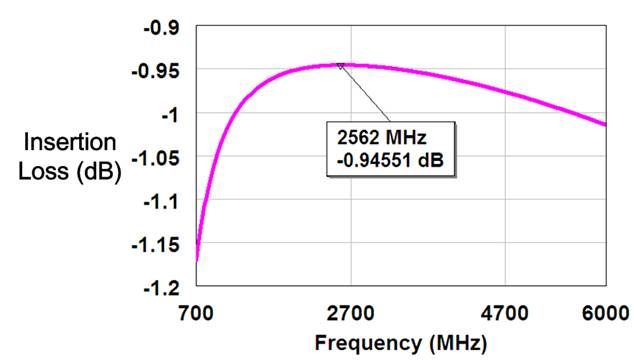

串8.2pF电容 内阻为11.5 Ohm Insertion Loss如下图:

所以如果想要使阻抗点有所较大的移动

尽可能不要用串联小P数电容的方式

因为电容值越小 其内阻越大 亦即Insertion Loss会越大

同理 你要使阻抗点有所较大的移动

尽可能不要用串联大n数电感的方式

因为电感值越大 其内阻越大 亦即Insertion Loss会越大

况且根据ZL = jwL的公式 L值越大 感抗越大

如此一来 其Insertion Loss会更大

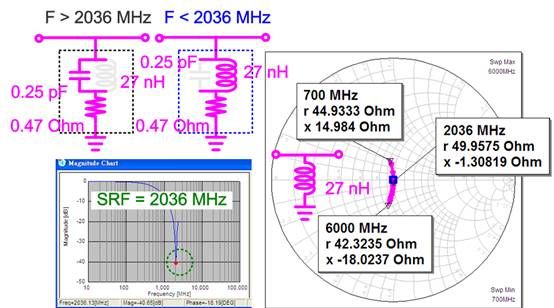

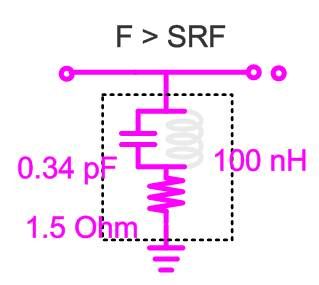

再以并27nH的电感为例

由上图可知 其SRF为2036 MHz

当频率小于2036 MHz时 此时是电感 确实就是按照并电感的趋势在走

但当频率大于2036MHz时 此时是电容 反而是按照并电容的趋势在走

当然 有些方案 并不是为了调阻抗位置 例如:

串大P数电容 => 在不影响阻抗情况下 当DC Block

串小n数电感 / 并小P数电容 / 并大n数电感 => 在不影响阻抗情况下 使阻抗收敛

而电容跟电感的SRF 都跟其值成反比

换言之

电容值越大 其SRF越低 越容易变电感性

电感值越大 其SRF越低 越容易变电容性

因此上述串大P数电容 跟并大n数电感的方案

是否会因

电容变电感性 电感变电容性

使得阻抗偏掉? 反而使阻抗难以预测?

答案是不会!

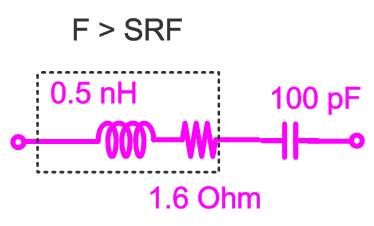

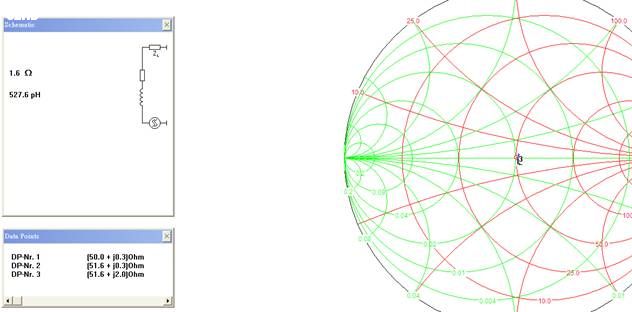

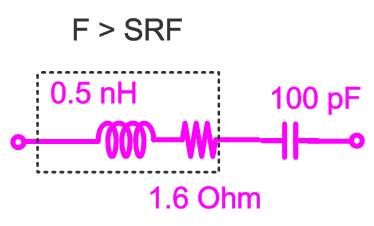

以串联100 pF的电容为例 当频率点超过SRF时

会变成电感在主宰

但实际上 即便是0.5nH的ESL在主宰 其阻抗依旧不动如山啊

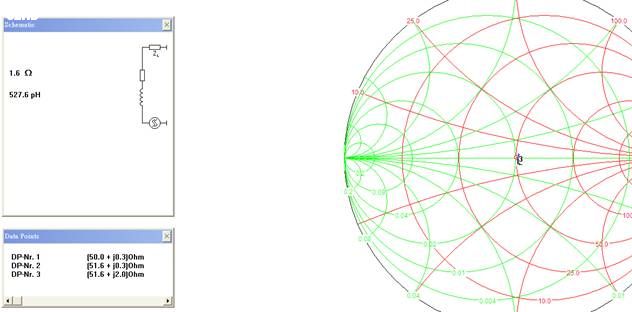

再以并联100 nH的电感为例 当频率点超过SRF时

会变成电容在主宰

但实际上 即便是0.34pF的EPC在主宰 其阻抗依旧不动如山啊

因为其电容的ESL 或电感的EPC

多半都很小

因此串大P数电容 与并大n数电感

即便过了SRF

也顶多是变成串小n数电感 与并小p数电容

而这两个情况 不会剧烈改变你的阻抗

因此 串大P数电容 跟并大n数电感的方案

不管频率点为何? 有无过SRF 其阻抗都是不动如山的

但并大n数电感时 要特别注意

因为这是为了加强阻抗收敛用的

所以虽然不管频率点为何 其阻抗都是不动如山的

但若让频率点过了SRF 此时变电容性 那么可能收敛度会变差

而串大P数电容 当DC Block 则比较没这疑虑

因为不管频率点为何? 有无过SRF 都是有DC Block的功用

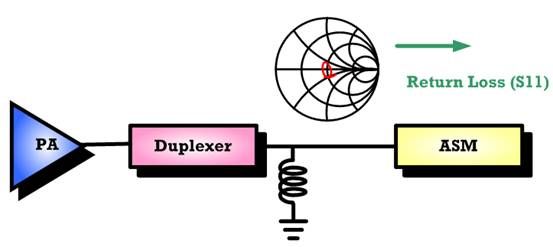

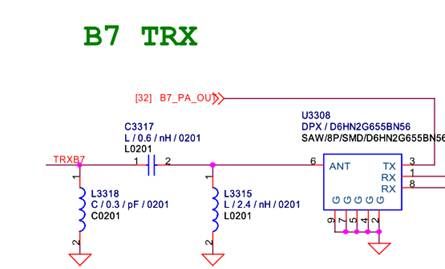

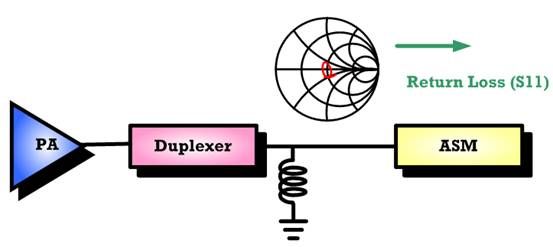

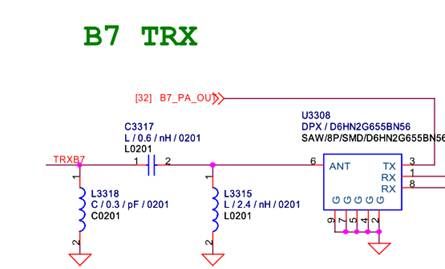

而有个特别案例 那就是Duplexer ANT端的落地电感

这是由于Duplexer的封装结构特性,会使其成电容性,

因此常看到Duplexer输出端,会摆放一颗落地电感,

来抵消其封装所造成的电容性,以加强其S11的收敛度,

亦即Duplexer的输出端,看出去需为一个电感性负载。如下图:

因此这颗电感 必须与Duplexer视为一体 不能以匹配组件来看待

所以该落地电感的值 必须遵照厂商的建议值 不能随便乱调

若值调大了 SRF往低频移动 可能会使频率点座落在SRF右边

此时呈电容性 那阻抗收敛程度会大为降低

若值调小 有可能因电感性不足以抵销其Duplexer封装所造成的电容性,

以至于阻抗收敛程度 依旧大为降低

所以不能随便乱调

至于小P数电容 与小n数电感 因为值小

所以SRF很大 频率点几乎只会在其SRF的左边

不会电容变电感 电感变电容

当然 而由以上分析可知 频率点越高 例如WiFi 5G

其频率点座落在SRF右边的机会越高

加上其PCB的寄生效应会更为严重

因此阻抗会更难预测

E:\360data\重要数据\桌面\音频资料\20140518

无图无真像,但小编不错了,我们公司网分都没有,做4G的时候是临时租台CMW500过来调好就还掉,平时只有8960 CMU200用

E:\360data\重要数据\桌面\音频资料\20150504\0.jpg

不知道怎么上传图片。

果然不行,,

搞了半天终于穿上来了

有图了,快来回答吧。顺便问下要不要来我们公司。

小编也是360爱好者啊

电阻电容电感的高频模型

调试匹配很少用到网分,这问题还没碰到过,在线同看大神解答

从图看,位置没怎么动,但收敛性在变化。调的是滤波器匹配吗?

不是滤波器的匹配,就是很简单的PA输出端到天线端。我不知道为什么串联电感怎么不是顺时针转呢。

360强制的。不想换。快回答问题!

确定的你CABLE 做得没问题,还有就是可能穿电感对阻抗的影响不大,或者你串联的电感不够大

CABKLE应该是没问题的,校准用的线。串联的电感也不想5.6nH。

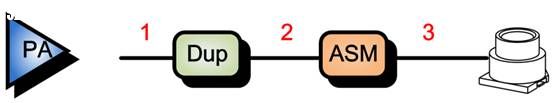

小编调的是双工器后面的还是PA到双工之间的匹配?貌似你这个是在调收敛度而不是在动load pull

你这量的是哪到哪的阻抗啊

就是PA出来到射频座这段,没有双工器。

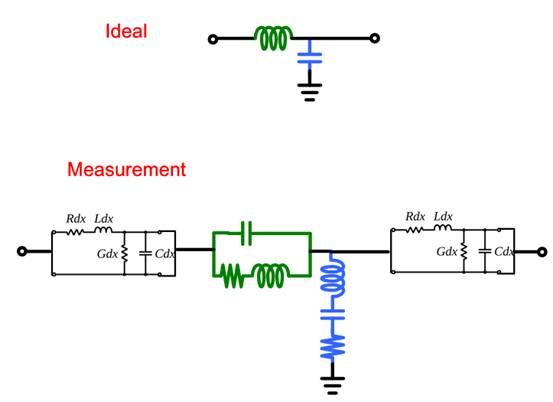

很简单,如图

不准是正常的

准才叫奇迹!

像下图这种趋势

这本来就只是参考用的

原因很简单 因为三个条件没考虑进去

1. 电感/电容本身的寄生效应

2. PCB走线的寄生效应

3. 组件焊在PCB上的寄生效应

当然有人说 第一点好解决啊 Murata的工具 有组件的真实特性曲线

已经帮你把寄生效应考虑进去 你就直接灌入仿真软件去做仿真即可

重点来了 这前提是你得用跟工具上 完全一模一样的型号才可以

哪怕同样是Murata 同样电容值 同样Size

不同型号 其Model就不同

由下图可知 光是同样GRM类别的电容 就有这些种类

那你更不要说不同厂家的电容 其Model肯定都不同啊

第二点更难 请问你要如何把PCB走线的寄生效应

萃取出来 并灌入仿真软件去做仿真?

所以我们由下图可知

VNA量到的是

组件焊在PCB上后 其Model与其PCB的寄生效应 总加成的结果

理想的趋势 完全没考虑到这些

所以只是参考用 若会完全百分百准 那真的是运气好

再来是第三点 组件焊在PCB上的寄生效应

如果是0201的匹配组件 或许这部分可忽略不计(因为Size较小)

但若是IC类的 就无法忽视了

可能很多人常遇到

的现象 用下图来做说明

你可能用Passive的方式去调Section 1,2,3的阻抗

好! 假设这三段 VNA量出来 分别都是50奥姆

但是合在一起量

一路从PA输出 看到Connector 把Section1,2,3全包进来

咦? 反而却不是50奥姆

这是因为 相较于你之前一段一段地量

你这样合在一起量时 又多加了两个因素

那就是IC本身的Model 以及IC焊在PCB上的寄生效应

当然有人会说 这些IC Datasheet上都宣称50奥姆啊

问题是

当这些IC焊到你的PCB上后

其寄生效应 很可能会改变IC本身的输入/输出阻抗 以至于偏离50奥姆

你说你第2层都有挖空? 但若PCB板子较薄 且层数又多

这意味着每一层之间的Gap会大幅缩小

即便你第二层挖空 其表层跟第三层 还是会有寄生效应啊

IC的Data sheet 其Performance 是用厂商自家的EVB量出来的

跟你实际焊在PCB上后量出来的Performance 肯定有差异 或多或少

因为你PCB的迭构走线 跟厂商自家的EVB 铁定不同啊

所以由以上可知 实际的变量这么多

单纯纸上谈兵 怎可能百分百预测准确?

所以我一开头就说了 不准是正常的 准才叫奇迹!

因此以你这例子为例 调串联组件

建议做法是

1. 先用软件去估 你要放的电感/电容值

2. 用点点法去看趋势 组件先不要焊 用牙签固定在PCB上

切记不要用镍子去固定 因为镍子是金属 会影响阻抗

然后 Port1的铜管也不要焊 直接用点的方式 点在PA的输出Pin

(当然Port2要接50奥姆负载 这相信大家都知道 )

去看Smith Chart的走向趋势

当然这样量 不是很准确 但这只是看趋势

如果趋势是你想要的 你再来焊组件 焊铜管去量 都还不迟

如果趋势不是你想要的 就不要花时间去焊了 赶快换电感/电容值比较实际

还有 由你的图片看来

虽然你放这些电感值 阻抗位置没啥变

但收敛度却提升许多

在调收敛度时 通常会利用串小电感/并小电容的方式 来提升收敛度

由下图可知 这样的组合 其实阻抗根本是没啥变化的

但实际上 这对提升收敛度 却有一定的帮助

另外 量测跟仿真不准

还有一个因素 那就是你的RF频率

是否超过电感/电容的SRF

电容的等效电路与频率响应如下:

电感的等效电路与频率响应如下:

所以我们由上图可知

电感不是一直呈电感性 若频率超过SRF 就会变电容

电容不是一直呈电容性 若频率超过SRF 就会变电感

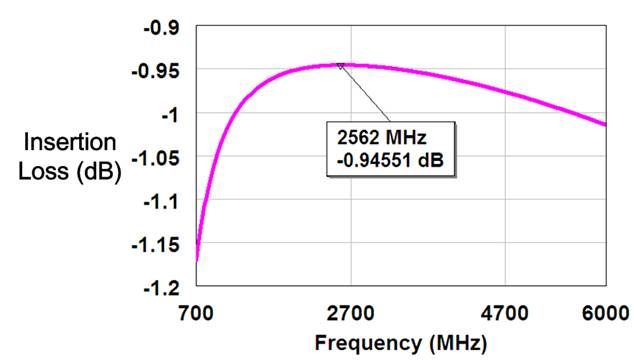

我们以串8.2pF电容为例 频率范围是700 MHz到6000 MHz

我们由上图可看到 其SRF为2562 MHz

换言之 当频率大于2562 MHz时 该电容会变电感

而由Smith Chart也证实这点

当频率小于2562 MHz时 此时是电容 确实就是按照串电容的趋势在走

但当频率大于2562MHz时 此时是电感 反而是按照串电感的趋势在走

而由上图也知 不管频率点为何 都会有电阻

这表示你只要串联组件 不管电容或电感

其内阻就是会造成讯号损耗

串8.2pF电容 内阻为11.5 Ohm Insertion Loss如下图:

所以如果想要使阻抗点有所较大的移动

尽可能不要用串联小P数电容的方式

因为电容值越小 其内阻越大 亦即Insertion Loss会越大

同理 你要使阻抗点有所较大的移动

尽可能不要用串联大n数电感的方式

因为电感值越大 其内阻越大 亦即Insertion Loss会越大

况且根据ZL = jwL的公式 L值越大 感抗越大

如此一来 其Insertion Loss会更大

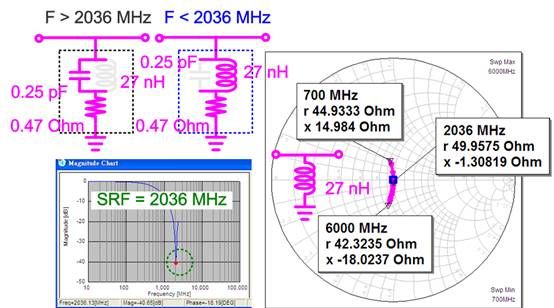

再以并27nH的电感为例

由上图可知 其SRF为2036 MHz

当频率小于2036 MHz时 此时是电感 确实就是按照并电感的趋势在走

但当频率大于2036MHz时 此时是电容 反而是按照并电容的趋势在走

当然 有些方案 并不是为了调阻抗位置 例如:

串大P数电容 => 在不影响阻抗情况下 当DC Block

串小n数电感 / 并小P数电容 / 并大n数电感 => 在不影响阻抗情况下 使阻抗收敛

而电容跟电感的SRF 都跟其值成反比

换言之

电容值越大 其SRF越低 越容易变电感性

电感值越大 其SRF越低 越容易变电容性

因此上述串大P数电容 跟并大n数电感的方案

是否会因

电容变电感性 电感变电容性

使得阻抗偏掉? 反而使阻抗难以预测?

答案是不会!

以串联100 pF的电容为例 当频率点超过SRF时

会变成电感在主宰

但实际上 即便是0.5nH的ESL在主宰 其阻抗依旧不动如山啊

再以并联100 nH的电感为例 当频率点超过SRF时

会变成电容在主宰

但实际上 即便是0.34pF的EPC在主宰 其阻抗依旧不动如山啊

因为其电容的ESL 或电感的EPC

多半都很小

因此串大P数电容 与并大n数电感

即便过了SRF

也顶多是变成串小n数电感 与并小p数电容

而这两个情况 不会剧烈改变你的阻抗

因此 串大P数电容 跟并大n数电感的方案

不管频率点为何? 有无过SRF 其阻抗都是不动如山的

但并大n数电感时 要特别注意

因为这是为了加强阻抗收敛用的

所以虽然不管频率点为何 其阻抗都是不动如山的

但若让频率点过了SRF 此时变电容性 那么可能收敛度会变差

而串大P数电容 当DC Block 则比较没这疑虑

因为不管频率点为何? 有无过SRF 都是有DC Block的功用

而有个特别案例 那就是Duplexer ANT端的落地电感

这是由于Duplexer的封装结构特性,会使其成电容性,

因此常看到Duplexer输出端,会摆放一颗落地电感,

来抵消其封装所造成的电容性,以加强其S11的收敛度,

亦即Duplexer的输出端,看出去需为一个电感性负载。如下图:

因此这颗电感 必须与Duplexer视为一体 不能以匹配组件来看待

所以该落地电感的值 必须遵照厂商的建议值 不能随便乱调

若值调大了 SRF往低频移动 可能会使频率点座落在SRF右边

此时呈电容性 那阻抗收敛程度会大为降低

若值调小 有可能因电感性不足以抵销其Duplexer封装所造成的电容性,

以至于阻抗收敛程度 依旧大为降低

所以不能随便乱调

至于小P数电容 与小n数电感 因为值小

所以SRF很大 频率点几乎只会在其SRF的左边

不会电容变电感 电感变电容

当然 而由以上分析可知 频率点越高 例如WiFi 5G

其频率点座落在SRF右边的机会越高

加上其PCB的寄生效应会更为严重

因此阻抗会更难预测

有没有具体操作,多谢大牛!

校准仪器还有射频线要做端口延伸,这样就会遵循那个规律

太牛逼的分析,学到了!

感觉小编描述的不太清楚,测量的是pa输出到测试座,但好像没说明动的是哪个位置的器件?另外矢网上的图是从那边看过去的?

pa输出到天线,你中间没加双工器?

太经典了

学习了。

点点法,应该是不错的方法