PA的前端匹配

Debug用的

1. 频率误差/相位误差, EVM, 调制频谱 => 减少反射 避免VCO Pulling

2. 传导杂散 => 设计低通滤波器 减少谐波

3. ACLR, 开关频谱 => 提升DA线性度

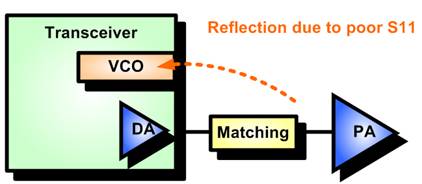

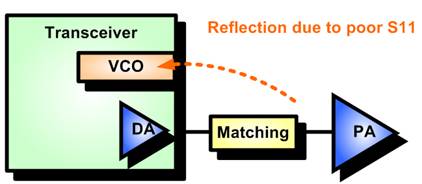

第一点 高通收发器 一向都是零中频架构 亦即RF频率等同于VCO频率

若这部分的匹配若没调校好,会因反射而干扰VCO,产生VCO Pulling

导致调变精确度下降,如下图 :

调变精确度下降 那就是频率误差/相位误差, EVM, 调制频谱

有可能会Fail 这时就要Finetune PA输入端的Matching

使其接近50奥姆 减少反射

而PA输入端的匹配电路,其摆放位置需依平台而定,

例如若为MTK的MT6252,则需靠近收发器,但若为高通的WTR1605L,则需靠近PA

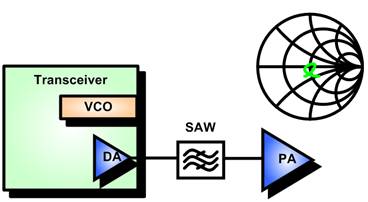

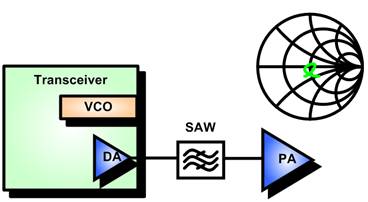

有时会遇到的问题是,将PA输入端的SAW Filter拔掉,其相位误差与EVM会变差,

此时可能有人会认为是SAW Filter的关系,但这是个误解,因为相位误差与EVM,都是带内噪声,

而SAW Filter是用来抑制带外噪声,换言之,SAW Filter无法改善相位误差与EVM,

相反地,若SAW Filter的Group Delay过大,会导致信号有所失真,进而劣化EVM。

因此合理的解释,便是VCO Pulling,当PA输入端放SAW Filter,

此时收发器看出去的S11很好,不会有讯号反射。

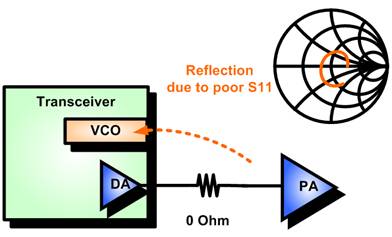

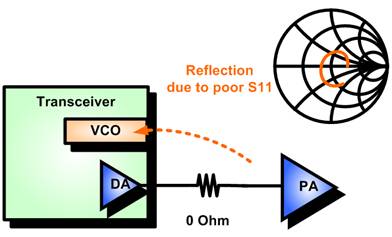

但是当PA输入端的SAW Filter拔掉时,其发射讯号由于Layout走线阻抗关系,

导致收发器看出去的S11不好,讯号反射打到VCO,使得调变精确度下降,

其相位误差与EVM变差。故此时应针对PA输入端的Matching再作微调,以减少反射。

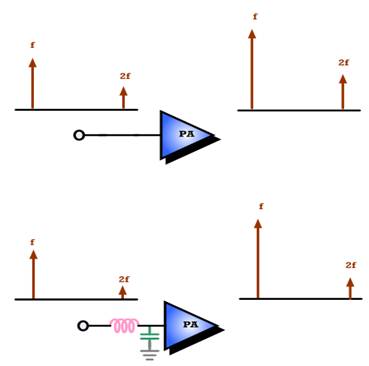

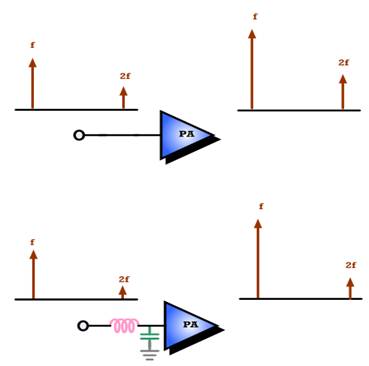

第二点 当RF讯号的谐波过大时,可在PA输入端,设计LC低通滤波器,

先抑制PA输入端的谐波,避免因PA的非线性效应,而使其更加恶化。

特别注意的是,不可将LC低通滤波器,设计在PA输出端,因为会动到Load-pull。

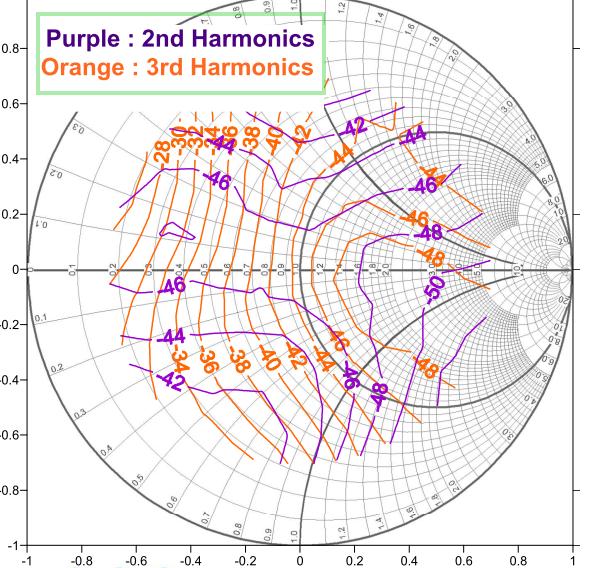

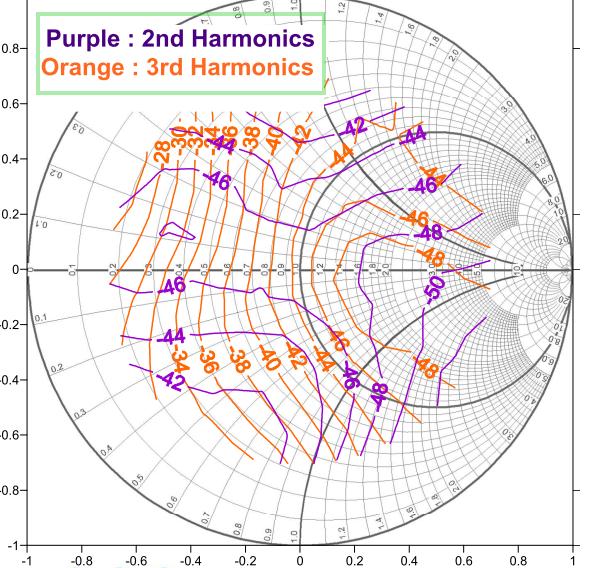

由上图可知,不同的Load-pull,会有不同谐波值,第二象限是高谐波区,

若该LC低通滤波器,使Load-pull跑到第二象限,进而导致谐波值变大,

那么该滤波器抑制谐波的能力,便大打折扣。

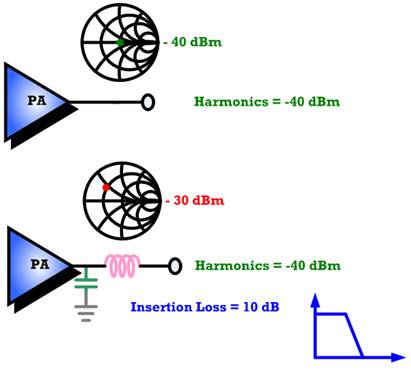

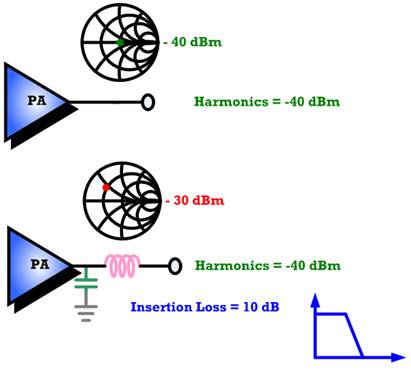

如上图,假设该滤波器,其谐波的Insertion Loss为10 dB,

但因更动了Load-pull,使其谐波增加了10 dB,

那么最终谐波会因其抵消结果,而并未所有抑制,

故若将LC低通滤波器,设计在PA输出端,那么该滤波器抑制谐波的能力,便大打折扣,

即便最终谐波仍获得改善,也会因Load-pull更动,而导致其他发射端的性能都劣化

第三点

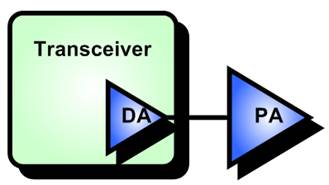

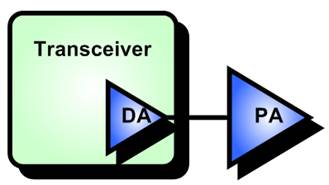

PA的输入端,其实也是DA(Driver Amplifier)的Load-pull :

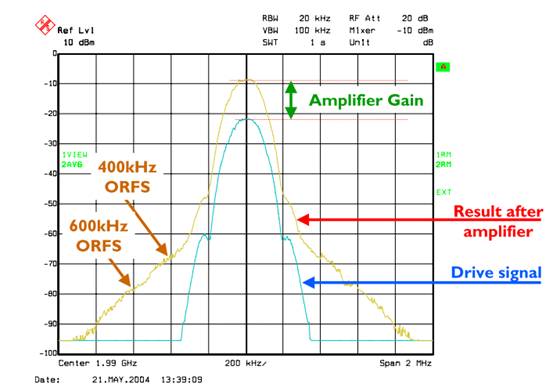

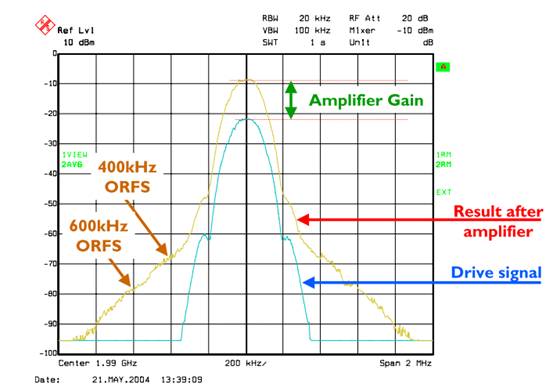

因此这部分的匹配若没调校好,会使DA的线性度不够,导致在PA输入端,开关频谱已偏高的情况发生,

再加上PA是主要的非线性贡献者,如此便会导致PA输出端的开关频谱更差。

当然WCDMA的ACLR 也是一样道理

因此PA输入端的ACLR不能太差,否则PA输出端的ACLR,肯定只会更差,

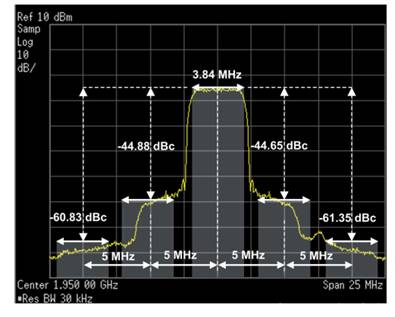

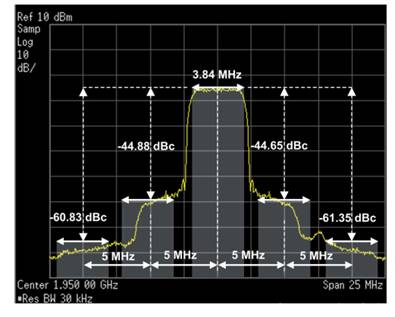

一线品牌大厂,其正负5MHz的ACLR,都要求至少-40 dBc,所以PA输入端

正负5MHz的ACLR 至少要 -50 dBc

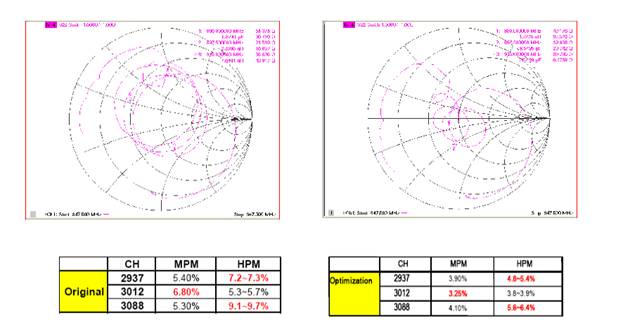

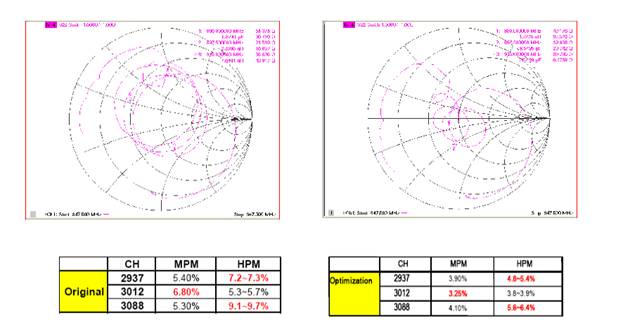

EVM也是 由下图可知,当PA输入端的Matching调校为较收敛的状况时,其EVM也跟着改善。

由于PA的输入功率范围一向很广,以RFMD的RF3225为例,其输入功率范围为0 dBm ~ 6 dBm,

这表示收发器的输出功率,即便扣掉Mismatch Loss与Insertion Loss,仍符合PA的输入功率范围,

因此一般而言,较少调校此处的匹配

PA输入端的Matching 多半都是Debug用的 因此会问这问题

通常都是考虑说 能否把PA输入端Matching拿掉 以节省空间?

由以上可以看出 若PA输入端走线阻抗控制做得够好 有收敛在50奥姆附近

理论上拿掉 是不至于出太大问题

当然 PA输入端Matching拿掉 就无法兜低通滤波器 来解传导杂散

不过若是高通平台 还可以靠调NV的方式来解

PA_Enable

ANT_SEL

V_ramp

这三条曲线 对于谐波以及开关频谱 都会有影响

建议PA_Enable比V_ramp早开启 而且最好能早一段时间

而Ant_sel可以比PA_en早开启 也可以比PA_en晚开启

看怎样的NV值 其谐波以及开关频谱会最低

前面提到 若PA输入端走线阻抗控制做得够好 有收敛在50奥姆附近

理论上其PA输入端的Matching可拿掉

而若PA没有内建DC Block 则PA输入端需摆放串联电容

重点来了 串联电容会使阻抗有所偏移,破坏原本已经控制好的阻抗

该如何处理呢 ?

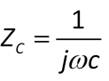

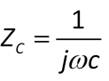

上式是容抗的公式,由上式可知,当电容值极大时,其阻抗会近乎于零。

而作阻抗匹配前,要先将落地组件拔除,且串联零奥姆电阻,来得知走线的原始阻抗,

因此可知串联零奥姆电阻,并不会改变原始阻抗。

而前述已知,电容值极大时,其阻抗会近乎于零,相当于零奥姆电阻,

故可知若想抵挡DC,但又不想使阻抗有所偏移时,可以摆放大电容,来同时兼具这两种需求。

然而这边所谓的大电容,并不需要到uF等级,因为uF等级的电容,至少都是0603的尺寸,

若摆放在走线,不仅占空间,同时也会因宽度与走线差异过大,产生很大的阻抗不连续,

以至于Mismatch Loss增加,如下图:

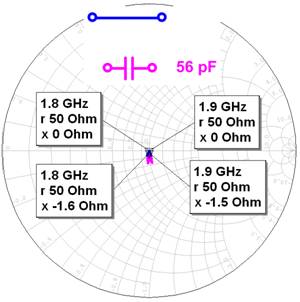

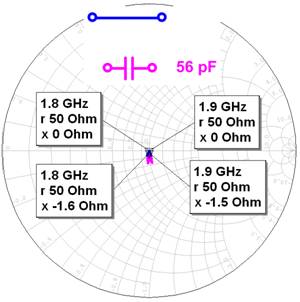

因此pF等级的电容即可,以DCS 1800/PCS 1900为例,

由下图可知,串联56 pF的电容,其阻抗几乎不变。

其他详细原理 可参照

在此就不赘述

各路大神有相关的资料分享一下么

盲调啊

万分感谢啊!学习了

“例如若为MTK的MT6252,则需靠近收发器,但若为高通的WTR1605L,则需靠近PA”

这个有点不明白,请教一下高手这是为什么啊

学习学习!

这位大神的资料很好,可以下下来看看

恩,发的很多帖子都不错!很有帮助!

学习了,不过好像现在高通新的平台已经没有了v_ramp,ant_sel这样的NV了,只能好好matching了~

嗯不错不错,,,

学习。

学习了~~~~~~~~~~

学习学习~~~~很不错

很经典啊,收藏了!

大神资料很多啊

讲解的真好,有时间再看看

VCO pulling是什么?新手求上路。

MTK6592最新参考设计资料。

可以加入 56592229 文件载!

讲解的真好,有时间再看看..............

请教一下各位大神,PA的输入匹配的作用是什么啊?若是没有网分匹配如何调试啊?谢谢了~

Debug用的

1. 频率误差/相位误差, EVM, 调制频谱 => 减少反射 避免VCO Pulling

2. 传导杂散 => 设计低通滤波器 减少谐波

3. ACLR, 开关频谱 => 提升DA线性度

第一点 高通收发器 一向都是零中频架构 亦即RF频率等同于VCO频率

若这部分的匹配若没调校好,会因反射而干扰VCO,产生VCO Pulling

导致调变精确度下降,如下图 :

调变精确度下降 那就是频率误差/相位误差, EVM, 调制频谱

有可能会Fail 这时就要Finetune PA输入端的Matching

使其接近50奥姆 减少反射

而PA输入端的匹配电路,其摆放位置需依平台而定,

例如若为MTK的MT6252,则需靠近收发器,但若为高通的WTR1605L,则需靠近PA

有时会遇到的问题是,将PA输入端的SAW Filter拔掉,其相位误差与EVM会变差,

此时可能有人会认为是SAW Filter的关系,但这是个误解,因为相位误差与EVM,都是带内噪声,

而SAW Filter是用来抑制带外噪声,换言之,SAW Filter无法改善相位误差与EVM,

相反地,若SAW Filter的Group Delay过大,会导致信号有所失真,进而劣化EVM。

因此合理的解释,便是VCO Pulling,当PA输入端放SAW Filter,

此时收发器看出去的S11很好,不会有讯号反射。

但是当PA输入端的SAW Filter拔掉时,其发射讯号由于Layout走线阻抗关系,

导致收发器看出去的S11不好,讯号反射打到VCO,使得调变精确度下降,

其相位误差与EVM变差。故此时应针对PA输入端的Matching再作微调,以减少反射。

第二点 当RF讯号的谐波过大时,可在PA输入端,设计LC低通滤波器,

先抑制PA输入端的谐波,避免因PA的非线性效应,而使其更加恶化。

特别注意的是,不可将LC低通滤波器,设计在PA输出端,因为会动到Load-pull。

由上图可知,不同的Load-pull,会有不同谐波值,第二象限是高谐波区,

若该LC低通滤波器,使Load-pull跑到第二象限,进而导致谐波值变大,

那么该滤波器抑制谐波的能力,便大打折扣。

如上图,假设该滤波器,其谐波的Insertion Loss为10 dB,

但因更动了Load-pull,使其谐波增加了10 dB,

那么最终谐波会因其抵消结果,而并未所有抑制,

故若将LC低通滤波器,设计在PA输出端,那么该滤波器抑制谐波的能力,便大打折扣,

即便最终谐波仍获得改善,也会因Load-pull更动,而导致其他发射端的性能都劣化

第三点

PA的输入端,其实也是DA(Driver Amplifier)的Load-pull :

因此这部分的匹配若没调校好,会使DA的线性度不够,导致在PA输入端,开关频谱已偏高的情况发生,

再加上PA是主要的非线性贡献者,如此便会导致PA输出端的开关频谱更差。

当然WCDMA的ACLR 也是一样道理

因此PA输入端的ACLR不能太差,否则PA输出端的ACLR,肯定只会更差,

一线品牌大厂,其正负5MHz的ACLR,都要求至少-40 dBc,所以PA输入端

正负5MHz的ACLR 至少要 -50 dBc

EVM也是 由下图可知,当PA输入端的Matching调校为较收敛的状况时,其EVM也跟着改善。

由于PA的输入功率范围一向很广,以RFMD的RF3225为例,其输入功率范围为0 dBm ~ 6 dBm,

这表示收发器的输出功率,即便扣掉Mismatch Loss与Insertion Loss,仍符合PA的输入功率范围,

因此一般而言,较少调校此处的匹配

PA输入端的Matching 多半都是Debug用的 因此会问这问题

通常都是考虑说 能否把PA输入端Matching拿掉 以节省空间?

由以上可以看出 若PA输入端走线阻抗控制做得够好 有收敛在50奥姆附近

理论上拿掉 是不至于出太大问题

当然 PA输入端Matching拿掉 就无法兜低通滤波器 来解传导杂散

不过若是高通平台 还可以靠调NV的方式来解

PA_Enable

ANT_SEL

V_ramp

这三条曲线 对于谐波以及开关频谱 都会有影响

建议PA_Enable比V_ramp早开启 而且最好能早一段时间

而Ant_sel可以比PA_en早开启 也可以比PA_en晚开启

看怎样的NV值 其谐波以及开关频谱会最低

前面提到 若PA输入端走线阻抗控制做得够好 有收敛在50奥姆附近

理论上其PA输入端的Matching可拿掉

而若PA没有内建DC Block 则PA输入端需摆放串联电容

重点来了 串联电容会使阻抗有所偏移,破坏原本已经控制好的阻抗

该如何处理呢 ?

上式是容抗的公式,由上式可知,当电容值极大时,其阻抗会近乎于零。

而作阻抗匹配前,要先将落地组件拔除,且串联零奥姆电阻,来得知走线的原始阻抗,

因此可知串联零奥姆电阻,并不会改变原始阻抗。

而前述已知,电容值极大时,其阻抗会近乎于零,相当于零奥姆电阻,

故可知若想抵挡DC,但又不想使阻抗有所偏移时,可以摆放大电容,来同时兼具这两种需求。

然而这边所谓的大电容,并不需要到uF等级,因为uF等级的电容,至少都是0603的尺寸,

若摆放在走线,不仅占空间,同时也会因宽度与走线差异过大,产生很大的阻抗不连续,

以至于Mismatch Loss增加,如下图:

因此pF等级的电容即可,以DCS 1800/PCS 1900为例,

由下图可知,串联56 pF的电容,其阻抗几乎不变。

其他详细原理 可参照

在此就不赘述

各路大神有相关的资料分享一下么

盲调啊

万分感谢啊!学习了

“例如若为MTK的MT6252,则需靠近收发器,但若为高通的WTR1605L,则需靠近PA”

这个有点不明白,请教一下高手这是为什么啊

学习学习!

这位大神的资料很好,可以下下来看看

恩,发的很多帖子都不错!很有帮助!

学习了,不过好像现在高通新的平台已经没有了v_ramp,ant_sel这样的NV了,只能好好matching了~

嗯不错不错,,,

学习。

学习了~~~~~~~~~~

学习学习~~~~很不错

很经典啊,收藏了!

大神资料很多啊

讲解的真好,有时间再看看

VCO pulling是什么?新手求上路。

MTK6592最新参考设计资料。

可以加入 56592229 文件载!

讲解的真好,有时间再看看..............

相关文章:

- DCS相位误差前端偏大(05-08)

- 手机接收机前端的LNA的可控原理(05-08)

- 泰景模拟电视前端电路(05-08)

- 求助:GSM双频PA,发现900工作时1800有东西输出,而且前端开关抑制不住!(05-08)

- 有谁了解RFaxis,其前端芯片有市场吗?(05-08)

- 一个wifi前端的问题(05-08)