关于RX线下面的GND挖空的问题

为了控制阻抗, 挖了的走线那么粗

你的意思是如果走线也挖的话,为了保持阻抗,线宽就要拓宽?走线就会变的很粗是吧?

对,太粗的线IC pin脚进不去

学习。

那还请教您一下,这个参考地怎么算?挖空的部分参考L3,没挖的参考L2?是这样的吗?

我觉得你的问题问的不清楚吧 你是想说0402器件下挖掉 然后走线下挖掉是为什么?我们的项目一般走线下是挖的 线宽4mil

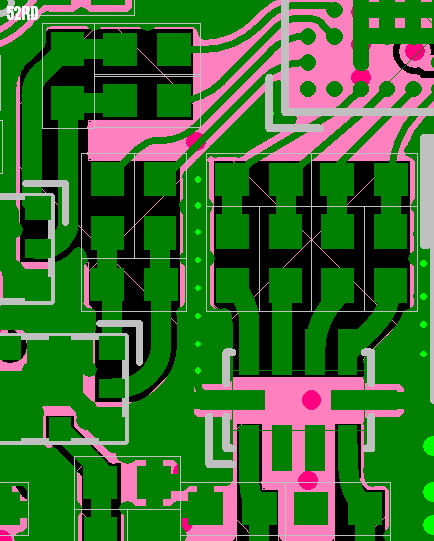

我问的是为什么0402下面挖掉,而走线不挖?我们目前的PCB就是我发的图片,只挖了0402期间下面的GND,线路到BGA的线下面的GND没有挖

就是阻抗控制。不要想着0402,要想着0402的那么粗的线,参考第二层该是多少阻抗,挖地只是权宜。

RX设置好规则3倍线宽间距则可(目的降低损耗),挖空不挖空无所谓

BALUN-SAW底下以及附近一些匹配网络要挖空,这里其实0402的艰巨已经够大,理论上挖空作用不大,但为什么要挖空呢?其实主要不是插损,是因为balun-saw的pad点到周围0402 R/L元件的pad通常会摆件摆得非常靠近(这里器件聚拢到一起会获得更好的SAW的滤波匹配),这样板厂在制作上会碰到两pad之间阻焊层宽度小于最小加工间距的问题,于是工厂会要求keepout(如PCB不做keepout工厂有时候也会强制keepout)

静待高手...........

小编自问自答

都是高人

表达复杂了吧,我的做法是SAW前端(既PA到SAW端)是要做50 OHM阻抗,然后下层线挖不挖是你自己的决定,你不挖,阻抗线参考第二层,线宽一般4MIL左右,你挖掉参考第三层地,线宽一般12MIL,这个只要能控制好阻抗既可。SAW到IC端一般是控制75到150 OHM之间。因为是差分线,统一线宽的。一般你的间距和线宽及参考地达不到要求,一般工厂是很难做到的,你发的图片竟然SAW到IC端搞了两种线宽出来。我理解不了。不知道这个LAYOUT怎么想的。

相关文章:

- 主板上RX接收部分第2层没有挖空对Pathloss的影响(05-08)

- 晶振上下两层为什么挖空,且不能走线(05-08)

- layout时RF屏蔽框内是要铺地还是要挖空?(05-08)

- Rx部分走线为什么要挖空(05-08)

- 测试RX BER 灵敏度的问题。高人看看(05-08)

- 请教Rx-Level的两个指标(05-08)