谐波点的传导与什么有关系?

几个方向 :

1. 降Power 这是最简单的

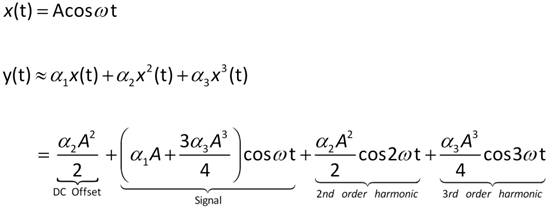

由上图可知 谐波是来自于组件的非线性效应 当然PA是最可能

同时也可看出 主频Power降了 其谐波也会跟着降

依我经验 主频降个0.5 dBm 二阶谐波大概就会差个2~3 dBm

当然三阶的就降更多了

假设GSM 850/EGSM 900在PCL5的Target Power为32.5 dBm

可以调NV或DAC 降成32 dBm试试

2. 若是高通平台 可以调NV

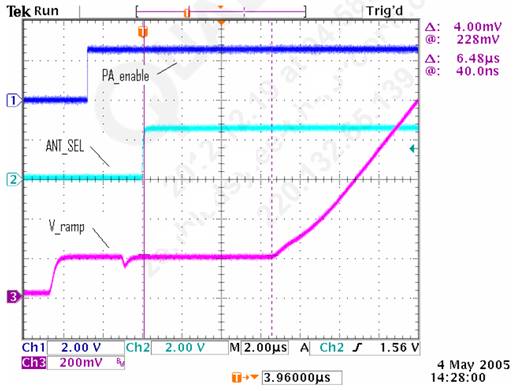

下图是PA_Enable、ANT_SEL、V_ramp三条曲线。

这三条曲线,对于谐波以及开关频谱,都会有影响,

建议PA_Enable比V_ramp早开启,而且最好能早一段时间。

而Ant_sel可以比PA_en早开启,也可以比PA_en晚开启,看怎样的NV值 其谐波以及开关频谱会最低。

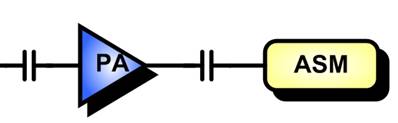

3. 检查DC Block

由第一点的图可知 DC Offset也是非线性效应之一

若流入PA跟ASM 会使其线性度下降

除非是PA跟ASM已有内建DC Block 否则PA的input跟output

都要摆放DC Block 检查一下是否有放

4. 在PA输入端 就将谐波砍掉 避免因为PA的非线性效应

使其谐波更加恶化 但这要看PA input的摆放零件

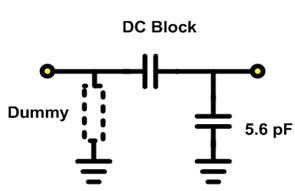

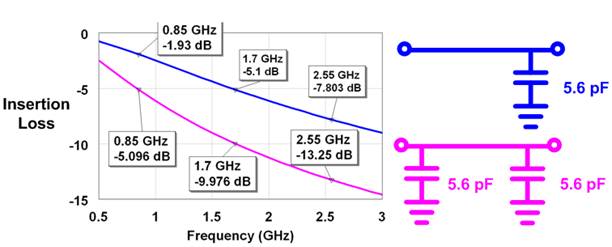

假设PA input只放一个串联的DC Block

那你只能自己额外放一个落地电容来砍谐波

以GSM 850为例 可以放一个5.6 pF的落地电容

由上图可以看到 对于二阶谐波 大概有5 dB的insertion Loss

对于三阶谐波 大概有8 dB的insertion Loss

特别注意的是 在设计电容值时 不是谐波抑制能力越大越好

因为一般普通的COG电容 其频率响应 不会只砍到谐波

同时也会砍到主频 假设放10 pF的落地电容

可以看到二阶谐波 大概有16 dB的insertion Loss

三阶谐波 大概有22 dB的insertion Loss

但主频也被砍了5 dB 另外落地电容会使阻抗偏掉

换句话说 会有Mismatch Loss 在这情况下 10pF的落地电容

其insertion Loss跟Mismatch Loss加一加

可能会使主频的讯号过低 甚至低于PA输入范围的下限

同时我们也看到 虽然三阶谐波的抑制能力更好

但三阶谐波的频率 已座落在谐振频率的右边

换言之 此时是利用该落地电容的电感性去砍三阶谐波

把电容当电感用 某种程度上会有一些未知的风险 最好是极力避免

而前述的5.6 pF落地电容 其二三阶谐波都座落在谐振频率的左边

同时主频只被砍了2 dB 即便加上阻抗偏掉造成的Mismatch Loss

原则上都还在PA输入范围内

况且砍一些主频的能量 跟方法1的降Power有相同意义

可以更降低PA的非线性效应

所以在设计落地电容时

可以砍主频 但不要砍太多 至少要确保加上Mismatch Loss后

都还在PA输入范围内

同时最好确保其谐波频率 都座落在谐振频率的左边

5. 承第4点 若PA input摆放π型 那原则上只能串联DC Block

然后再摆一颗落地电容

若同样以GSM 850为例 那就是只摆一颗5.6 pF的落地电容 另一个落地组件不上件

倘若另一个落地组件也上5.6 pF 则主频会被砍过多能量

由上图可知 若摆放两个5.6 pF的落地电容 主频会被砍5 dB

前述已说过 不是谐波抑制能力越大越好 还要考虑到主频会不会衰减过大

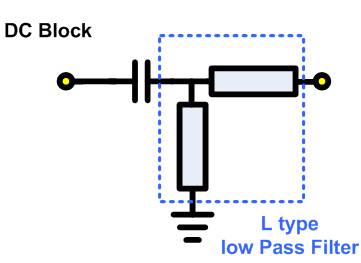

6. 若PA input摆放T型 那就是DC Block加L型低通滤波器

而其低通滤波器 建议用LC 不要用RC

因为绕线电阻具有很强的电感性, 其寄生电感容易使系统不稳定,

因此不可用于对频率敏感的应用中,例如RF走线

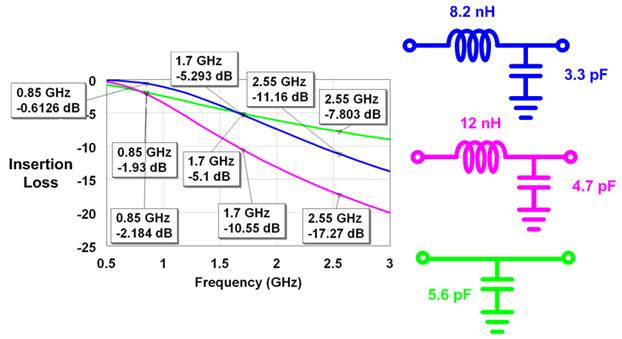

由上图可知 以5.6pF的落地电容来做比较 如绿色曲线

若采用(8.2nH + 3.3pF)的低通滤波器 如蓝色曲线

其2阶谐波的抑制能力差不多 3阶谐波的抑制能力多了3dB

但主频只衰减了0.6 dB

若采用(12nH + 4.7pF)的低通滤波器 如粉红曲线

其主频衰减量差不多 但2阶谐波的抑制能力多了5 dB

3阶谐波的抑制能力多了9 dB

这表示相较于单一颗落地电容 其LC低通滤波器的设计上可以较为弹性

同时效果更好

同样的主频衰减量 但谐波抑制能力更好

或是同样的谐波抑制能力 但主频衰减量更小

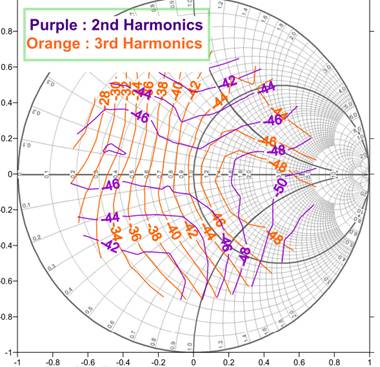

7. Finetune PA Load-pull

由上图可知 不同的Load-pull 会有不同的谐波值

以上图为例 谐波最低处 是位于第四象限

因此可以将PA的Load-pull Finetune在第四象限

但PA的Load-pull一但更动 其他Tx的性能也会跟着变动

所以前述的落地电容 或低通滤波器 设计在PA输入端

道理在此 因为怕动到PA的Load-pull

而若Finetune后的Load-pull 救了传导杂散 但其他测项Fail

那就得不偿失 而50奥姆的Tx性能 虽不是最好

但在输出功率 谐波 耗电流……等表现上

大致上还可以接受 所以一般都是Finetune在50奥姆

因此若真要Finetune 顶多是使其更接近50奥姆

除非万不得已 再来考虑是否要Finetune在谐波最低处

同时要确认其他的Tx测项 是否会因此Fail

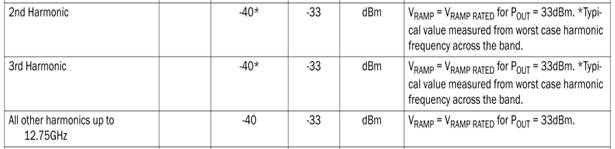

8. 换PA

如上图所示 一般PA的datasheet 会有谐波的量测值

因此可以换个pin-to-pin但谐波较小的PA

但同第7点 如此一来 其他Tx的性能也会跟着变动

等于Load-pull要重调 Tx测项要重新测试

若新PA救了传导杂散 但其他测项Fail 那就得不偿失

况且现今平台 多半已使用MMPA

亦即GSM/WCDMA/LTE的Tx性能 通通受影响

影响层面极大 因此除非真的解不掉 再来考虑这步

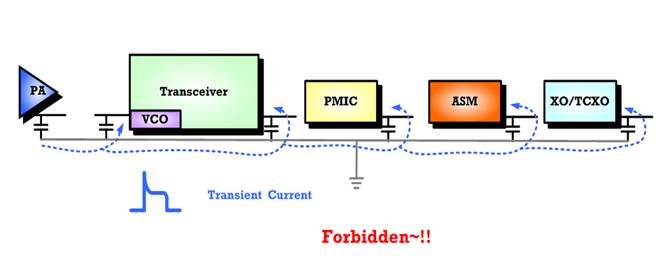

9. 电源方面

假设收发器或PA的电源 稳压不好 或有IR Drop 或载有高频噪声

都会使Tx性能劣化 当然也包含传导杂散

因此可以先针对收发器跟PA 同时额外供电

倘若问题依旧 那原因就不是出在电源

若问题改善 那就看问题是出在PA的电源 还是收发器电源

一般是出在PA电源居多

稳压方面的话 就加大其电容值 因为电容值越大 其ESR越小 稳压效果越好

而高频噪声的话 则是看电源走线附近

有无高速讯号走线 或RF走线

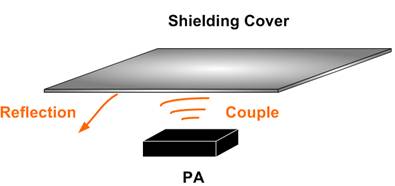

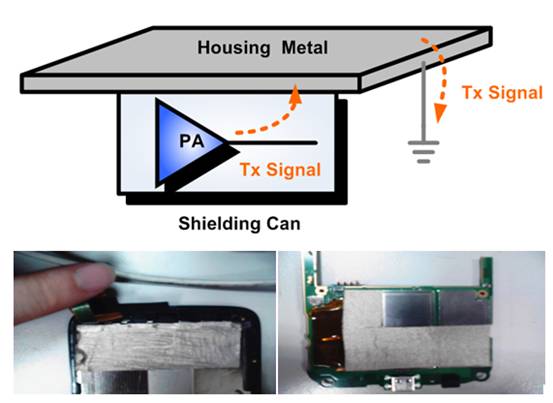

最常见到的情况是 Shielding Cover盖上去后,其传导杂散变大,

而这来自PA的机会较大,如下图 :

因为PA的能量本来就很大,加上体积较大,离Shielding Cover更近,

所以这表示PA耦合到Shielding Cover的能量同样很大,

若Shielding Cover接地良好,原则上PA耦合到Shielding Cover的能量,会通通流到GND,

但若Shielding Cover与Shielding Frame的接触不够好,

那么PA耦合到Shielding Cover的能量,有一部分会反射,

若是打到PA电源,使PA电源上载有RF高频噪声

那传导杂散就会劣化。

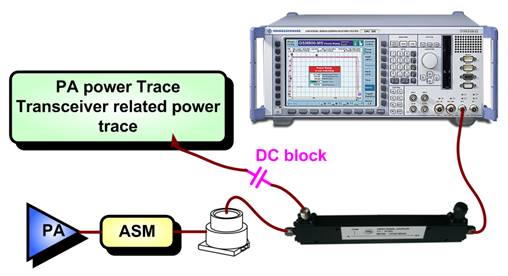

此时可以做实验,去验证是否PA输出讯号打到上述走线,如下图 :

记得要加DC Block,避免电源的直流讯号,回灌到CMU跟PA,

原则上这样的实验,其发射性能是一定会劣化,

但要观察是否为Shielding Cover盖上去后的现象,

倘若同样的现象完全复制出来,才可判定Root Cause是PA输出讯号打到电源走线,

例如Shielding Cover盖上去后,其传导杂散会Fail,但相位误差依然Pass,

而上述实验却是传导杂散跟相位误差都Fail,那就不能证明是PA输出讯号打到电源走线。

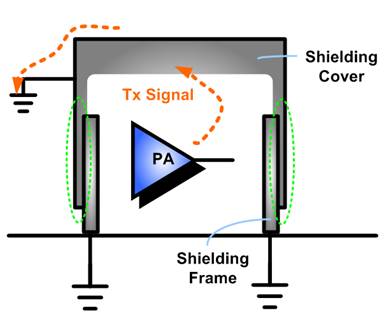

而若证明出来 确实是Shielding Cover盖上去后,PA输出讯号打到电源走线

那么可透过加强Shielding Cover与Shielding Frame的接触,

以及加强Shielding Cover与Housing金属的接触,

使其耦合到Shielding Cover上的发射讯号,通通流到GND

10. Layout方面

检查一下稳压电容跟bypass电容 是否离PA过远

若离过远 那么即便你加大稳压电容的值

或是找出高频噪声的频率点 其稳压跟滤波的效果

也会不如预期 如下图

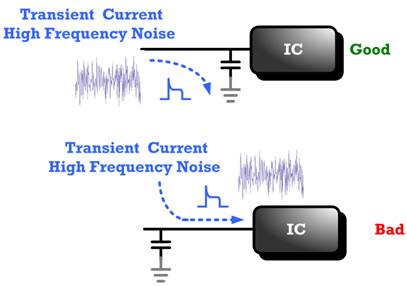

而稳压电容需直接下到Main GND,

便是避免已流到GND的瞬时电流,透过共同的GND,又再流入上述的IC中,

尤其是PA稳压电容,绝不能与其他IC的稳压电容表层一起共地,

否则全都会受瞬时电流影响 如下图 :

至于IR Drop 那就是在PA操作时 量一下电压 看跟预期的相差多少

若相差太多 那就是Layout改版时 电源走线要短一点 线宽宽一点

若是有穿层 记得Via要多打

11. 检查PA是否在架桥下

前述提到,若作了第9点 Coupler回灌PA输出的实验,

但现象却与Shielding Cover盖上去的现象不一致,

那就不能证明是PA输出讯号,打到上述走线。

那么Shielding Cover盖上去后 其传导杂散劣化现象

可能是来自于Shielding Cover与PA内部Bond Wire的寄生效应,尤其是Shielding Frame的架桥,

因为相较于Shielding Cover,其架桥的高度又更小,

当Shielding Cover盖上去后 会再更进一步压缩PA与架桥的距离

倘若PA刚好在架桥下方, 那寄生效应会很大,其PA的特性可能会有所改变,导致发射性能劣化,

若问题是来自寄生效应,

那么就是Shielding Cover的高度,以及架桥的位置,要重新调整,

再不然就是PA上方的Shielding Cover,直接破孔开天窗。

所以Placement时,PA尽量不要在架桥跟Shielding Frame的屋檐下方,避免寄生效应。

原则上建议按照上面的顺序

Debug时 永远都是简单的实验先做

那种劳师动众的实验 万不得已 放到最后再做

其他详细原理 可参照

在此就不赘述

给力啊顶!

相关文章:

- GSM 谐波滤波器(05-08)

- 谐波问题请指教(05-08)

- DCS1800二次和三次谐波超标(05-08)

- RF4180的二次谐波问题(05-08)

- DCS二次谐波余量只有3.3dB,怎么调整(05-08)

- GSM900的二次谐波出问题,请教各位大侠(05-08)