关于GARDNER同步环路在FPGA中实现的延时

12-30

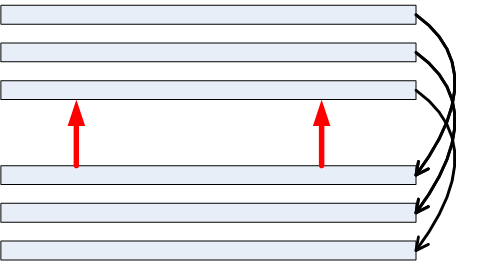

如图,并行算法下,由于TED、LP、NCO都会有延迟,当前并行计算得到的插值变量必然不会送给紧邻的下一次并行计算过程使用,这个延迟对算法的最终实现有影响吗?在这种延时存在的情况下,算法最终能趋近到正确的结果吗?

麻烦了解的朋友指点下,谢谢了~

gardner算法本身环路里就有一个延迟单元吧,loop filter吧。

不是吧,在matlab里面仿真时没有延时的。loop filter只是一个P+I结构,对每次计算没有延时啊

环路肯定有延时的.最后的收敛情况,请查看gardner写的锁相环那本书吧.

相关文章:

- 请教一些关于设置数字锁相环的环路参数的方法,谢谢!(05-08)

- 做载波相位同步的看过来(05-08)

- 请问谁有关于DA和AD变换采样同步算法的文章(05-08)

- 弱弱的问,同步和异步cdma的区别是什么(05-08)

- 问一个OFDM的同步问题(05-08)

- 问一个入门问题,什么是异步数据信道和同步数据信道?(05-08)

射频专业培训教程推荐