CST discrete port 疑问

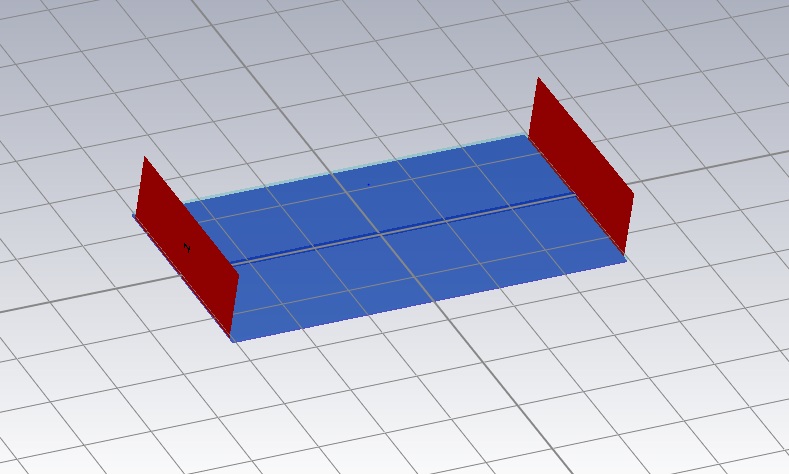

因为我以前主要用HFSS,很自然把CST waveguide port和discrete port的区别联想到HFSS中waveport和lumped port的区别,所以建了一个简单的两端口微带线模型来验证,模型如下(boundary都是open and add space):

图1 模型

我分别使用两种端口对70欧姆(w=0.05),50欧姆(w=0.1),25欧姆(w=0.26)的微带线进行了仿真,两种端口的仿真结果如下:(介电常数3.4,损耗0.002,金属电导率5.8e+7)

图2 waveguide port仿真结果

waveguide port的结果和我预想的一致,和HFSS waveport一样,该port在端口处无反射,对于不同阻抗的微带线匹配都很好,损耗很小。

图3 图4 discrete port 仿真结果

但是discrete port的仿真结果与我预想的差别很大。discrete port设置成50欧姆阻抗,所以对于70欧姆和25欧姆的传输线会有反射,但是对于50欧姆的传输线应该是匹配的,其结果应该会与waveguide port的结果相近,但是实际结果却相差很多。

我的疑问是,对于特性阻抗为50欧姆的微带传输线,为什么CST用两种端口的仿真结果差别这么大?到底哪一个是准确的?

(在HFSS中我做过类似的仿真实验,其结果是对于50欧姆传输线,waveport和lumped port结果是基本一致的)

谢谢!

知道何谓归一化吗?

还请告知一下介电常数为3.4的介质厚度是多少?

你可以用CST内 micro--->calculate--->calculate analytical line impedance--->Thin microstrip计算一下以介电常数为3.4的做介质的微带线中(固定介质高度),70/50/25ohm,对应的微带线线宽是多少,感觉0.05,0.1,0.26会有一些出入。

我想小编的意思是,如果微带线是50欧姆,设置离散端口(阻抗=50)和波导端口结果应该是一样的?

用的是flex软板,厚度50um,宽度是用微带线工具算过的。谢

对的,但是仿真差别挺大,不知问题出在哪里

在我这个仿真模型中的归一化不是太明白,愿闻其详,谢。

归一化: 以端口阻抗为主。

波导端口: 以物件(微带线或是任何物件_obj的阻抗为主。)

所以、若是不做归一化处理,波导端口呈现的阻抗,将随着物件_obj的阻抗而变。

你好,我的理解是波导端口不做归一化处理,所以对于不同阻抗的微带线都是匹配的,这和仿真结果一直。但是能解释一下为什么和50欧姆的discrete port仿真结果不一致吗?谢谢

Waveguide ports represent a special kind of boundary condition of the calculation domain, enabling the stimulation as well as the absorption of energy. This kind of port simulates an infinitely long waveguide connected to the structure. The waveguide modes travel out of the structure toward the boundary planes thus leaving the computation domain with very low levels of reflections.

Very low reflections can be achieved when the waveguide mode patterns in the port match perfectly with the mode patterns from the waveguides inside the structure. CST MICROWAVE STUDIO uses a 2D eigenmode solver to calculate the waveguide port modes. This procedure can provide very low levels of reflection below -100dB in some cases.

-----------------------------------------------------------------

the discrete ports offers another possibility to feed the calculation domain with power. Three different types of discrete ports are available, considering the excitation as a voltage or current source or as an impedance element that also absorbs power and enables S-parameter calculation.

**这是CST of Help的内容,不是我创新的。

问题还没有解决,希望不要沉下去。50欧姆微带线为什么两种端口差距这么大?仿真类似微带结构时应该用哪种端口准确些?谢谢。

离散端口在高频就是会和波导端口的结果不一致的。离散端口在高频时端口失配的问题会越来越明显,我估计是离散端口中两根wire引入的寄生电感效应。不知道你用的是edge port还是face port?

可能face port会好一些?或者看看有没有deembedding选项?HFSS的集总端口里有这个功能,CST里不知道是否有?

你好。你指的wire是什么?金线?我这个模型中没有。

CST中离散端口没有deembed功能,波端口才有。

不清楚edge port和face port是什么,我去研究下。

谢谢。

就是下面截图中离散端口里的两根蓝色的直线,实质上是两根理想的PEC导线,当频率很高时,它们的寄生电感效应就会变得越来越明显,从而导致端口失配,CST的离散端口分为edge port(线激励源,就像截图中的)和fac eport(面激励源)。

十分感谢你的回复。

很有启发,我去研究下edge port和face port。

在HFSS中应该没有这种现象,两种端口在高频基本还是吻合的。

你在HFSS里试试看:把lumped port的宽度改的足够细,尽量接近CST里离散端口的edge port形式,看看是否有变化?不过CST里的离散端口中真正的激励源是中间的那个三角形,而HFSS里的lumped port从某种意义上说还是一个近似的主模,所以感觉两者还是不一样的。

有什么结果分享一下给我哦,我也正好学习一下,呵呵!

十分感谢你的回复。

仔细看了下CST的help。里面说的挺明白了,和你的意思一样。

edge port会加入一个金属wire,face port会加入一个PEC的sheet,这样在高频时就会造成失配,影响结果。help文档里也说waveguide port更精确,discrete port推荐低频时使用。(低频的一种定义是金属wire长度小于十分之一波长)。

关于HFSS端口的实验我回去试一下再给你答复。

以微带线为例对不同尺寸的集总端口进行了仿真。

CST使用face port且port宽度和微带线一致时匹配最好,高频性能也最好。

HFSS情况一致,但是改变port宽度时S参数变化没有CST那么大。

嗯,学习了,非常感谢哈!

我觉得主要原因还是激励 的场型不一样,DP是电源激励,激励出来的场相当于一个偶极子天线,而WGP是波导激励,激励出来的是相应波导的模式场,S参数是通过波导模式定义的,所以WGP计算的S参数更准,而DP只有在距离很短的时候场才和TEM波的场相似,所以DP算S参数要距离很短,而且只能是TEM波

小编,可以去CST China的官网上看一下,里面两周一题有提到这个方面的知识。

离散端口的误差确实比较明显

谢谢你的回复。

和cst工程师沟通过了,DP不准原因原因:1.金属线带来的失配和辐射(失配可以通过Deembed去嵌) 2. 你所说的模式问题,DP没有场模式的概念,只是电压电流。

结论:频率高时用waveguide port

高频低频怎么界定?

我的经验是一般几个GHz可以用DP,10GHz以上尽量用WP。当然也和PCB厚度有关系。

你可以試試看用HFSS打lump port試著去比較

相关文章:

- CST MICROWAVE STUDIO (05-08)

- cst里面怎么画螺旋曲线啊? (05-08)

- cst仿真错误提示,请求帮助 (05-08)

- cst中这样的警告是什么原因导致的? (05-08)

- 请问cst对硬件要求高吗? (05-08)

- 我装cst出了问题 (05-08)