CST MWS关于缝隙屏蔽效能的疑问

05-08

最近整理仿真数据,发现在一个矩形机型上开两条缝,随着两条缝的间距增大,屏蔽效能SE反而减小,这个应该怎么解释呢?感觉应该是随着间距增大,缝隙耦合减小,因此屏蔽效能增大呀。希望大家给予指导,谢谢!

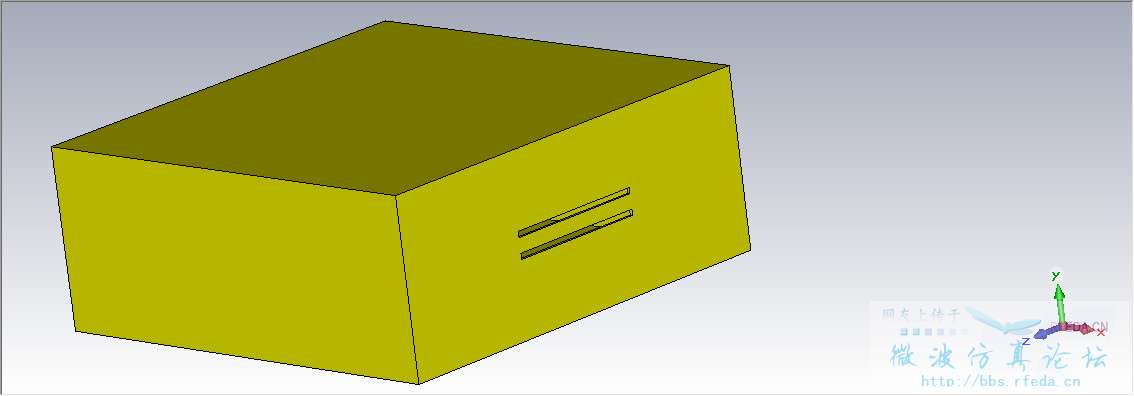

大概就是长这样,两个缝隙距离变化

大概就是长这样,两个缝隙距离变化

探针在哪,什么频段,机柜尺寸,孔缝尺寸?

探针就在机箱中心

0-1GHz之间都是这个规律

机箱尺寸300*300*120(这是外尺寸,厚度2mm)

缝隙100*4

1. ,如果不是腔体,换成一块挡板,确实两个缝间距越大,探针处的合成场强变小,但是这是在腔体环境下,要考虑其中的模式场型,就不一定是这样的规律了

2. 最重要的是这个频段内 这个尺寸的孔缝,形成的截止波导,1GHz的电磁波肯定是凋零模了,能透进去的电磁波很小,-30dB的仿真精度肯定不够,应该先考虑仿真结果的准确性吧

3. 就算电磁波进去了,而且仿准了,探针处的场肯定非常小,这时候这个规律说服性就会小很多

4. 1GHz下这种腔体 SE肯定好得很,差个几dB 甚至10几dB 都应该无所谓

综上,要想考察你说的规律是否正确

1. 别用腔体 就一块空板 开两条缝

2 仿真SE的话 要吗加大缝隙尺寸,要吗加大仿真频带宽度

非常非常感谢!我用的仿真精度是-80dB的,按照相关文献仿的几个结果是重合的。1GHz之内确实SE普遍都还不错,但也有一个谐振点存在,周围SE就很差了。感谢热心人!

相关文章:

- 关于CSTMWS做机箱屏蔽效能 (05-08)

- CST MS工作室机箱屏蔽效能仿真 (05-08)

- CST仿真屏蔽效能问题 (05-08)

- CST MWS计算机箱屏蔽效能,两个不同的工程计算出的数据能进行对比吗? (05-08)

- 在CST MS中如何计算金属箱的屏蔽效能? (05-08)

- CST屏蔽效能仿真材料设置 (05-08)

射频专业培训教程推荐