硅基片上分形电感设计技术研究

05-08

1 引言随着无线通信技术的发展,传统的通信频段已经不能满足人们对通信传输速率日益增长的需求,无线通信开始向毫米波频段扩展。目前毫米波集成电路已应用到汽车雷达与无线局域网等工业方面,在医学、安检和天文等领域已有高达170 GHz 的应用[1]。

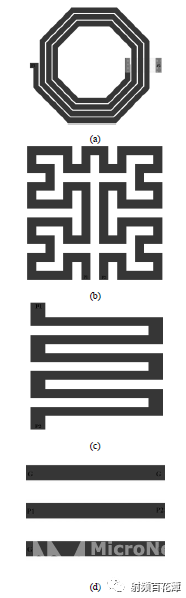

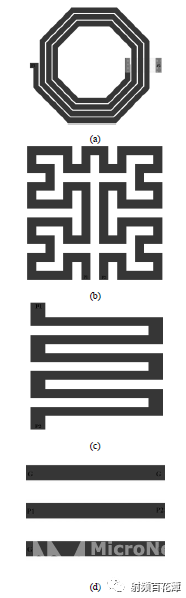

绝大多数毫米波集成电路都采用III-V 族等特殊材料和工艺制作,成本较高,这限制了毫米波电路的普及。硅基毫米波的研究起始于2000 年左右,随着深亚微米和纳米工艺的日趋成熟,设计实现毫米波CMOS 集成电路已经成为可能,有望大幅度降低毫米波集成电路的成本。绝大多数毫米波集成电路都采用III-V族等特殊材料和工艺制作,成本较高,这限制了毫米波电路的普及。硅基毫米波的研究起始于2000 年左右,随着深亚微米和纳米工艺的日趋成熟,设计实现毫米波CMOS 集成电路已经成为可能,有望大幅度降低毫米波集成电路的成本。2 片上电感分析片上电感广泛地应用于低噪声放大器、功率放大器、混频器、功率分配器和移相器等集成电路中。毫米波频段波长很短,电路具有极小的尺寸,电路所需电感值一般为数十皮亨,远小于射频电路所需的电感值。这样可以缓解电感面积对芯片尺寸的制约,同时为分形电感[2]、绕组电感[3-4]及传输线型电感[5]等新型片上电感设计带来机遇(如图1 感[5]等新型片上电感设计带来机遇(如图1 所示)。另一方面,片上电感在毫米波频段的结构、损耗机制和性能等方面都与低频段存在很大的差异,片上螺旋电感的趋肤效应、邻近效应、涡流效应及衬底耦合效应等各种寄生效应会变得更加严重[6],这增加了毫米波片上电感的设计。缺乏高性能片上电感成为制约集成电路发展与高性能芯片系统实现的主要瓶颈之一[7]。

绝大多数毫米波集成电路都采用III-V 族等特殊材料和工艺制作,成本较高,这限制了毫米波电路的普及。硅基毫米波的研究起始于2000 年左右,随着深亚微米和纳米工艺的日趋成熟,设计实现毫米波CMOS 集成电路已经成为可能,有望大幅度降低毫米波集成电路的成本。绝大多数毫米波集成电路都采用III-V族等特殊材料和工艺制作,成本较高,这限制了毫米波电路的普及。硅基毫米波的研究起始于2000 年左右,随着深亚微米和纳米工艺的日趋成熟,设计实现毫米波CMOS 集成电路已经成为可能,有望大幅度降低毫米波集成电路的成本。2 片上电感分析片上电感广泛地应用于低噪声放大器、功率放大器、混频器、功率分配器和移相器等集成电路中。毫米波频段波长很短,电路具有极小的尺寸,电路所需电感值一般为数十皮亨,远小于射频电路所需的电感值。这样可以缓解电感面积对芯片尺寸的制约,同时为分形电感[2]、绕组电感[3-4]及传输线型电感[5]等新型片上电感设计带来机遇(如图1 感[5]等新型片上电感设计带来机遇(如图1 所示)。另一方面,片上电感在毫米波频段的结构、损耗机制和性能等方面都与低频段存在很大的差异,片上螺旋电感的趋肤效应、邻近效应、涡流效应及衬底耦合效应等各种寄生效应会变得更加严重[6],这增加了毫米波片上电感的设计。缺乏高性能片上电感成为制约集成电路发展与高性能芯片系统实现的主要瓶颈之一[7]。

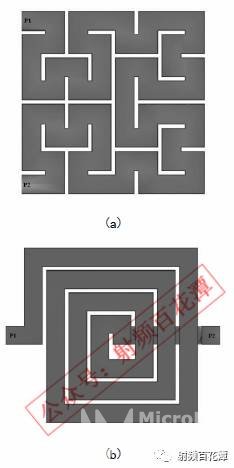

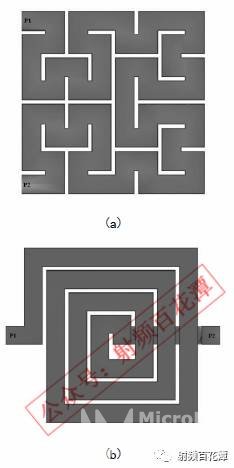

图1 不同类型片上电感版图结构:(a)螺旋电感;(b)分形电感(三阶Moore 形电感);(c) 绕组电感;(d) 传输线电感片上电感一般由金属线和衬底构成,提高其性能可以从下面两个方向进行设计:第一个方向是改进元件工艺。包括采用电阻率低的金属作为元件环绕材料;采用高电阻率的衬底减小衬底寄生效应;采用厚氧化层或微机电系统工艺悬空金属过线来提高螺旋元件性能;采用硅通孔技术 [8]、纳米磁性材料、铁氧体材料和新型磁介质结构设计[9-11]使片上电感由二维到三维结构转变,增加器件磁通量。这种类型元件性能提高方法不能与传统CMOS 工艺相兼容。另一个方向是在现有CMOS 工艺基础上通过版图优化设计提升元件性能。通过多路径技术能够抑制趋肤效应与邻近效应,采用过孔把多层金属线相连能够增加金属线厚度,提高元件品质因数 [12];采用内外圈金属宽度渐变的设计方法,能够降低邻近效应与趋肤效应对电感品质因数的影响;采用屏蔽层能够减小衬底损耗等等。分形电感的设计越来越引起人们的关注,分形是这样一种图形,将其细微部分放大后,其结构看起来仍与原先的一样。分形是一个新的数学领域,早在1998 年分形技术已经应用于片上天线与片上电容的设计。图1(b)显示了三阶Moore 形电感[2]。对于毫米波集成电路而言,所需电感感值一般不高,这样设计低阶分形电感就能满足电路设计需求,可以有效减小电感面积。目前绝大多数分形电感都是采用MEMS 及III-V 族工艺制造,制约硅基分形电感应用的主要问题是衬底损耗与金属线损耗过大,品质因数较低。3 片上分形电感电磁仿真分形电感在单位面积内能够拥有较长的金属路径,因此与绕组电感相比,电感密度较大。与螺旋电感相比,分形电感另外一个优势是只需要一层金属就能够完成整个电感的设计,不需要过孔与金属过线,这样可以使用简单的工艺来制造,节约成本。但螺旋电感金属线间有互感存在,因此螺旋电感感值较大。为了比较分形电感与传统电感的性能差异,采用华虹宏力微电子公司130nm 1P6M BiCMOS 工艺仿真了面积相同的三阶Hilbert 分形电感与方形单端电感,版图结构如图2 所示。图中金属线宽为10微米,金属间隙为2 微米,电感金属线由有顶层技术构成,单端电感金属过线由M5 构成。

图1 不同类型片上电感版图结构:(a)螺旋电感;(b)分形电感(三阶Moore 形电感);(c) 绕组电感;(d) 传输线电感片上电感一般由金属线和衬底构成,提高其性能可以从下面两个方向进行设计:第一个方向是改进元件工艺。包括采用电阻率低的金属作为元件环绕材料;采用高电阻率的衬底减小衬底寄生效应;采用厚氧化层或微机电系统工艺悬空金属过线来提高螺旋元件性能;采用硅通孔技术 [8]、纳米磁性材料、铁氧体材料和新型磁介质结构设计[9-11]使片上电感由二维到三维结构转变,增加器件磁通量。这种类型元件性能提高方法不能与传统CMOS 工艺相兼容。另一个方向是在现有CMOS 工艺基础上通过版图优化设计提升元件性能。通过多路径技术能够抑制趋肤效应与邻近效应,采用过孔把多层金属线相连能够增加金属线厚度,提高元件品质因数 [12];采用内外圈金属宽度渐变的设计方法,能够降低邻近效应与趋肤效应对电感品质因数的影响;采用屏蔽层能够减小衬底损耗等等。分形电感的设计越来越引起人们的关注,分形是这样一种图形,将其细微部分放大后,其结构看起来仍与原先的一样。分形是一个新的数学领域,早在1998 年分形技术已经应用于片上天线与片上电容的设计。图1(b)显示了三阶Moore 形电感[2]。对于毫米波集成电路而言,所需电感感值一般不高,这样设计低阶分形电感就能满足电路设计需求,可以有效减小电感面积。目前绝大多数分形电感都是采用MEMS 及III-V 族工艺制造,制约硅基分形电感应用的主要问题是衬底损耗与金属线损耗过大,品质因数较低。3 片上分形电感电磁仿真分形电感在单位面积内能够拥有较长的金属路径,因此与绕组电感相比,电感密度较大。与螺旋电感相比,分形电感另外一个优势是只需要一层金属就能够完成整个电感的设计,不需要过孔与金属过线,这样可以使用简单的工艺来制造,节约成本。但螺旋电感金属线间有互感存在,因此螺旋电感感值较大。为了比较分形电感与传统电感的性能差异,采用华虹宏力微电子公司130nm 1P6M BiCMOS 工艺仿真了面积相同的三阶Hilbert 分形电感与方形单端电感,版图结构如图2 所示。图中金属线宽为10微米,金属间隙为2 微米,电感金属线由有顶层技术构成,单端电感金属过线由M5 构成。

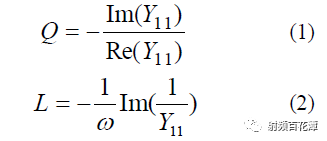

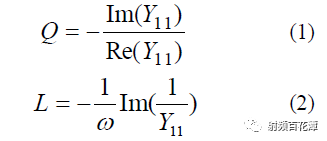

图2 分形电感与单端电感版图结构:(a)三阶Hilbert 分形电感;(b)方形单端电感使用ADS MOMENTUM 电磁仿真软件对片上分形电感与单端电感进行了仿真,仿真频率设置为0.1-80.1GHz。图3 给出了仿真的品质因数Q 与电感值L 比较图,片上电感Q 与L 计算公式分别为:

图2 分形电感与单端电感版图结构:(a)三阶Hilbert 分形电感;(b)方形单端电感使用ADS MOMENTUM 电磁仿真软件对片上分形电感与单端电感进行了仿真,仿真频率设置为0.1-80.1GHz。图3 给出了仿真的品质因数Q 与电感值L 比较图,片上电感Q 与L 计算公式分别为:

由图3 可知,螺旋电感在射频段品质因数与电感都较高,品质因数最大值为10.03,电感值约为0.8 nL,但在毫米波频段,螺旋电感已发生谐振而失去感性。相比较,分形电感在整个仿真频段内电感值与品质因数变化不大(品质因数大于5,电感值约为0.18 nL),由此可知螺旋电感适用于射频集成电路设计,而分型电感能够满足毫米波集成电路的设计需求。

由图3 可知,螺旋电感在射频段品质因数与电感都较高,品质因数最大值为10.03,电感值约为0.8 nL,但在毫米波频段,螺旋电感已发生谐振而失去感性。相比较,分形电感在整个仿真频段内电感值与品质因数变化不大(品质因数大于5,电感值约为0.18 nL),由此可知螺旋电感适用于射频集成电路设计,而分型电感能够满足毫米波集成电路的设计需求。

图3 分形电感与单端电感品质因数Q 与感值L 比较图:(a)品质因数Q;(b)感值L4 结论片上电感是集成电路设计关键无源元件之一,广泛应用于集成电路设计中。随着无线通信技术的发展,传统螺旋电感已经不能满足毫米波电路设计需求。本文主要基于ADS MOMENTUM 电磁仿真软件,对硅基片上分型电感与螺旋电感进行了设计分析。仿真结果显示,在毫米波频段,螺旋电感会发生谐振而失去感性。而分形电感在整个仿真频段内电感值与品质因数变化不大。同时分形电感版图结构简单,可以广泛应用于毫米波集成电路设计。作者:韩 波 王诗兵 史晓凤

图3 分形电感与单端电感品质因数Q 与感值L 比较图:(a)品质因数Q;(b)感值L4 结论片上电感是集成电路设计关键无源元件之一,广泛应用于集成电路设计中。随着无线通信技术的发展,传统螺旋电感已经不能满足毫米波电路设计需求。本文主要基于ADS MOMENTUM 电磁仿真软件,对硅基片上分型电感与螺旋电感进行了设计分析。仿真结果显示,在毫米波频段,螺旋电感会发生谐振而失去感性。而分形电感在整个仿真频段内电感值与品质因数变化不大。同时分形电感版图结构简单,可以广泛应用于毫米波集成电路设计。作者:韩 波 王诗兵 史晓凤

微信万人群1.仅限射频人员,不重复加群2.先加群主,验证后邀请加入3.需要注明:单位+岗位/方向

微信万人群1.仅限射频人员,不重复加群2.先加群主,验证后邀请加入3.需要注明:单位+岗位/方向

射频百花潭关注中国最大的射频公众号

射频百花潭关注中国最大的射频公众号

射频百花潭专注于射频微波/高频高速技术分享和信息传递。由资深射频专家、深圳兴森快捷射频实验室主任、《ADS2008/2011射频电路设计与仿真实例》《HFSS射频仿真设计实例大全》主编徐兴福建立,该号已经50000人关注,10000人加群,包括IEEE Fellow多名。PCB制板、射频/高速PCB设计、仿真请联系群主。

射频百花潭专注于射频微波/高频高速技术分享和信息传递。由资深射频专家、深圳兴森快捷射频实验室主任、《ADS2008/2011射频电路设计与仿真实例》《HFSS射频仿真设计实例大全》主编徐兴福建立,该号已经50000人关注,10000人加群,包括IEEE Fellow多名。PCB制板、射频/高速PCB设计、仿真请联系群主。

绝大多数毫米波集成电路都采用III-V 族等特殊材料和工艺制作,成本较高,这限制了毫米波电路的普及。硅基毫米波的研究起始于2000 年左右,随着深亚微米和纳米工艺的日趋成熟,设计实现毫米波CMOS 集成电路已经成为可能,有望大幅度降低毫米波集成电路的成本。绝大多数毫米波集成电路都采用III-V族等特殊材料和工艺制作,成本较高,这限制了毫米波电路的普及。硅基毫米波的研究起始于2000 年左右,随着深亚微米和纳米工艺的日趋成熟,设计实现毫米波CMOS 集成电路已经成为可能,有望大幅度降低毫米波集成电路的成本。2 片上电感分析片上电感广泛地应用于低噪声放大器、功率放大器、混频器、功率分配器和移相器等集成电路中。毫米波频段波长很短,电路具有极小的尺寸,电路所需电感值一般为数十皮亨,远小于射频电路所需的电感值。这样可以缓解电感面积对芯片尺寸的制约,同时为分形电感[2]、绕组电感[3-4]及传输线型电感[5]等新型片上电感设计带来机遇(如图1 感[5]等新型片上电感设计带来机遇(如图1 所示)。另一方面,片上电感在毫米波频段的结构、损耗机制和性能等方面都与低频段存在很大的差异,片上螺旋电感的趋肤效应、邻近效应、涡流效应及衬底耦合效应等各种寄生效应会变得更加严重[6],这增加了毫米波片上电感的设计。缺乏高性能片上电感成为制约集成电路发展与高性能芯片系统实现的主要瓶颈之一[7]。

绝大多数毫米波集成电路都采用III-V 族等特殊材料和工艺制作,成本较高,这限制了毫米波电路的普及。硅基毫米波的研究起始于2000 年左右,随着深亚微米和纳米工艺的日趋成熟,设计实现毫米波CMOS 集成电路已经成为可能,有望大幅度降低毫米波集成电路的成本。绝大多数毫米波集成电路都采用III-V族等特殊材料和工艺制作,成本较高,这限制了毫米波电路的普及。硅基毫米波的研究起始于2000 年左右,随着深亚微米和纳米工艺的日趋成熟,设计实现毫米波CMOS 集成电路已经成为可能,有望大幅度降低毫米波集成电路的成本。2 片上电感分析片上电感广泛地应用于低噪声放大器、功率放大器、混频器、功率分配器和移相器等集成电路中。毫米波频段波长很短,电路具有极小的尺寸,电路所需电感值一般为数十皮亨,远小于射频电路所需的电感值。这样可以缓解电感面积对芯片尺寸的制约,同时为分形电感[2]、绕组电感[3-4]及传输线型电感[5]等新型片上电感设计带来机遇(如图1 感[5]等新型片上电感设计带来机遇(如图1 所示)。另一方面,片上电感在毫米波频段的结构、损耗机制和性能等方面都与低频段存在很大的差异,片上螺旋电感的趋肤效应、邻近效应、涡流效应及衬底耦合效应等各种寄生效应会变得更加严重[6],这增加了毫米波片上电感的设计。缺乏高性能片上电感成为制约集成电路发展与高性能芯片系统实现的主要瓶颈之一[7]。 图1 不同类型片上电感版图结构:(a)螺旋电感;(b)分形电感(三阶Moore 形电感);(c) 绕组电感;(d) 传输线电感片上电感一般由金属线和衬底构成,提高其性能可以从下面两个方向进行设计:第一个方向是改进元件工艺。包括采用电阻率低的金属作为元件环绕材料;采用高电阻率的衬底减小衬底寄生效应;采用厚氧化层或微机电系统工艺悬空金属过线来提高螺旋元件性能;采用硅通孔技术 [8]、纳米磁性材料、铁氧体材料和新型磁介质结构设计[9-11]使片上电感由二维到三维结构转变,增加器件磁通量。这种类型元件性能提高方法不能与传统CMOS 工艺相兼容。另一个方向是在现有CMOS 工艺基础上通过版图优化设计提升元件性能。通过多路径技术能够抑制趋肤效应与邻近效应,采用过孔把多层金属线相连能够增加金属线厚度,提高元件品质因数 [12];采用内外圈金属宽度渐变的设计方法,能够降低邻近效应与趋肤效应对电感品质因数的影响;采用屏蔽层能够减小衬底损耗等等。分形电感的设计越来越引起人们的关注,分形是这样一种图形,将其细微部分放大后,其结构看起来仍与原先的一样。分形是一个新的数学领域,早在1998 年分形技术已经应用于片上天线与片上电容的设计。图1(b)显示了三阶Moore 形电感[2]。对于毫米波集成电路而言,所需电感感值一般不高,这样设计低阶分形电感就能满足电路设计需求,可以有效减小电感面积。目前绝大多数分形电感都是采用MEMS 及III-V 族工艺制造,制约硅基分形电感应用的主要问题是衬底损耗与金属线损耗过大,品质因数较低。3 片上分形电感电磁仿真分形电感在单位面积内能够拥有较长的金属路径,因此与绕组电感相比,电感密度较大。与螺旋电感相比,分形电感另外一个优势是只需要一层金属就能够完成整个电感的设计,不需要过孔与金属过线,这样可以使用简单的工艺来制造,节约成本。但螺旋电感金属线间有互感存在,因此螺旋电感感值较大。为了比较分形电感与传统电感的性能差异,采用华虹宏力微电子公司130nm 1P6M BiCMOS 工艺仿真了面积相同的三阶Hilbert 分形电感与方形单端电感,版图结构如图2 所示。图中金属线宽为10微米,金属间隙为2 微米,电感金属线由有顶层技术构成,单端电感金属过线由M5 构成。

图1 不同类型片上电感版图结构:(a)螺旋电感;(b)分形电感(三阶Moore 形电感);(c) 绕组电感;(d) 传输线电感片上电感一般由金属线和衬底构成,提高其性能可以从下面两个方向进行设计:第一个方向是改进元件工艺。包括采用电阻率低的金属作为元件环绕材料;采用高电阻率的衬底减小衬底寄生效应;采用厚氧化层或微机电系统工艺悬空金属过线来提高螺旋元件性能;采用硅通孔技术 [8]、纳米磁性材料、铁氧体材料和新型磁介质结构设计[9-11]使片上电感由二维到三维结构转变,增加器件磁通量。这种类型元件性能提高方法不能与传统CMOS 工艺相兼容。另一个方向是在现有CMOS 工艺基础上通过版图优化设计提升元件性能。通过多路径技术能够抑制趋肤效应与邻近效应,采用过孔把多层金属线相连能够增加金属线厚度,提高元件品质因数 [12];采用内外圈金属宽度渐变的设计方法,能够降低邻近效应与趋肤效应对电感品质因数的影响;采用屏蔽层能够减小衬底损耗等等。分形电感的设计越来越引起人们的关注,分形是这样一种图形,将其细微部分放大后,其结构看起来仍与原先的一样。分形是一个新的数学领域,早在1998 年分形技术已经应用于片上天线与片上电容的设计。图1(b)显示了三阶Moore 形电感[2]。对于毫米波集成电路而言,所需电感感值一般不高,这样设计低阶分形电感就能满足电路设计需求,可以有效减小电感面积。目前绝大多数分形电感都是采用MEMS 及III-V 族工艺制造,制约硅基分形电感应用的主要问题是衬底损耗与金属线损耗过大,品质因数较低。3 片上分形电感电磁仿真分形电感在单位面积内能够拥有较长的金属路径,因此与绕组电感相比,电感密度较大。与螺旋电感相比,分形电感另外一个优势是只需要一层金属就能够完成整个电感的设计,不需要过孔与金属过线,这样可以使用简单的工艺来制造,节约成本。但螺旋电感金属线间有互感存在,因此螺旋电感感值较大。为了比较分形电感与传统电感的性能差异,采用华虹宏力微电子公司130nm 1P6M BiCMOS 工艺仿真了面积相同的三阶Hilbert 分形电感与方形单端电感,版图结构如图2 所示。图中金属线宽为10微米,金属间隙为2 微米,电感金属线由有顶层技术构成,单端电感金属过线由M5 构成。 图2 分形电感与单端电感版图结构:(a)三阶Hilbert 分形电感;(b)方形单端电感使用ADS MOMENTUM 电磁仿真软件对片上分形电感与单端电感进行了仿真,仿真频率设置为0.1-80.1GHz。图3 给出了仿真的品质因数Q 与电感值L 比较图,片上电感Q 与L 计算公式分别为:

图2 分形电感与单端电感版图结构:(a)三阶Hilbert 分形电感;(b)方形单端电感使用ADS MOMENTUM 电磁仿真软件对片上分形电感与单端电感进行了仿真,仿真频率设置为0.1-80.1GHz。图3 给出了仿真的品质因数Q 与电感值L 比较图,片上电感Q 与L 计算公式分别为: 由图3 可知,螺旋电感在射频段品质因数与电感都较高,品质因数最大值为10.03,电感值约为0.8 nL,但在毫米波频段,螺旋电感已发生谐振而失去感性。相比较,分形电感在整个仿真频段内电感值与品质因数变化不大(品质因数大于5,电感值约为0.18 nL),由此可知螺旋电感适用于射频集成电路设计,而分型电感能够满足毫米波集成电路的设计需求。

由图3 可知,螺旋电感在射频段品质因数与电感都较高,品质因数最大值为10.03,电感值约为0.8 nL,但在毫米波频段,螺旋电感已发生谐振而失去感性。相比较,分形电感在整个仿真频段内电感值与品质因数变化不大(品质因数大于5,电感值约为0.18 nL),由此可知螺旋电感适用于射频集成电路设计,而分型电感能够满足毫米波集成电路的设计需求。 图3 分形电感与单端电感品质因数Q 与感值L 比较图:(a)品质因数Q;(b)感值L4 结论片上电感是集成电路设计关键无源元件之一,广泛应用于集成电路设计中。随着无线通信技术的发展,传统螺旋电感已经不能满足毫米波电路设计需求。本文主要基于ADS MOMENTUM 电磁仿真软件,对硅基片上分型电感与螺旋电感进行了设计分析。仿真结果显示,在毫米波频段,螺旋电感会发生谐振而失去感性。而分形电感在整个仿真频段内电感值与品质因数变化不大。同时分形电感版图结构简单,可以广泛应用于毫米波集成电路设计。作者:韩 波 王诗兵 史晓凤

图3 分形电感与单端电感品质因数Q 与感值L 比较图:(a)品质因数Q;(b)感值L4 结论片上电感是集成电路设计关键无源元件之一,广泛应用于集成电路设计中。随着无线通信技术的发展,传统螺旋电感已经不能满足毫米波电路设计需求。本文主要基于ADS MOMENTUM 电磁仿真软件,对硅基片上分型电感与螺旋电感进行了设计分析。仿真结果显示,在毫米波频段,螺旋电感会发生谐振而失去感性。而分形电感在整个仿真频段内电感值与品质因数变化不大。同时分形电感版图结构简单,可以广泛应用于毫米波集成电路设计。作者:韩 波 王诗兵 史晓凤 微信万人群1.仅限射频人员,不重复加群2.先加群主,验证后邀请加入3.需要注明:单位+岗位/方向

微信万人群1.仅限射频人员,不重复加群2.先加群主,验证后邀请加入3.需要注明:单位+岗位/方向 射频百花潭关注中国最大的射频公众号

射频百花潭关注中国最大的射频公众号 射频百花潭专注于射频微波/高频高速技术分享和信息传递。由资深射频专家、深圳兴森快捷射频实验室主任、《ADS2008/2011射频电路设计与仿真实例》《HFSS射频仿真设计实例大全》主编徐兴福建立,该号已经50000人关注,10000人加群,包括IEEE Fellow多名。PCB制板、射频/高速PCB设计、仿真请联系群主。

射频百花潭专注于射频微波/高频高速技术分享和信息传递。由资深射频专家、深圳兴森快捷射频实验室主任、《ADS2008/2011射频电路设计与仿真实例》《HFSS射频仿真设计实例大全》主编徐兴福建立,该号已经50000人关注,10000人加群,包括IEEE Fellow多名。PCB制板、射频/高速PCB设计、仿真请联系群主。 相关文章:

- 怎样用CST仿出电感模型的电感值随频率变化的图形(05-08)

- 如何在HFSS中仿真多层电容和电感,谢谢(05-08)

- HFSS中如何建电感模型啊?(05-08)

- 求教高手如何通过仿真得到电感的数值 公式是什么?(05-08)

- ADS 中集成电感电容的值怎么设置那(05-08)

- ADS库中 怎么没看见 0603封装的电阻电容电感啊。(05-08)

射频专业培训教程推荐