戴维南端接匹配简易阻抗匹配方法

05-08

在高速的设计中,阻抗的匹配与否关系到信号的质量优劣。阻抗匹配的技术可以说是丰富多样,在此只对几种简单常用的端接方法进行介绍。为什么要进行阻抗匹配呢?无外乎几种原因,如减少反射、控制信号边沿速率、减少信号波动、一些电平信号本身需要等等。端接阻抗匹配一般有5种方法:1.源端串联匹配,2.终端并联匹配,3.戴维南匹配,4.RC网络匹配,5.二极管匹配。1、串联端接匹配:

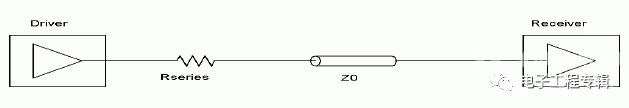

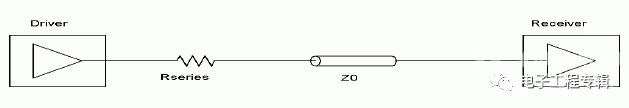

一般多在源端使用,Rs(串联电阻)=Z0(传输线的特性阻抗)-R0(源阻抗)。例如:若R0为22,Z0为55Ω,则Rs应为33Ω。优点:①器件单一;②抑制振铃,减少过冲;③适用于集总线型负载和单一负载;④增强信号完整性,产生更小EMI。缺点:①当TTL,CMOS器件出现在相同网络时,串联匹配不是最佳选择;②分布式负载不是适用,因为在走线路径的中间,电压仅是源电压的一般;③接收端的反相反射仍然存在;④影响信号上升时间并增加信号延时。2、并联端接匹配:

一般多在源端使用,Rs(串联电阻)=Z0(传输线的特性阻抗)-R0(源阻抗)。例如:若R0为22,Z0为55Ω,则Rs应为33Ω。优点:①器件单一;②抑制振铃,减少过冲;③适用于集总线型负载和单一负载;④增强信号完整性,产生更小EMI。缺点:①当TTL,CMOS器件出现在相同网络时,串联匹配不是最佳选择;②分布式负载不是适用,因为在走线路径的中间,电压仅是源电压的一般;③接收端的反相反射仍然存在;④影响信号上升时间并增加信号延时。2、并联端接匹配:

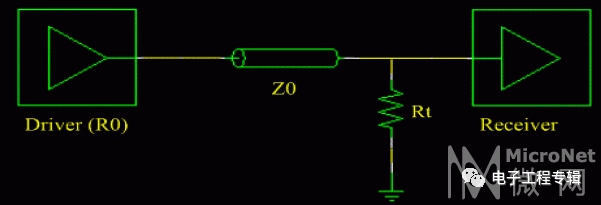

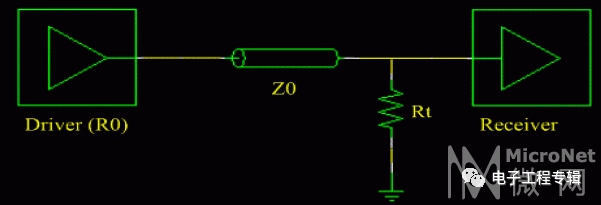

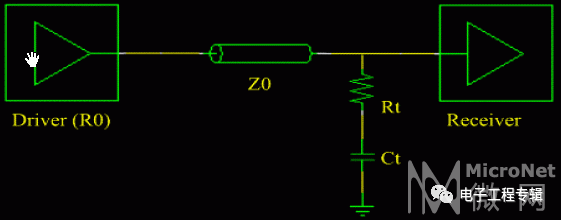

此Rt电阻值必须等于传输线所要求的电阻值,电阻的一端接信号,一端接地或电源。简单的终端并联匹配一般不用于TTL,COMS电路,因为在高逻辑状态时,此方法需要较大的驱动电流。优点:①器件单一;②适用于分布式负载;③反射几乎可以完全消除;④电阻阻值易于选择。缺点:①此电阻需要驱动源端的电流驱动,增加系统电路的功耗;②降低噪声容限。此电阻值必须等于传输线所要求的电阻值。电阻的一端接信号,一端接地。简单的终端并联匹配一般不用于TTL,COMS电路,因为他们无法提供强大的输出电流。3、戴维南端接匹配:

此Rt电阻值必须等于传输线所要求的电阻值,电阻的一端接信号,一端接地或电源。简单的终端并联匹配一般不用于TTL,COMS电路,因为在高逻辑状态时,此方法需要较大的驱动电流。优点:①器件单一;②适用于分布式负载;③反射几乎可以完全消除;④电阻阻值易于选择。缺点:①此电阻需要驱动源端的电流驱动,增加系统电路的功耗;②降低噪声容限。此电阻值必须等于传输线所要求的电阻值。电阻的一端接信号,一端接地。简单的终端并联匹配一般不用于TTL,COMS电路,因为他们无法提供强大的输出电流。3、戴维南端接匹配:

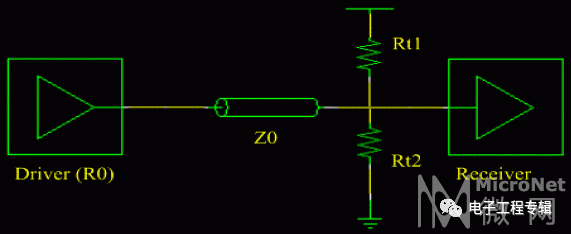

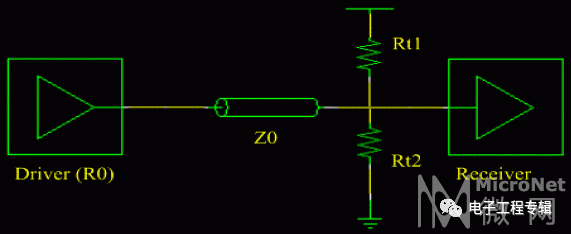

一个电阻上拉,一个电阻下拉,通常采用R1/R2=220/330的比值。戴维南等效阻抗必须等于走线的特性阻抗。对于大多数设计R1>R2,否则TTL/COMS电路将无法工作。优点:①适用于分布式负载;②完全吸收发送波,消除反射。;缺点:①增加系统电路的功耗;②降低噪声容限;③使用两个电阻,增加布局、布线难度;④电阻值不易于选择。4、RC网络匹配:

一个电阻上拉,一个电阻下拉,通常采用R1/R2=220/330的比值。戴维南等效阻抗必须等于走线的特性阻抗。对于大多数设计R1>R2,否则TTL/COMS电路将无法工作。优点:①适用于分布式负载;②完全吸收发送波,消除反射。;缺点:①增加系统电路的功耗;②降低噪声容限;③使用两个电阻,增加布局、布线难度;④电阻值不易于选择。4、RC网络匹配:

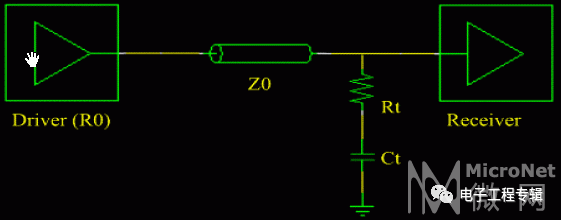

电阻与电容相连,电阻另一端接信号,电容另一端接地。电阻应等于走线特性阻抗,容值通常较小(20pF-600pF)。对差分信号只需三个原件,两个电阻加一个电容。优点:①适用于分布式及总线型负载;②完全吸收发送波,消除反射;③具有很低的直流功率损耗。缺点:①会降低高速信号的速率,增加信号延时;②RC电路的时间常数会导致电路中存在反射;③对于高频、高速短路要慎用;④使用两个器件,增加布局、布线难度。5、二极管端接匹配:

电阻与电容相连,电阻另一端接信号,电容另一端接地。电阻应等于走线特性阻抗,容值通常较小(20pF-600pF)。对差分信号只需三个原件,两个电阻加一个电容。优点:①适用于分布式及总线型负载;②完全吸收发送波,消除反射;③具有很低的直流功率损耗。缺点:①会降低高速信号的速率,增加信号延时;②RC电路的时间常数会导致电路中存在反射;③对于高频、高速短路要慎用;④使用两个器件,增加布局、布线难度。5、二极管端接匹配:

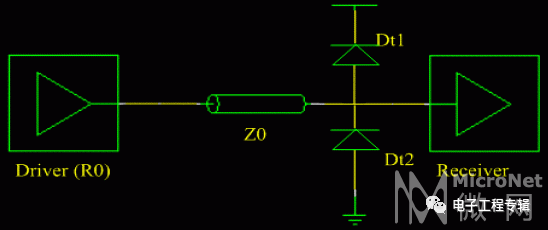

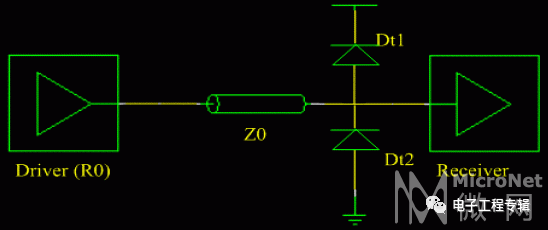

此端接常用于差分或成对网络,二极管常用于限制走线过程的过冲。优点:①预防输入端的过冲。缺点:①不能减少反射。长按二维码识别关注

此端接常用于差分或成对网络,二极管常用于限制走线过程的过冲。优点:①预防输入端的过冲。缺点:①不能减少反射。长按二维码识别关注

电子路上与你同行!

电子路上与你同行!

一般多在源端使用,Rs(串联电阻)=Z0(传输线的特性阻抗)-R0(源阻抗)。例如:若R0为22,Z0为55Ω,则Rs应为33Ω。优点:①器件单一;②抑制振铃,减少过冲;③适用于集总线型负载和单一负载;④增强信号完整性,产生更小EMI。缺点:①当TTL,CMOS器件出现在相同网络时,串联匹配不是最佳选择;②分布式负载不是适用,因为在走线路径的中间,电压仅是源电压的一般;③接收端的反相反射仍然存在;④影响信号上升时间并增加信号延时。2、并联端接匹配:

一般多在源端使用,Rs(串联电阻)=Z0(传输线的特性阻抗)-R0(源阻抗)。例如:若R0为22,Z0为55Ω,则Rs应为33Ω。优点:①器件单一;②抑制振铃,减少过冲;③适用于集总线型负载和单一负载;④增强信号完整性,产生更小EMI。缺点:①当TTL,CMOS器件出现在相同网络时,串联匹配不是最佳选择;②分布式负载不是适用,因为在走线路径的中间,电压仅是源电压的一般;③接收端的反相反射仍然存在;④影响信号上升时间并增加信号延时。2、并联端接匹配: 此Rt电阻值必须等于传输线所要求的电阻值,电阻的一端接信号,一端接地或电源。简单的终端并联匹配一般不用于TTL,COMS电路,因为在高逻辑状态时,此方法需要较大的驱动电流。优点:①器件单一;②适用于分布式负载;③反射几乎可以完全消除;④电阻阻值易于选择。缺点:①此电阻需要驱动源端的电流驱动,增加系统电路的功耗;②降低噪声容限。此电阻值必须等于传输线所要求的电阻值。电阻的一端接信号,一端接地。简单的终端并联匹配一般不用于TTL,COMS电路,因为他们无法提供强大的输出电流。3、戴维南端接匹配:

此Rt电阻值必须等于传输线所要求的电阻值,电阻的一端接信号,一端接地或电源。简单的终端并联匹配一般不用于TTL,COMS电路,因为在高逻辑状态时,此方法需要较大的驱动电流。优点:①器件单一;②适用于分布式负载;③反射几乎可以完全消除;④电阻阻值易于选择。缺点:①此电阻需要驱动源端的电流驱动,增加系统电路的功耗;②降低噪声容限。此电阻值必须等于传输线所要求的电阻值。电阻的一端接信号,一端接地。简单的终端并联匹配一般不用于TTL,COMS电路,因为他们无法提供强大的输出电流。3、戴维南端接匹配: 一个电阻上拉,一个电阻下拉,通常采用R1/R2=220/330的比值。戴维南等效阻抗必须等于走线的特性阻抗。对于大多数设计R1>R2,否则TTL/COMS电路将无法工作。优点:①适用于分布式负载;②完全吸收发送波,消除反射。;缺点:①增加系统电路的功耗;②降低噪声容限;③使用两个电阻,增加布局、布线难度;④电阻值不易于选择。4、RC网络匹配:

一个电阻上拉,一个电阻下拉,通常采用R1/R2=220/330的比值。戴维南等效阻抗必须等于走线的特性阻抗。对于大多数设计R1>R2,否则TTL/COMS电路将无法工作。优点:①适用于分布式负载;②完全吸收发送波,消除反射。;缺点:①增加系统电路的功耗;②降低噪声容限;③使用两个电阻,增加布局、布线难度;④电阻值不易于选择。4、RC网络匹配: 电阻与电容相连,电阻另一端接信号,电容另一端接地。电阻应等于走线特性阻抗,容值通常较小(20pF-600pF)。对差分信号只需三个原件,两个电阻加一个电容。优点:①适用于分布式及总线型负载;②完全吸收发送波,消除反射;③具有很低的直流功率损耗。缺点:①会降低高速信号的速率,增加信号延时;②RC电路的时间常数会导致电路中存在反射;③对于高频、高速短路要慎用;④使用两个器件,增加布局、布线难度。5、二极管端接匹配:

电阻与电容相连,电阻另一端接信号,电容另一端接地。电阻应等于走线特性阻抗,容值通常较小(20pF-600pF)。对差分信号只需三个原件,两个电阻加一个电容。优点:①适用于分布式及总线型负载;②完全吸收发送波,消除反射;③具有很低的直流功率损耗。缺点:①会降低高速信号的速率,增加信号延时;②RC电路的时间常数会导致电路中存在反射;③对于高频、高速短路要慎用;④使用两个器件,增加布局、布线难度。5、二极管端接匹配: 此端接常用于差分或成对网络,二极管常用于限制走线过程的过冲。优点:①预防输入端的过冲。缺点:①不能减少反射。长按二维码识别关注

此端接常用于差分或成对网络,二极管常用于限制走线过程的过冲。优点:①预防输入端的过冲。缺点:①不能减少反射。长按二维码识别关注 电子路上与你同行!

电子路上与你同行! 相关文章:

- 共烧材料匹配:LTCC研发关注点(05-08)

- 关于匹配网络(05-08)

- 关于贴片的匹配电路的疑惑!知道的前辈们指点一下。(05-08)

- 有磁阻抗匹配的问题(05-08)

- 耦合波导的匹配(05-08)

- ADS 阻抗匹配(05-08)

射频专业培训教程推荐