航天科工二院25所自主研制宽带PLL频率综合器芯片

05-08

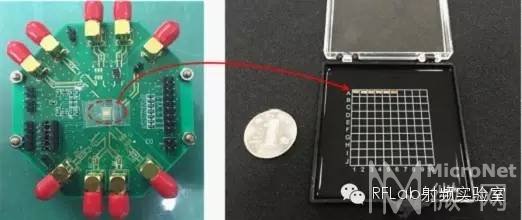

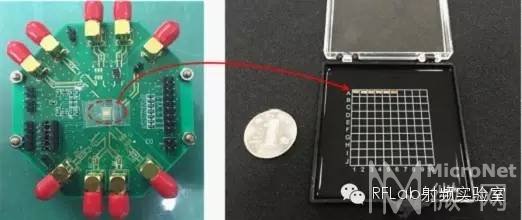

近日,中国航天科工二院25所微系统研发中心传来捷报,由该所独立开展的宽带PLL(Phase-Locked Loop,锁相环)频率综合器芯片研制获得成功。该芯片是25所首款具备数字、模拟以及射频混合特征的芯片,也是集团公司首颗拥有自主知识产权的宽带PLL频率综合器芯片。频率源是无线通信系统的重要硬件组成部分,它为射频收发系统提供本地振荡信号来完成上下变频功能,是各类型号产品中不可缺少的重要部件,而频率综合器则是实现可编程频率源的核心器件。面对弹载设备升级换代、提升竞争力的迫切需求,传统的频率源设计方式面临减体积、降成本的巨大压力。因此,研发拥有自主知识产权的宽带PLL频率综合器芯片,不仅能够有效促进系统体积减小、成本降低,也能够为系统的硬件可重构提供器件基础,更有助于实现核心技术的自主可控,对于武器系统中射频收发的微小型化设计乃至整机SoC设计的作用和意义都非常大。

由25所研发的该款芯片以通用、宽带、高性能频率源应用为设计目标,可以满足多个型号对频率源的需求。未来在实现定型和量产后,体积、重量及成本将比现有系统中相应模块分别降低60%以上。由于其具备了很强的通用性,该芯片还可以应用在多种武器装备的无线通信系统中,市场前景广阔。该芯片的研制成功,是25所继数字SoC“精导芯Ⅰ号”成功发布和应答机平台射频收发SoC完成首次流片后,在射频及数模混合SoC领域的又一次关键技术突破,标志着25所已完全具备了数模混合SoC的自主研发能力。本文来源:中国航天科工二院

由25所研发的该款芯片以通用、宽带、高性能频率源应用为设计目标,可以满足多个型号对频率源的需求。未来在实现定型和量产后,体积、重量及成本将比现有系统中相应模块分别降低60%以上。由于其具备了很强的通用性,该芯片还可以应用在多种武器装备的无线通信系统中,市场前景广阔。该芯片的研制成功,是25所继数字SoC“精导芯Ⅰ号”成功发布和应答机平台射频收发SoC完成首次流片后,在射频及数模混合SoC领域的又一次关键技术突破,标志着25所已完全具备了数模混合SoC的自主研发能力。本文来源:中国航天科工二院

由25所研发的该款芯片以通用、宽带、高性能频率源应用为设计目标,可以满足多个型号对频率源的需求。未来在实现定型和量产后,体积、重量及成本将比现有系统中相应模块分别降低60%以上。由于其具备了很强的通用性,该芯片还可以应用在多种武器装备的无线通信系统中,市场前景广阔。该芯片的研制成功,是25所继数字SoC“精导芯Ⅰ号”成功发布和应答机平台射频收发SoC完成首次流片后,在射频及数模混合SoC领域的又一次关键技术突破,标志着25所已完全具备了数模混合SoC的自主研发能力。本文来源:中国航天科工二院

由25所研发的该款芯片以通用、宽带、高性能频率源应用为设计目标,可以满足多个型号对频率源的需求。未来在实现定型和量产后,体积、重量及成本将比现有系统中相应模块分别降低60%以上。由于其具备了很强的通用性,该芯片还可以应用在多种武器装备的无线通信系统中,市场前景广阔。该芯片的研制成功,是25所继数字SoC“精导芯Ⅰ号”成功发布和应答机平台射频收发SoC完成首次流片后,在射频及数模混合SoC领域的又一次关键技术突破,标志着25所已完全具备了数模混合SoC的自主研发能力。本文来源:中国航天科工二院 相关文章:

- 宇宙窗口的频率是多少(05-08)

- 请问:如何在同一张图里看不同模型在同一频率的方向图(05-08)

- 问个关于CST中仿真频率设置的问题(05-08)

- 在30G以上的频率中CST如何馈电(05-08)

- HFSS中如何得到天线最大增益频率曲线(05-08)

- 求助一个频率搬移的问题(05-08)

射频专业培训教程推荐