差分滤波器布线需要注意这八点

05-08

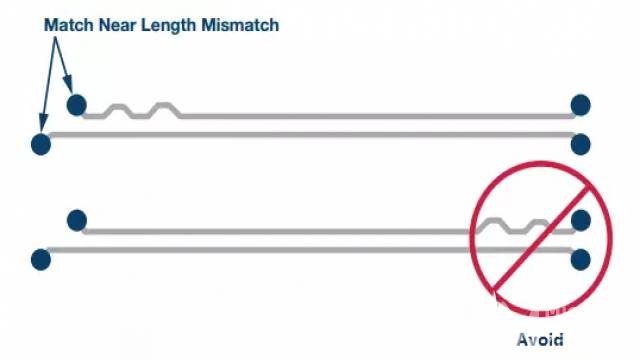

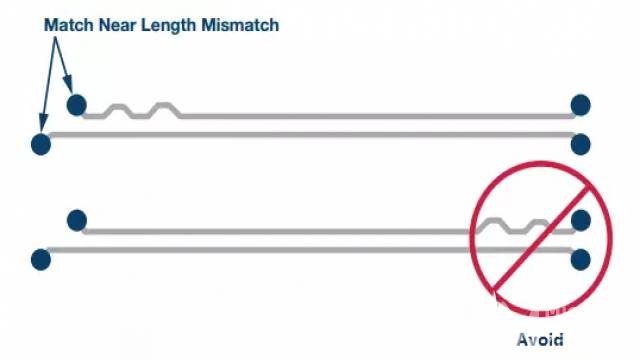

不关注我你都不知道自己错过了什么!当提到通信系统时,比起单端电路,差分电路总是能提供更加优良的性能——它们具有更高的线性度、抗共模干扰信号性能等。使用差分电路最大的挑战就是抛开它们难于设计、测试和校正的想法,需要仔细观察如何使用差分滤波器。如何使用差分滤波器?你知道吗?不晓得,就继续往下看,本文简单明了的说说8个需要注意的点儿~1、 成对差分走线的长度须相同此规则源自这一事实:差分接收器检测正负信号跨过彼此的点,即交越点。因此,信号须同时到达接收器才能正常工作。2、差分对内的走线布线须彼此靠近如果一对中的相邻线路之间的距离大于电介质厚度的2倍,则其间的耦合会很小。此规则也是基于差分信号相等但相反这一事实,如果外部噪声同等地干扰两个信号,则其影响会互相抵消。同样,如果走线并排布线,则差分信号在相邻导线中引起的任何干扰噪声都会被抵消。3、同一差分对内的走线间距在全长范围内须保持不变如果差分走线彼此靠近布线,它们将影响总阻抗。如果此间距在驱动器与接收器之间变化不定,则一路上会存在阻抗不匹配,导致反射。4、差分对之间的间距应较宽以使其间的串扰最小。5、如果在同一层上使用铜皮铺地,应加大从差分走线到铜皮铺地之间的间隙推荐最小间隙为走线宽度的3倍。6、在靠近差分对内偏斜源处引入少量弯弯曲曲的校正

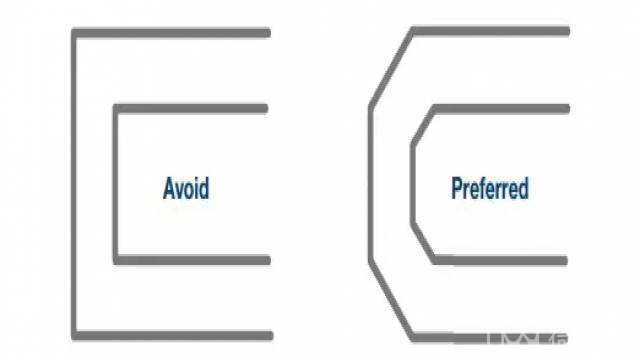

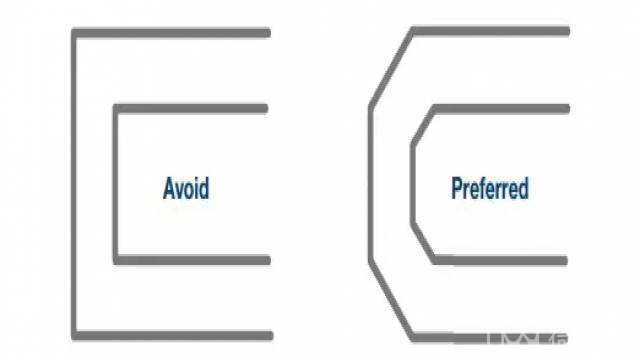

从而降低这种偏斜。在靠近差分对内偏斜源处引入少量弯弯曲曲的校正7、差分对布线时应避免急转弯(90°)。

从而降低这种偏斜。在靠近差分对内偏斜源处引入少量弯弯曲曲的校正7、差分对布线时应避免急转弯(90°)。

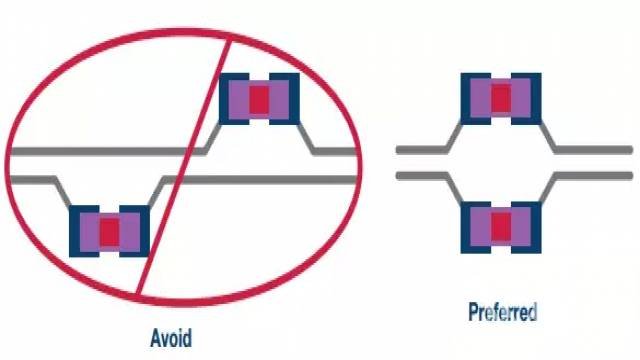

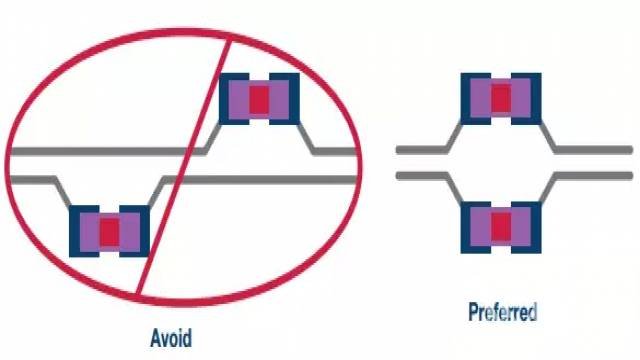

应使用对称布线。

应使用对称布线。

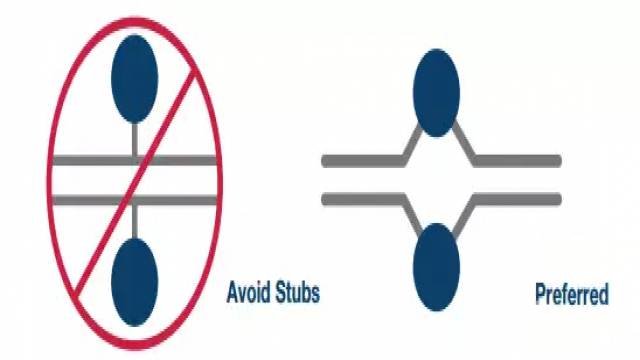

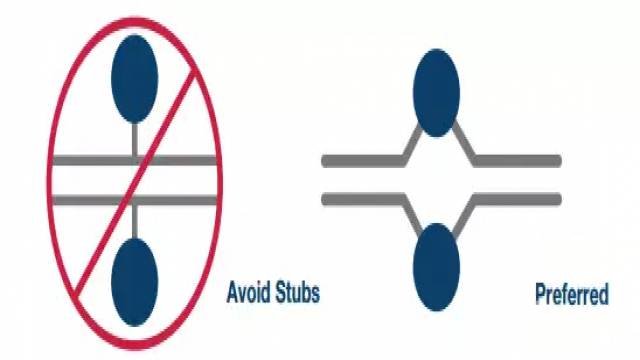

若需要测试点,应避免引入走线分支,而且测试点应对称放置)。

若需要测试点,应避免引入走线分支,而且测试点应对称放置)。

8、就降低对滤波器元件值的要求,减少印刷电路板(PCB)上的调谐工作量而言,寄生电容和电感应尽可能小。与滤波器设计中的电感设计值相比,寄生电感可能微不足道。寄生电容对差分IF滤波器更为重要。IF滤波器设计中的电容只有几pF。如果寄生电容达到数十分之一pF,滤波器响应就会受到相当大的影响。为了防止寄生电容影响,一个良好的做法是避免差分布线区域和电源扼流圈下有任何接地或电源层。来源:互联网 ,EMC家园编辑推荐阅读1.小结EMC整改常用方法;2.常见RFID标签类型及其应用场景;3.无线充电迈向中功率 线圈磁材选用定成败;4.IPhone与磁性材料形影不离;5.电磁兼容术语中英文对照;6.分享几个提高电磁兼容性的策略!;7.NFC移动支付 PK 微信支付及支付宝!;8.隔磁片在无线充电器中有什么作用?;9.LED驱动电源如何进行EMC整改?;10.中兴新能源汽车副总:无线充电十年内将颠覆用户习惯;11.RFID行业:这是最好的时代,也是最坏的时代;12.产品EMC辐射发射超标原因有哪些?。13.电子产品20多种认证,不信你都知道!请收下我的膝盖.直接在公众号(需先关注)对话框回复序列号即可查看,例如“1”。喜欢就关注我们吧!欢迎并感谢您分享转发朋友圈!我们的宗旨做最认真的公众号欢迎关注长按下方二维码识别即可免费关注

8、就降低对滤波器元件值的要求,减少印刷电路板(PCB)上的调谐工作量而言,寄生电容和电感应尽可能小。与滤波器设计中的电感设计值相比,寄生电感可能微不足道。寄生电容对差分IF滤波器更为重要。IF滤波器设计中的电容只有几pF。如果寄生电容达到数十分之一pF,滤波器响应就会受到相当大的影响。为了防止寄生电容影响,一个良好的做法是避免差分布线区域和电源扼流圈下有任何接地或电源层。来源:互联网 ,EMC家园编辑推荐阅读1.小结EMC整改常用方法;2.常见RFID标签类型及其应用场景;3.无线充电迈向中功率 线圈磁材选用定成败;4.IPhone与磁性材料形影不离;5.电磁兼容术语中英文对照;6.分享几个提高电磁兼容性的策略!;7.NFC移动支付 PK 微信支付及支付宝!;8.隔磁片在无线充电器中有什么作用?;9.LED驱动电源如何进行EMC整改?;10.中兴新能源汽车副总:无线充电十年内将颠覆用户习惯;11.RFID行业:这是最好的时代,也是最坏的时代;12.产品EMC辐射发射超标原因有哪些?。13.电子产品20多种认证,不信你都知道!请收下我的膝盖.直接在公众号(需先关注)对话框回复序列号即可查看,例如“1”。喜欢就关注我们吧!欢迎并感谢您分享转发朋友圈!我们的宗旨做最认真的公众号欢迎关注长按下方二维码识别即可免费关注

免责声明:部分资料来源于网络,转载的目的在于传递更多信息及分享,并不意味着赞同其观点或证实其真实性,也不构成其他建议,仅提供交流平台,不为其版权负责。如涉及侵权,请联系我们及时修改或删除。邮箱:yyj@szph.com.cn

免责声明:部分资料来源于网络,转载的目的在于传递更多信息及分享,并不意味着赞同其观点或证实其真实性,也不构成其他建议,仅提供交流平台,不为其版权负责。如涉及侵权,请联系我们及时修改或删除。邮箱:yyj@szph.com.cn

从而降低这种偏斜。在靠近差分对内偏斜源处引入少量弯弯曲曲的校正7、差分对布线时应避免急转弯(90°)。

从而降低这种偏斜。在靠近差分对内偏斜源处引入少量弯弯曲曲的校正7、差分对布线时应避免急转弯(90°)。 应使用对称布线。

应使用对称布线。 若需要测试点,应避免引入走线分支,而且测试点应对称放置)。

若需要测试点,应避免引入走线分支,而且测试点应对称放置)。 8、就降低对滤波器元件值的要求,减少印刷电路板(PCB)上的调谐工作量而言,寄生电容和电感应尽可能小。与滤波器设计中的电感设计值相比,寄生电感可能微不足道。寄生电容对差分IF滤波器更为重要。IF滤波器设计中的电容只有几pF。如果寄生电容达到数十分之一pF,滤波器响应就会受到相当大的影响。为了防止寄生电容影响,一个良好的做法是避免差分布线区域和电源扼流圈下有任何接地或电源层。来源:互联网 ,EMC家园编辑推荐阅读1.小结EMC整改常用方法;2.常见RFID标签类型及其应用场景;3.无线充电迈向中功率 线圈磁材选用定成败;4.IPhone与磁性材料形影不离;5.电磁兼容术语中英文对照;6.分享几个提高电磁兼容性的策略!;7.NFC移动支付 PK 微信支付及支付宝!;8.隔磁片在无线充电器中有什么作用?;9.LED驱动电源如何进行EMC整改?;10.中兴新能源汽车副总:无线充电十年内将颠覆用户习惯;11.RFID行业:这是最好的时代,也是最坏的时代;12.产品EMC辐射发射超标原因有哪些?。13.电子产品20多种认证,不信你都知道!请收下我的膝盖.直接在公众号(需先关注)对话框回复序列号即可查看,例如“1”。喜欢就关注我们吧!欢迎并感谢您分享转发朋友圈!我们的宗旨做最认真的公众号欢迎关注长按下方二维码识别即可免费关注

8、就降低对滤波器元件值的要求,减少印刷电路板(PCB)上的调谐工作量而言,寄生电容和电感应尽可能小。与滤波器设计中的电感设计值相比,寄生电感可能微不足道。寄生电容对差分IF滤波器更为重要。IF滤波器设计中的电容只有几pF。如果寄生电容达到数十分之一pF,滤波器响应就会受到相当大的影响。为了防止寄生电容影响,一个良好的做法是避免差分布线区域和电源扼流圈下有任何接地或电源层。来源:互联网 ,EMC家园编辑推荐阅读1.小结EMC整改常用方法;2.常见RFID标签类型及其应用场景;3.无线充电迈向中功率 线圈磁材选用定成败;4.IPhone与磁性材料形影不离;5.电磁兼容术语中英文对照;6.分享几个提高电磁兼容性的策略!;7.NFC移动支付 PK 微信支付及支付宝!;8.隔磁片在无线充电器中有什么作用?;9.LED驱动电源如何进行EMC整改?;10.中兴新能源汽车副总:无线充电十年内将颠覆用户习惯;11.RFID行业:这是最好的时代,也是最坏的时代;12.产品EMC辐射发射超标原因有哪些?。13.电子产品20多种认证,不信你都知道!请收下我的膝盖.直接在公众号(需先关注)对话框回复序列号即可查看,例如“1”。喜欢就关注我们吧!欢迎并感谢您分享转发朋友圈!我们的宗旨做最认真的公众号欢迎关注长按下方二维码识别即可免费关注 免责声明:部分资料来源于网络,转载的目的在于传递更多信息及分享,并不意味着赞同其观点或证实其真实性,也不构成其他建议,仅提供交流平台,不为其版权负责。如涉及侵权,请联系我们及时修改或删除。邮箱:yyj@szph.com.cn

免责声明:部分资料来源于网络,转载的目的在于传递更多信息及分享,并不意味着赞同其观点或证实其真实性,也不构成其他建议,仅提供交流平台,不为其版权负责。如涉及侵权,请联系我们及时修改或删除。邮箱:yyj@szph.com.cn 相关文章:

- Protel软件在高频电路布线中的技巧(05-08)

- 利用飞线手工布局和布线(05-08)

- 高速板4层以上布线总结(05-08)

- HFSS:仿真两微带线串扰,为何不能满足布线之3W原则?(05-08)

- 印刷布线图的基本设计方法和原则要求(05-08)

- 关于功放中的微带布线的问题?请解答疑惑(05-08)

射频专业培训教程推荐