漫谈示波器的DDC(数字下变频)技术

05-08

01引言如今随着电子产品设计的日趋复杂,测试内容也越来越复杂,人们可能不仅需要知道信号的时域特性,也想了解信号的频域特性,或者多域的联合特性也需要进行测量。结果是,很可能在工作测试台上摆满了各种仪器:示波器、频谱仪……等等,工作空间受到挤占,并且更重要的是测试工作变得复杂,各种仪器的复杂连接,仪器间的同步问题需要解决……。因此,对于一般的调试测量,人们希望能有一台多功能的仪器,既能满足时域测试的需求,又能进行频域的分析,甚至时频域信号一起进行相参的联合调试,再甚至对于一些矢量信号也能进行分析。示波器作为最基本的测试测量仪器被广泛的使用,如果能融入这些分析功能,将给工程师们带来极大的便利。目前,各示波器厂家也推出了一些多合一的示波器,技术也各不相同,不是分离的时域和频域通道测量,就是采用软件计算的方式进行分析,因此也面临一些问题。例如在频谱分析时,我们知道RBW(分辨率带宽)与信号的捕获时间成反比关系,如果需要小的RBW(通俗说就是频谱看的更精细),那就需要更长捕获时间,采样率必然会降低,那么对于高频的信号将无法进行分析。相反,如果要对高频信号进行分析,那么RBW将会较大,频率分辨率将会变弱。另外,在矢量信号分析中,同样会受到示波器存储空间和采样率的限制,导致不能对更长时间的信号进行分析。那么对于这些测量当中的问题,如何通过示波器设计来解决呢?本文介绍了R&S公司示波器采用的DDC(数字下变频)技术,很好的解决了以上问题,将多域联合测试发挥的淋漓尽致。02DDC介绍DDC(Digital Down Converter)即数字下变频,是通过NCO(数控振荡器)产生与射频或中频信号载波相同频率的正弦或余弦信号,与射频或中频信号相乘,最后通过滤波、重采样得到基带信号的过程。由于数字信号处理的巨大优势,使其得到了广泛的应用。在无线通信系统中,也越来越希望能将A/D(模数)、D/A(数模)转换靠近射频前端,从而能通过数字信号处理来实现通信中的各种功能。然而目前受ADC(模数转换器)和DSP(数字信号处理器)发展水平的限制,直接在很高频的射频端进行AD变换再进行数字信号处理非常困难——数字示波器也一样,如受处理能力限制,如果在射频端对高频信号进行AD采样,需要很高的采样率,捕获时间一旦加长,样本点数就会非常巨大,此时就会发现示波器处理时间变长,反应很缓慢。为了解决ADC与DSP的这个矛盾,采用DDC将信号变频到基带,再使用更低的速率进行重采样,就能减小数据量,提高DSP的效率。

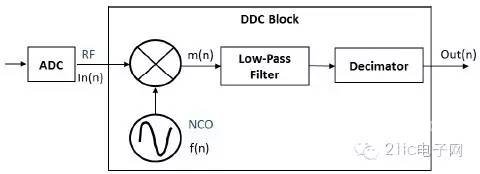

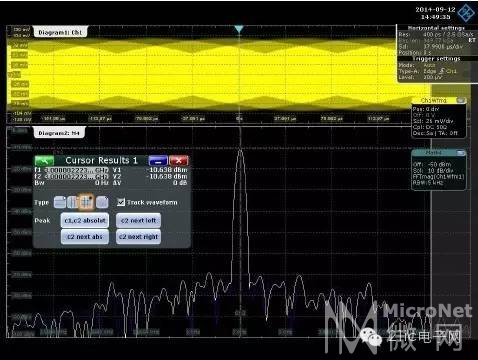

图1 DDC原理框图图1为DDC原理框图,主要由NCO、混频器、低通滤波器和重采样几个模块组成。射频信号通过高速ADC后变为数字信号In(n):In(n) = s(n)×cos(wn) (1)其中,s(n)为信号,cos(wn)为载波,w为载波频率。NCO产生与射频信号频率相同的本振信号f(n):f(n) = cos(wn) (2)本振信号与射频信号混频相乘后得到信号m(n):m(n) = In(n)×f(n) = s(n)×cos(wn)×cos(wn) = 1/2s(n)[cos(2wn)+1] (3)将信号m(n)进行低通滤波和重采样后便可得到输出信号Out(n):Out(n) = 1/2s(n) (4)由此可见,通过DDC,即保留了真实的有用信号s(n),又通过重采样使得数据量大大减少,提高了后续信号处理的效率。同样,如果在数字示波器中使用了DDC技术,不但能保留射频信号中的有用信号,同时能大大减少数据量,提高示波器的处理速度。下面我们就来讨论R&S示波器中的DDC应用。03R&S示波器硬件实现的DDC在讨论R&S示波器中的DDC应用之前,我们先来比较一下R&S数字示波器与传统数字示波器结构上的不同。

图1 DDC原理框图图1为DDC原理框图,主要由NCO、混频器、低通滤波器和重采样几个模块组成。射频信号通过高速ADC后变为数字信号In(n):In(n) = s(n)×cos(wn) (1)其中,s(n)为信号,cos(wn)为载波,w为载波频率。NCO产生与射频信号频率相同的本振信号f(n):f(n) = cos(wn) (2)本振信号与射频信号混频相乘后得到信号m(n):m(n) = In(n)×f(n) = s(n)×cos(wn)×cos(wn) = 1/2s(n)[cos(2wn)+1] (3)将信号m(n)进行低通滤波和重采样后便可得到输出信号Out(n):Out(n) = 1/2s(n) (4)由此可见,通过DDC,即保留了真实的有用信号s(n),又通过重采样使得数据量大大减少,提高了后续信号处理的效率。同样,如果在数字示波器中使用了DDC技术,不但能保留射频信号中的有用信号,同时能大大减少数据量,提高示波器的处理速度。下面我们就来讨论R&S示波器中的DDC应用。03R&S示波器硬件实现的DDC在讨论R&S示波器中的DDC应用之前,我们先来比较一下R&S数字示波器与传统数字示波器结构上的不同。

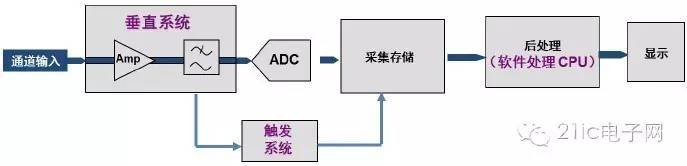

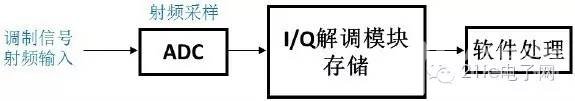

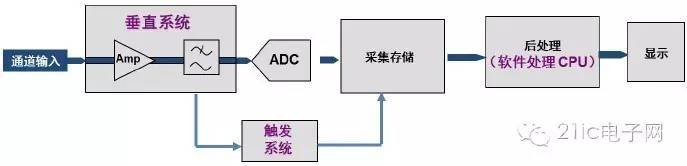

图2 传统数字示波器结构框图图2为传统数字示波器的基本结构框图。信号通过模拟通道进入示波器,经过垂直增益放大器和滤波,通过ADC转换成数字信号,由采集存储模块存储下来,再通过软件的方式进行后续的处理,最终显示在示波器屏幕上。传统数字示波器采用软件处理的方式进行数据处理,在硬件上并没有DDC的结构。因此对一些高频信号进行采集或者频谱分析的时候,必须在高采样率下进行,由于示波器本身存储空间有限,因此采集或分析的信号时间长度也相对较短。

图2 传统数字示波器结构框图图2为传统数字示波器的基本结构框图。信号通过模拟通道进入示波器,经过垂直增益放大器和滤波,通过ADC转换成数字信号,由采集存储模块存储下来,再通过软件的方式进行后续的处理,最终显示在示波器屏幕上。传统数字示波器采用软件处理的方式进行数据处理,在硬件上并没有DDC的结构。因此对一些高频信号进行采集或者频谱分析的时候,必须在高采样率下进行,由于示波器本身存储空间有限,因此采集或分析的信号时间长度也相对较短。

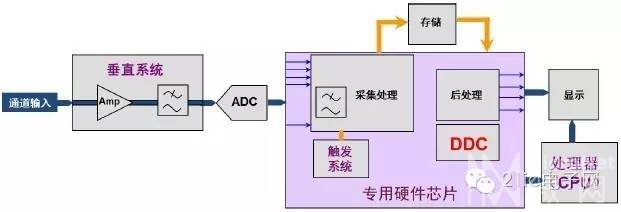

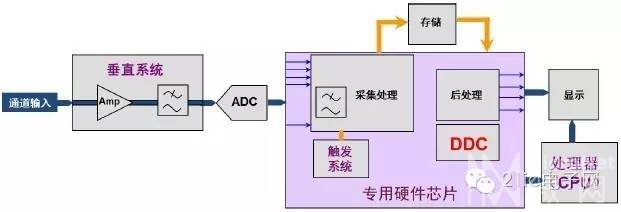

图3 R&S数字示波器结构框图图3为R&S数字示波器的基本结构框图。信号处理流程与传统数字示波器并无太大差别,但使用了较多的硬件结构,包括触发系统、数字处理、DDC等。其它硬件结构的特点与优势本文不作讨论,但可以明显的注意到该结构中使用了硬件实现的DDC。由于使用了硬件的DDC结构,可以对信号先下变频到基带,再以较低的采样率进行重采样,在相同存储空间的情况下,可以采集或分析更长时间的信号。并且由于是硬件的实现方式,速度也会较快。下面,就DDC在I/Q解调和频谱分析当中的应用进行讨论。 3.1 I/Q解调中的DDC我们先来看一个真实测试中遇到的问题:待测信号为一个载波频率为300MHz,调制带宽为2MHz的调制信号。那么如果用示波器对该信号进行采集,希望采集时间尽量长,最长可以采集多少秒时间的信号?对于这个问题,我们从信号分析的角度来进行分析。首先对于这类调制信号,军用的有雷达信号(如chirp信号),民用的有一般通信信号(如QAM信号),这些信号绝大多数为矢量信号。对于这类信号的分析,一定会用到正交解调即I/Q解调。传统数字示波器对于该类信号只能先直接对射频信号进行采集,得到数据存储下来后,再交由专用软件或者用第三方软件编程进行处理(包括I/Q解调和后续处理)。

图3 R&S数字示波器结构框图图3为R&S数字示波器的基本结构框图。信号处理流程与传统数字示波器并无太大差别,但使用了较多的硬件结构,包括触发系统、数字处理、DDC等。其它硬件结构的特点与优势本文不作讨论,但可以明显的注意到该结构中使用了硬件实现的DDC。由于使用了硬件的DDC结构,可以对信号先下变频到基带,再以较低的采样率进行重采样,在相同存储空间的情况下,可以采集或分析更长时间的信号。并且由于是硬件的实现方式,速度也会较快。下面,就DDC在I/Q解调和频谱分析当中的应用进行讨论。 3.1 I/Q解调中的DDC我们先来看一个真实测试中遇到的问题:待测信号为一个载波频率为300MHz,调制带宽为2MHz的调制信号。那么如果用示波器对该信号进行采集,希望采集时间尽量长,最长可以采集多少秒时间的信号?对于这个问题,我们从信号分析的角度来进行分析。首先对于这类调制信号,军用的有雷达信号(如chirp信号),民用的有一般通信信号(如QAM信号),这些信号绝大多数为矢量信号。对于这类信号的分析,一定会用到正交解调即I/Q解调。传统数字示波器对于该类信号只能先直接对射频信号进行采集,得到数据存储下来后,再交由专用软件或者用第三方软件编程进行处理(包括I/Q解调和后续处理)。

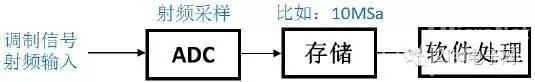

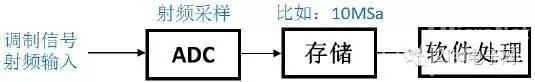

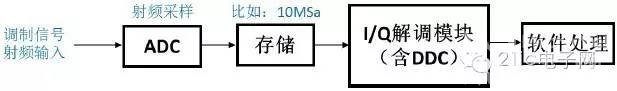

图4 传统数字示波器对调制信号处理流程图4显示了传统示波器对于该类调制信号的处理流程。针对上述问题,载波频率为300MHz,调制带宽为2MHz,那么信号的最高频率为301MHz。根据奈奎斯特采样定理,ADC所用的采样率必须为信号最高频率的2倍及以上才能真实的还原波形。我们假设传统示波器ADC使用2倍最高频率即602MSa/s的采样率进行采样(示波器采用刚好2倍关系的采样率一般是不推荐的,一般采用3~5倍的关系才能较为真实的还原波形),假设示波器存储深度为10MSa,那么所能采集信号的最长时间为10MSa / (602MSa/s) ≈ 16.6ms。即使用传统示波器对该类信号进行采集,只能采集10多毫秒时间的信号。如果针对载频更高的信号,如2GHz,采集时间则会更短。对于上述问题,R&S示波器采用了硬件实现的I/Q解调模块,其中最重要的部分就是DDC。通过使用该模块,可以采集尽可能长时间的调制信号。

图4 传统数字示波器对调制信号处理流程图4显示了传统示波器对于该类调制信号的处理流程。针对上述问题,载波频率为300MHz,调制带宽为2MHz,那么信号的最高频率为301MHz。根据奈奎斯特采样定理,ADC所用的采样率必须为信号最高频率的2倍及以上才能真实的还原波形。我们假设传统示波器ADC使用2倍最高频率即602MSa/s的采样率进行采样(示波器采用刚好2倍关系的采样率一般是不推荐的,一般采用3~5倍的关系才能较为真实的还原波形),假设示波器存储深度为10MSa,那么所能采集信号的最长时间为10MSa / (602MSa/s) ≈ 16.6ms。即使用传统示波器对该类信号进行采集,只能采集10多毫秒时间的信号。如果针对载频更高的信号,如2GHz,采集时间则会更短。对于上述问题,R&S示波器采用了硬件实现的I/Q解调模块,其中最重要的部分就是DDC。通过使用该模块,可以采集尽可能长时间的调制信号。

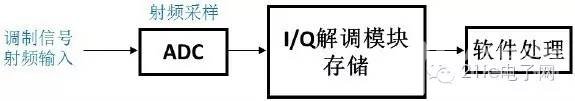

图5 R&S数字示波器对调制信号处理流程图5显示了R&S示波器对调制信号的处理流程,其中I/Q解调模块如图6所示。

图5 R&S数字示波器对调制信号处理流程图5显示了R&S示波器对调制信号的处理流程,其中I/Q解调模块如图6所示。

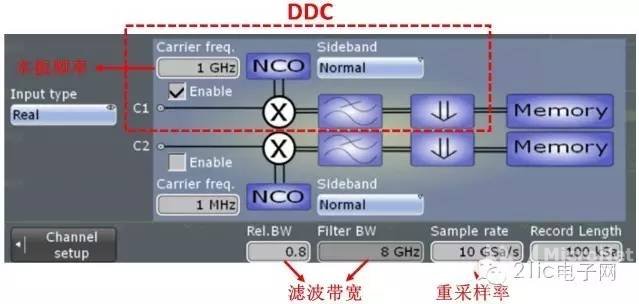

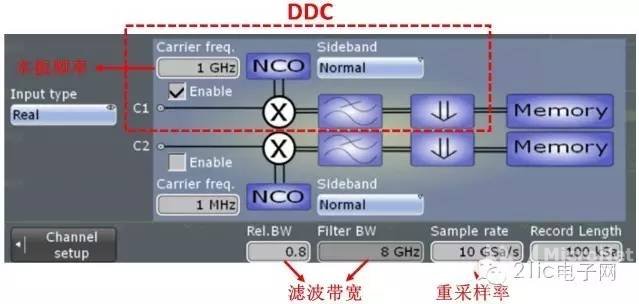

图6 R&S数字示波器I/Q解调模块R&S数字示波器在前端的ADC始终保持对射频信号以最高实时采样率进行采集(如10GSa/s或20GSa/s),转换成数字信号后再通过I/Q解调模块对数字化后的射频信号进行数字下变频、滤波得到频率较低的基带信号,最后通过重采样降低数据量,存储下来送到软件进行处理。I/Q解调模块主要由DDC构成,包括NCO、乘法器、低通滤波器和重采样几个部分构成,如图6所示。NCO负责生成本振频率,在“Carrier freq.”处设置。一般设置为与射频载波相同的频率,设置好后,NCO及产生两路正交频率相同的信号。两路正交信号分别与射频信号相乘,通过滤波得到正交的两路基带信号。滤波带宽可在“Rel.BW”处设置。在“Sample rate”处设置重采样率,最后经过重采样将基带信号保存下来。通过该种处理方式,一是可以省去软件中进行I/Q解调的处理过程。更重要的是,在示波器存储空间有限的情况下,可以存储分析更长时间的信号。例如针对本小节开头的问题,对于载波频率300MHz,调制带宽2MHz的信号,通过设置“Carrier freq.”即本振频率跟载波频率一样,为300MHz,那么经过下变频后信号变为基带,带宽就只有2MHz。重采样率“Sample rate”设置也以2倍关系来算,那么只需设置为2×2=4MSa/s。存储深度仍假设为10MSa,那么可采集和分析的信号时间则为10MSa / (4MSa/s) = 2.5s ! 时间长度一下就提高了150倍以上!对于如此高效的利用存储空间,有些朋友很是吃惊,也不免有些难以理解。可能会认为,即使加入了DDC结构,也还是数字信号处理,在前端仍存在着ADC。也就是说示波器仍需在前端对射频信号采样,仍需对射频信号满足2倍的奈奎斯特定理,那么计算下来,也只能存储16.6ms的信号,哪里来的2.5s呢。我们再仔细分析一下信号处理流程就能知晓其中的缘由。

图6 R&S数字示波器I/Q解调模块R&S数字示波器在前端的ADC始终保持对射频信号以最高实时采样率进行采集(如10GSa/s或20GSa/s),转换成数字信号后再通过I/Q解调模块对数字化后的射频信号进行数字下变频、滤波得到频率较低的基带信号,最后通过重采样降低数据量,存储下来送到软件进行处理。I/Q解调模块主要由DDC构成,包括NCO、乘法器、低通滤波器和重采样几个部分构成,如图6所示。NCO负责生成本振频率,在“Carrier freq.”处设置。一般设置为与射频载波相同的频率,设置好后,NCO及产生两路正交频率相同的信号。两路正交信号分别与射频信号相乘,通过滤波得到正交的两路基带信号。滤波带宽可在“Rel.BW”处设置。在“Sample rate”处设置重采样率,最后经过重采样将基带信号保存下来。通过该种处理方式,一是可以省去软件中进行I/Q解调的处理过程。更重要的是,在示波器存储空间有限的情况下,可以存储分析更长时间的信号。例如针对本小节开头的问题,对于载波频率300MHz,调制带宽2MHz的信号,通过设置“Carrier freq.”即本振频率跟载波频率一样,为300MHz,那么经过下变频后信号变为基带,带宽就只有2MHz。重采样率“Sample rate”设置也以2倍关系来算,那么只需设置为2×2=4MSa/s。存储深度仍假设为10MSa,那么可采集和分析的信号时间则为10MSa / (4MSa/s) = 2.5s ! 时间长度一下就提高了150倍以上!对于如此高效的利用存储空间,有些朋友很是吃惊,也不免有些难以理解。可能会认为,即使加入了DDC结构,也还是数字信号处理,在前端仍存在着ADC。也就是说示波器仍需在前端对射频信号采样,仍需对射频信号满足2倍的奈奎斯特定理,那么计算下来,也只能存储16.6ms的信号,哪里来的2.5s呢。我们再仔细分析一下信号处理流程就能知晓其中的缘由。

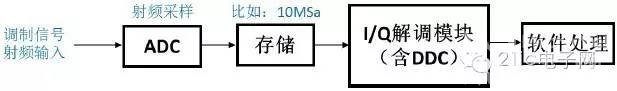

图7 一般认为的信号处理流程一般认为的信号处理流程如图7所示。对于这种结构,就如上面所理解的一样,这种情况下即使使用了DDC,仍需先将射频采集的信号先存储下来,因此还是会受高采样率的影响。对于上述例子,只能存储16.6ms的信号。但R&S示波器真正的处理流程却如图8所示。

图7 一般认为的信号处理流程一般认为的信号处理流程如图7所示。对于这种结构,就如上面所理解的一样,这种情况下即使使用了DDC,仍需先将射频采集的信号先存储下来,因此还是会受高采样率的影响。对于上述例子,只能存储16.6ms的信号。但R&S示波器真正的处理流程却如图8所示。

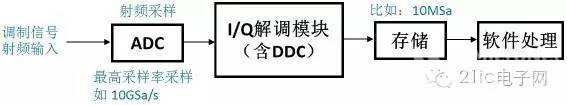

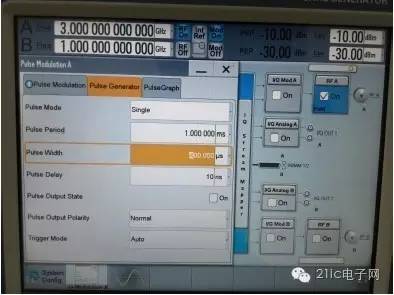

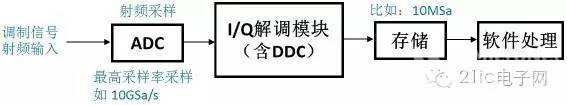

图8 R&S示波器信号处理流程在射频前端,ADC一直保持最高的实时采样率,比如10GSa/s,这样就不会造成信号混叠。经过采样后的数字信号直接送至DDC进行数字下变频。由于R&S示波器的DDC采用硬件实现,速度快,因此能进行实时处理,处理完后直接存储下来。通过这种实时的DDC处理,便能很好的节约存储空间,实现如上例所述的2.5s信号存储。对此,我们进行以下实验。首先通过信号源生成载波频率为3GHz的射频脉冲信号,调制脉冲宽度为0.4ms,脉冲重复周期为1ms。设置如图9所示:

图8 R&S示波器信号处理流程在射频前端,ADC一直保持最高的实时采样率,比如10GSa/s,这样就不会造成信号混叠。经过采样后的数字信号直接送至DDC进行数字下变频。由于R&S示波器的DDC采用硬件实现,速度快,因此能进行实时处理,处理完后直接存储下来。通过这种实时的DDC处理,便能很好的节约存储空间,实现如上例所述的2.5s信号存储。对此,我们进行以下实验。首先通过信号源生成载波频率为3GHz的射频脉冲信号,调制脉冲宽度为0.4ms,脉冲重复周期为1ms。设置如图9所示:

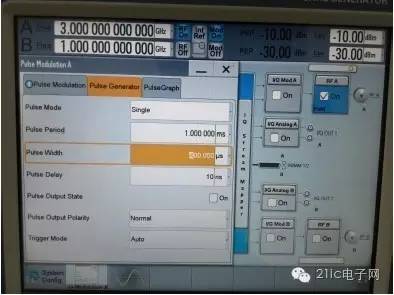

图9 载波频率3GHz的脉冲调制射频信号设置对于该信号的采集和分析,如果使用传统数字示波器,所能采集和分析的信号长度的结果等效于如图10所示:

图9 载波频率3GHz的脉冲调制射频信号设置对于该信号的采集和分析,如果使用传统数字示波器,所能采集和分析的信号长度的结果等效于如图10所示:

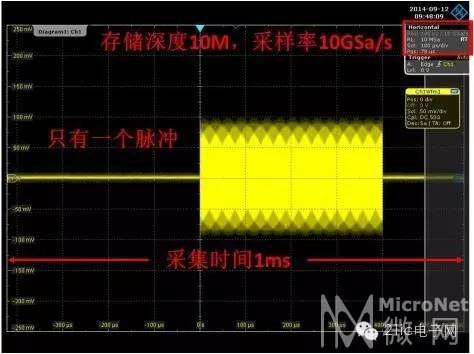

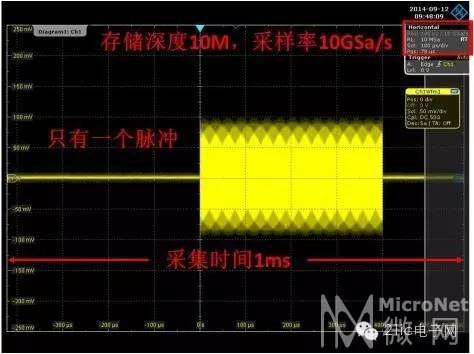

图10 传统数字示波器采集射频脉冲等效结果由于射频信号频率为3GHz,因此采样率至少为6GSa/s以上,我们设为10GSa/s。存储深度依然设置为10M,可以看出,此时只能采集到1ms时间的信号,也就是说尽能采集和分析一个脉冲信号。如果使用带有DDC结构的I/Q选件的R&S示波器进行采集分析,我们可以先设置本振频率为3GHz,将信号变为基带后,可以以更低的采样率进行采集,如设置成100MSa/s,存储深度也设置为10M。设置情况如图11所示:

图10 传统数字示波器采集射频脉冲等效结果由于射频信号频率为3GHz,因此采样率至少为6GSa/s以上,我们设为10GSa/s。存储深度依然设置为10M,可以看出,此时只能采集到1ms时间的信号,也就是说尽能采集和分析一个脉冲信号。如果使用带有DDC结构的I/Q选件的R&S示波器进行采集分析,我们可以先设置本振频率为3GHz,将信号变为基带后,可以以更低的采样率进行采集,如设置成100MSa/s,存储深度也设置为10M。设置情况如图11所示:

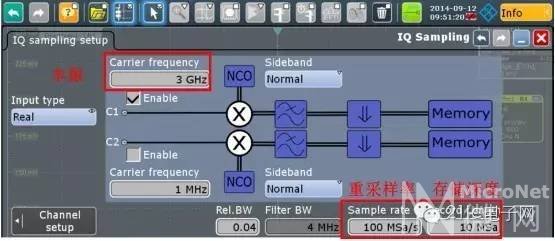

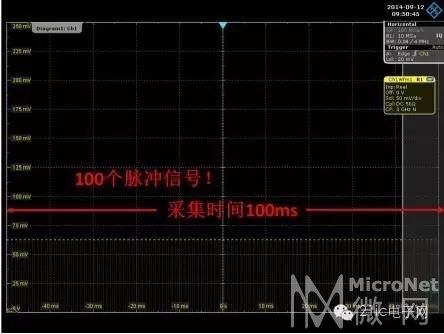

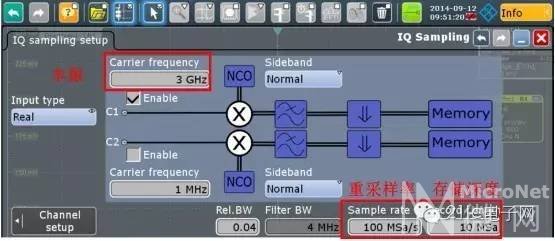

图11 R&S示波器I/Q选件设置此时进行观察,我们可以采集和分析更长时间的信号,即100ms的信号,也就是说我们可以采集和分析高达100个脉冲信号!如果重采样率设置的更低,我们能够采集和分析的信号时间还会更长。图12显示R&S示波器测试结果:

图11 R&S示波器I/Q选件设置此时进行观察,我们可以采集和分析更长时间的信号,即100ms的信号,也就是说我们可以采集和分析高达100个脉冲信号!如果重采样率设置的更低,我们能够采集和分析的信号时间还会更长。图12显示R&S示波器测试结果:

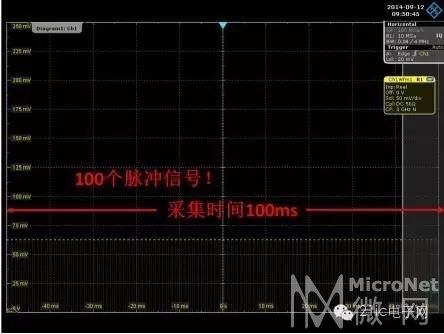

图12 R&S示波器采集射频脉冲结果综上所述,R&S示波器I/Q选件中DDC技术使得在射频信号采集和分析中,能够高效的利用有限的存储空间,采集和分析最大时间长度的信号。3.2 频谱分析中的DDC示波器频谱分析功能一般采用FFT(Fast Fourier Transformation)即快速傅里叶变换。传统数字示波器的频谱分析原理框图如图13所示。

图12 R&S示波器采集射频脉冲结果综上所述,R&S示波器I/Q选件中DDC技术使得在射频信号采集和分析中,能够高效的利用有限的存储空间,采集和分析最大时间长度的信号。3.2 频谱分析中的DDC示波器频谱分析功能一般采用FFT(Fast Fourier Transformation)即快速傅里叶变换。传统数字示波器的频谱分析原理框图如图13所示。

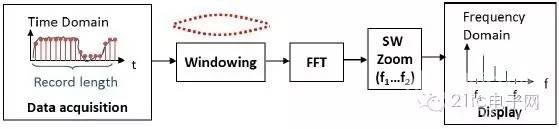

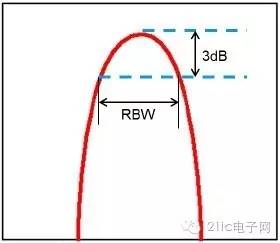

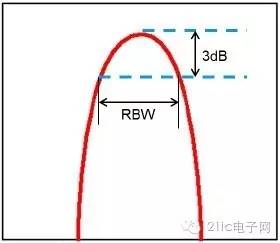

图13 传统数字示波器频谱分析框图模拟信号经过ADC后变成数字信号,之后选择不同的窗函数进行加窗处理,最后直接做FFT将信号变换到频域。通过该种处理方式得到的频谱范围为0Hz至最大频率(通常数值上等于ADC采样率的一半),例如ADC采样率为5GSa/s,那么FFT得到的频谱范围为0Hz至2.5GHz。如果要观测某一段的频谱,则通过软件显示放大(Zoom)的方式将频谱放大显示到该频段。这种传统示波器频谱分析方式的好处在于,所有处理过程采用软件计算,且算法简单,因此便于实现。但如果追求更快的实时频谱测量或者更高精度的频谱分析,这种传统的处理方式就会显得非常困难。由于采用全软件的处理方式以及一直是对整个频率范围(0Hz至最大频率)做计算,因此处理速度会很慢,无法做到实时或者准实时的频谱分析。另外在示波器设置方面也会很复杂,需要不断的调整时域参数(如时基、采样率等)来满足需要的频域参数设置。最重要的是,受到示波器存储深度的限制,并且通常使用的FFT点数只有几K,因此频率分辨率即最小能区分的频率大小会非常有限,通常情况下很难达到一个理想的频率分辨率。一般来讲,频率分辨率有两种解释。一种解释是,表示在FFT中,两个相邻频率点间的最小频率间隔,如公式(5)所示:f = fs / N = 1 / t (5)其中,f表示频率分辨率,fs表示ADC采样频率,N表示FFT的计算点数,t表示采集信号的时间长度,也就是捕获时间。可以看出,信号采集时间t越长,频率分辨率f越小,也就是频率分辨力就越好。第二种解释是,频率分辨率可以用分辨率带宽(RBW)来表示。RBW定义为窗函数主瓣3dB带宽,如图14所示:

图13 传统数字示波器频谱分析框图模拟信号经过ADC后变成数字信号,之后选择不同的窗函数进行加窗处理,最后直接做FFT将信号变换到频域。通过该种处理方式得到的频谱范围为0Hz至最大频率(通常数值上等于ADC采样率的一半),例如ADC采样率为5GSa/s,那么FFT得到的频谱范围为0Hz至2.5GHz。如果要观测某一段的频谱,则通过软件显示放大(Zoom)的方式将频谱放大显示到该频段。这种传统示波器频谱分析方式的好处在于,所有处理过程采用软件计算,且算法简单,因此便于实现。但如果追求更快的实时频谱测量或者更高精度的频谱分析,这种传统的处理方式就会显得非常困难。由于采用全软件的处理方式以及一直是对整个频率范围(0Hz至最大频率)做计算,因此处理速度会很慢,无法做到实时或者准实时的频谱分析。另外在示波器设置方面也会很复杂,需要不断的调整时域参数(如时基、采样率等)来满足需要的频域参数设置。最重要的是,受到示波器存储深度的限制,并且通常使用的FFT点数只有几K,因此频率分辨率即最小能区分的频率大小会非常有限,通常情况下很难达到一个理想的频率分辨率。一般来讲,频率分辨率有两种解释。一种解释是,表示在FFT中,两个相邻频率点间的最小频率间隔,如公式(5)所示:f = fs / N = 1 / t (5)其中,f表示频率分辨率,fs表示ADC采样频率,N表示FFT的计算点数,t表示采集信号的时间长度,也就是捕获时间。可以看出,信号采集时间t越长,频率分辨率f越小,也就是频率分辨力就越好。第二种解释是,频率分辨率可以用分辨率带宽(RBW)来表示。RBW定义为窗函数主瓣3dB带宽,如图14所示:

图14 RBW定义如果两个信号频率的差值小于该定义的带宽,即RBW,那么这两个频率将混在一起不能分辨。

图14 RBW定义如果两个信号频率的差值小于该定义的带宽,即RBW,那么这两个频率将混在一起不能分辨。

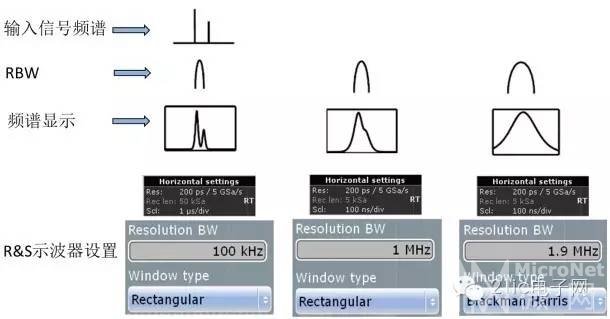

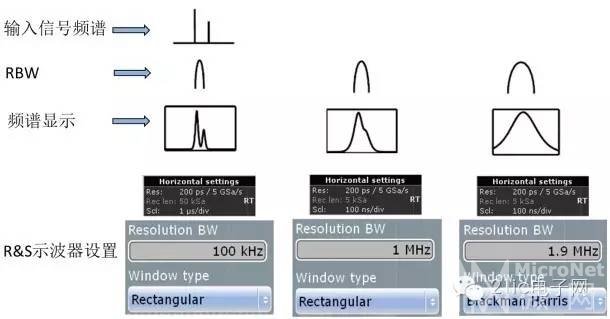

图15 不同RBW设置对应的不同频谱图15显示了对于同样频谱的输入信号,设置不同的RBW得到的完全不同的频谱。从左至右RBW依次增大,可以看出,主瓣宽度也是依次增大,频率分辨能力也是依次降低,到最右边时,已经完全不能区分信号中的两个频率了。由于DDC对频率分辨率的两种解释的影响是类似的,因此我们就只讨论第二种解释的情况,即RBW。RBW计算方式如公式(6)所示:RBW = RBWnorm × fs / N = RBWnorm / t (6)其中,RBWnorm为窗函数的归一化因子,如Blackman-Harris窗为1.8962,fs为采样频率,N为FFT计算点数,t为信号采集时间长度。从公式(6)可以看出,对于固定的窗函数,想要提高频率分辨力,即减小RBW,就必须增加信号的采集时间即捕获时间。从图15可以看出,对于固定的矩形窗,RBW从1MHz减小到100kHz,时基设置从100ns/div增大到1μs/div。但对于数字示波器来说,存储深度都是有限的。并且存储深度和捕获时间、采样率之间存在如下关系:存储深度 = 采样率 × 捕获时间 (7)从(7)式可以看出,对于固定的存储深度,采样率和捕获时间成反比关系。如果想要增加捕获时间,就意味着采样率会下降,如果采样率降低,就会意味着信号发生混叠的风险。即对于传统数字示波器的频谱分析,如果要提高频率分辨力,那么就会面临信号混叠的风险,或者说只能进行低频率信号的分析;如果要进行高频率信号的分析,为了保证采样率,那么频率分辨力必然不能提高。对于这种矛盾的关系,R&S示波器引入了DDC等一系列处理方式很好的解决了问题。

图15 不同RBW设置对应的不同频谱图15显示了对于同样频谱的输入信号,设置不同的RBW得到的完全不同的频谱。从左至右RBW依次增大,可以看出,主瓣宽度也是依次增大,频率分辨能力也是依次降低,到最右边时,已经完全不能区分信号中的两个频率了。由于DDC对频率分辨率的两种解释的影响是类似的,因此我们就只讨论第二种解释的情况,即RBW。RBW计算方式如公式(6)所示:RBW = RBWnorm × fs / N = RBWnorm / t (6)其中,RBWnorm为窗函数的归一化因子,如Blackman-Harris窗为1.8962,fs为采样频率,N为FFT计算点数,t为信号采集时间长度。从公式(6)可以看出,对于固定的窗函数,想要提高频率分辨力,即减小RBW,就必须增加信号的采集时间即捕获时间。从图15可以看出,对于固定的矩形窗,RBW从1MHz减小到100kHz,时基设置从100ns/div增大到1μs/div。但对于数字示波器来说,存储深度都是有限的。并且存储深度和捕获时间、采样率之间存在如下关系:存储深度 = 采样率 × 捕获时间 (7)从(7)式可以看出,对于固定的存储深度,采样率和捕获时间成反比关系。如果想要增加捕获时间,就意味着采样率会下降,如果采样率降低,就会意味着信号发生混叠的风险。即对于传统数字示波器的频谱分析,如果要提高频率分辨力,那么就会面临信号混叠的风险,或者说只能进行低频率信号的分析;如果要进行高频率信号的分析,为了保证采样率,那么频率分辨力必然不能提高。对于这种矛盾的关系,R&S示波器引入了DDC等一系列处理方式很好的解决了问题。

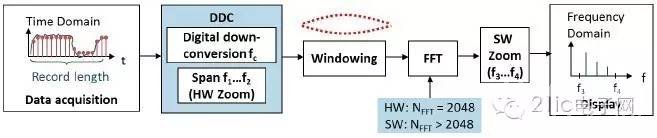

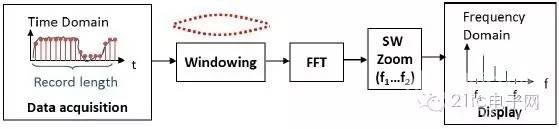

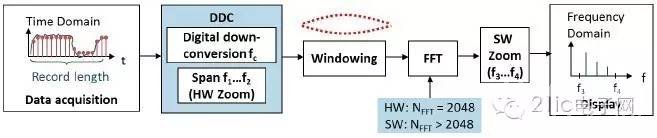

图16 R&S数字示波器频谱分析框图图16显示了R&S示波器的频谱分析流程,图17显示了频谱分析设置框图。

图16 R&S数字示波器频谱分析框图图16显示了R&S示波器的频谱分析流程,图17显示了频谱分析设置框图。

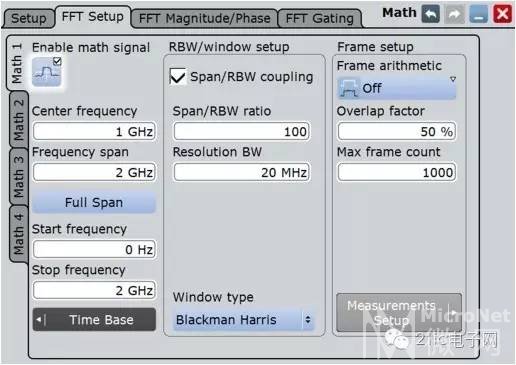

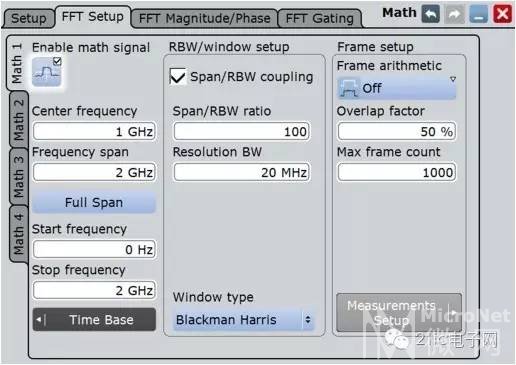

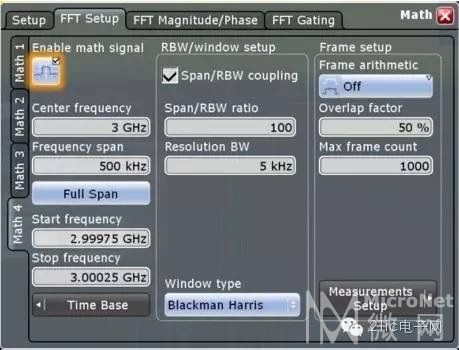

图17 R&S数字示波器频谱分析设置与传统数字示波器相比,R&S示波器引入了DDC模块,使信号在FFT之前先下变频到基带。设置中心频率Center frequency等效于设置本振频率,使信号下变频到基带,因此对基带信号进行重采样时,即使用较低的采样频率也不会造成信号混叠,从而在有限的存储空间中能采集最长时间的信号,因此频率分辨率(RBW)能够得到有效的保证。通过设置频率跨度Frequency span,可以在硬件上将FFT的计算范围缩小到所设定的带宽内,而不用对整个频率范围都进行FFT计算,从而提高处理速度。此外,FFT的计算方式也采用分段重叠的计算方式,从而能够更好的体现出频谱的细节。总之,与传统数字示波器频谱分析相比,采用R&S示波器频谱分析结构主要具有如下几点好处: 由于采用硬件处理等方式,频谱分析速度快,能做到实时的频谱分析; 频谱分析设置同频谱分析仪类似,直接对频谱参数进行设置,而不再需要进行复杂的时域参数调整; 具有大的动态范围; 即本文讨论的重点,由于采用了DDC结构,可以将信号先下变频到基带,再以较低的采样频率对其进行重采样,从而在有限的存储空间内能够采集最长时间的信号,根据公式(6)可以很好的保证频率分辨率(RBW)。即不用再在信号频率与RBW之间纠结折衷的方案。对此我们进行以下实验。使用信号源产生频率为3GHz的单频正弦波信号。如果使用传统示波器频谱分析方法,采样率必须设置为6GSa/s以上信号才不至于混叠,那么根据公式(6)和(7),在有限的存储空间内必不能得到很好的RBW。但如果使用R&S示波器频谱分析方法,设置如图18所示:

图17 R&S数字示波器频谱分析设置与传统数字示波器相比,R&S示波器引入了DDC模块,使信号在FFT之前先下变频到基带。设置中心频率Center frequency等效于设置本振频率,使信号下变频到基带,因此对基带信号进行重采样时,即使用较低的采样频率也不会造成信号混叠,从而在有限的存储空间中能采集最长时间的信号,因此频率分辨率(RBW)能够得到有效的保证。通过设置频率跨度Frequency span,可以在硬件上将FFT的计算范围缩小到所设定的带宽内,而不用对整个频率范围都进行FFT计算,从而提高处理速度。此外,FFT的计算方式也采用分段重叠的计算方式,从而能够更好的体现出频谱的细节。总之,与传统数字示波器频谱分析相比,采用R&S示波器频谱分析结构主要具有如下几点好处: 由于采用硬件处理等方式,频谱分析速度快,能做到实时的频谱分析; 频谱分析设置同频谱分析仪类似,直接对频谱参数进行设置,而不再需要进行复杂的时域参数调整; 具有大的动态范围; 即本文讨论的重点,由于采用了DDC结构,可以将信号先下变频到基带,再以较低的采样频率对其进行重采样,从而在有限的存储空间内能够采集最长时间的信号,根据公式(6)可以很好的保证频率分辨率(RBW)。即不用再在信号频率与RBW之间纠结折衷的方案。对此我们进行以下实验。使用信号源产生频率为3GHz的单频正弦波信号。如果使用传统示波器频谱分析方法,采样率必须设置为6GSa/s以上信号才不至于混叠,那么根据公式(6)和(7),在有限的存储空间内必不能得到很好的RBW。但如果使用R&S示波器频谱分析方法,设置如图18所示:

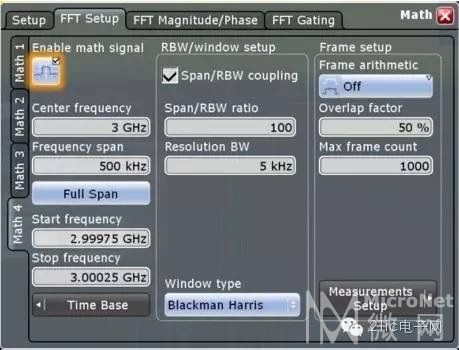

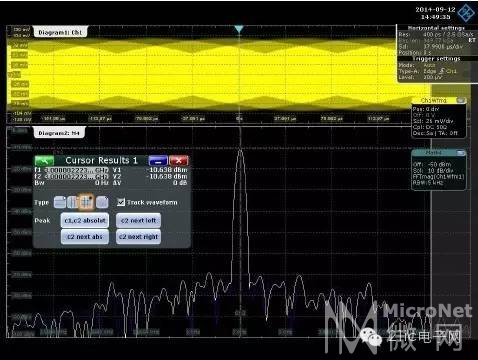

图18 R&S数字示波器频谱分析设置中心频率设为3GHz,RBW设为5kHz,窗函数采用Blackman Harris窗。频谱分析结果如图19所示。我们注意到,由于采用了DDC结构,采样率设置为了2.5GSa/s,并不需要满足信号频率的2倍以上关系,因为此时的采样率在频谱分析中实际为重采样率。在频域测量结果中可以看出,信号频率为3GHz,与信号源输出频率一致。因此,可以看出使用R&S示波器频谱分析结构,即使对于高频率的信号,仍然能够有很好的频率分辨率。

图18 R&S数字示波器频谱分析设置中心频率设为3GHz,RBW设为5kHz,窗函数采用Blackman Harris窗。频谱分析结果如图19所示。我们注意到,由于采用了DDC结构,采样率设置为了2.5GSa/s,并不需要满足信号频率的2倍以上关系,因为此时的采样率在频谱分析中实际为重采样率。在频域测量结果中可以看出,信号频率为3GHz,与信号源输出频率一致。因此,可以看出使用R&S示波器频谱分析结构,即使对于高频率的信号,仍然能够有很好的频率分辨率。

图19 R&S数字示波器频谱分析结果04小结通过以上讨论可以看出,R&S数字示波器采用DDC技术,无论是在射频信号采集分析(I/Q解调)还是在频域分析中,都能最大限度的利用示波器宝贵的存储空间,将信号的多域联合分析发挥的淋漓尽致。特别推荐互相鄙视的“模电”和“数电”约了一架,结果发现……

图19 R&S数字示波器频谱分析结果04小结通过以上讨论可以看出,R&S数字示波器采用DDC技术,无论是在射频信号采集分析(I/Q解调)还是在频域分析中,都能最大限度的利用示波器宝贵的存储空间,将信号的多域联合分析发挥的淋漓尽致。特别推荐互相鄙视的“模电”和“数电”约了一架,结果发现……

VCC、 VDD、VEE、VSS 电压理解

VCC、 VDD、VEE、VSS 电压理解

涨姿势!高手带你全面了解嵌入式C语言可靠性设计

涨姿势!高手带你全面了解嵌入式C语言可靠性设计

图1 DDC原理框图图1为DDC原理框图,主要由NCO、混频器、低通滤波器和重采样几个模块组成。射频信号通过高速ADC后变为数字信号In(n):In(n) = s(n)×cos(wn) (1)其中,s(n)为信号,cos(wn)为载波,w为载波频率。NCO产生与射频信号频率相同的本振信号f(n):f(n) = cos(wn) (2)本振信号与射频信号混频相乘后得到信号m(n):m(n) = In(n)×f(n) = s(n)×cos(wn)×cos(wn) = 1/2s(n)[cos(2wn)+1] (3)将信号m(n)进行低通滤波和重采样后便可得到输出信号Out(n):Out(n) = 1/2s(n) (4)由此可见,通过DDC,即保留了真实的有用信号s(n),又通过重采样使得数据量大大减少,提高了后续信号处理的效率。同样,如果在数字示波器中使用了DDC技术,不但能保留射频信号中的有用信号,同时能大大减少数据量,提高示波器的处理速度。下面我们就来讨论R&S示波器中的DDC应用。03R&S示波器硬件实现的DDC在讨论R&S示波器中的DDC应用之前,我们先来比较一下R&S数字示波器与传统数字示波器结构上的不同。

图1 DDC原理框图图1为DDC原理框图,主要由NCO、混频器、低通滤波器和重采样几个模块组成。射频信号通过高速ADC后变为数字信号In(n):In(n) = s(n)×cos(wn) (1)其中,s(n)为信号,cos(wn)为载波,w为载波频率。NCO产生与射频信号频率相同的本振信号f(n):f(n) = cos(wn) (2)本振信号与射频信号混频相乘后得到信号m(n):m(n) = In(n)×f(n) = s(n)×cos(wn)×cos(wn) = 1/2s(n)[cos(2wn)+1] (3)将信号m(n)进行低通滤波和重采样后便可得到输出信号Out(n):Out(n) = 1/2s(n) (4)由此可见,通过DDC,即保留了真实的有用信号s(n),又通过重采样使得数据量大大减少,提高了后续信号处理的效率。同样,如果在数字示波器中使用了DDC技术,不但能保留射频信号中的有用信号,同时能大大减少数据量,提高示波器的处理速度。下面我们就来讨论R&S示波器中的DDC应用。03R&S示波器硬件实现的DDC在讨论R&S示波器中的DDC应用之前,我们先来比较一下R&S数字示波器与传统数字示波器结构上的不同。 图2 传统数字示波器结构框图图2为传统数字示波器的基本结构框图。信号通过模拟通道进入示波器,经过垂直增益放大器和滤波,通过ADC转换成数字信号,由采集存储模块存储下来,再通过软件的方式进行后续的处理,最终显示在示波器屏幕上。传统数字示波器采用软件处理的方式进行数据处理,在硬件上并没有DDC的结构。因此对一些高频信号进行采集或者频谱分析的时候,必须在高采样率下进行,由于示波器本身存储空间有限,因此采集或分析的信号时间长度也相对较短。

图2 传统数字示波器结构框图图2为传统数字示波器的基本结构框图。信号通过模拟通道进入示波器,经过垂直增益放大器和滤波,通过ADC转换成数字信号,由采集存储模块存储下来,再通过软件的方式进行后续的处理,最终显示在示波器屏幕上。传统数字示波器采用软件处理的方式进行数据处理,在硬件上并没有DDC的结构。因此对一些高频信号进行采集或者频谱分析的时候,必须在高采样率下进行,由于示波器本身存储空间有限,因此采集或分析的信号时间长度也相对较短。 图3 R&S数字示波器结构框图图3为R&S数字示波器的基本结构框图。信号处理流程与传统数字示波器并无太大差别,但使用了较多的硬件结构,包括触发系统、数字处理、DDC等。其它硬件结构的特点与优势本文不作讨论,但可以明显的注意到该结构中使用了硬件实现的DDC。由于使用了硬件的DDC结构,可以对信号先下变频到基带,再以较低的采样率进行重采样,在相同存储空间的情况下,可以采集或分析更长时间的信号。并且由于是硬件的实现方式,速度也会较快。下面,就DDC在I/Q解调和频谱分析当中的应用进行讨论。 3.1 I/Q解调中的DDC我们先来看一个真实测试中遇到的问题:待测信号为一个载波频率为300MHz,调制带宽为2MHz的调制信号。那么如果用示波器对该信号进行采集,希望采集时间尽量长,最长可以采集多少秒时间的信号?对于这个问题,我们从信号分析的角度来进行分析。首先对于这类调制信号,军用的有雷达信号(如chirp信号),民用的有一般通信信号(如QAM信号),这些信号绝大多数为矢量信号。对于这类信号的分析,一定会用到正交解调即I/Q解调。传统数字示波器对于该类信号只能先直接对射频信号进行采集,得到数据存储下来后,再交由专用软件或者用第三方软件编程进行处理(包括I/Q解调和后续处理)。

图3 R&S数字示波器结构框图图3为R&S数字示波器的基本结构框图。信号处理流程与传统数字示波器并无太大差别,但使用了较多的硬件结构,包括触发系统、数字处理、DDC等。其它硬件结构的特点与优势本文不作讨论,但可以明显的注意到该结构中使用了硬件实现的DDC。由于使用了硬件的DDC结构,可以对信号先下变频到基带,再以较低的采样率进行重采样,在相同存储空间的情况下,可以采集或分析更长时间的信号。并且由于是硬件的实现方式,速度也会较快。下面,就DDC在I/Q解调和频谱分析当中的应用进行讨论。 3.1 I/Q解调中的DDC我们先来看一个真实测试中遇到的问题:待测信号为一个载波频率为300MHz,调制带宽为2MHz的调制信号。那么如果用示波器对该信号进行采集,希望采集时间尽量长,最长可以采集多少秒时间的信号?对于这个问题,我们从信号分析的角度来进行分析。首先对于这类调制信号,军用的有雷达信号(如chirp信号),民用的有一般通信信号(如QAM信号),这些信号绝大多数为矢量信号。对于这类信号的分析,一定会用到正交解调即I/Q解调。传统数字示波器对于该类信号只能先直接对射频信号进行采集,得到数据存储下来后,再交由专用软件或者用第三方软件编程进行处理(包括I/Q解调和后续处理)。 图4 传统数字示波器对调制信号处理流程图4显示了传统示波器对于该类调制信号的处理流程。针对上述问题,载波频率为300MHz,调制带宽为2MHz,那么信号的最高频率为301MHz。根据奈奎斯特采样定理,ADC所用的采样率必须为信号最高频率的2倍及以上才能真实的还原波形。我们假设传统示波器ADC使用2倍最高频率即602MSa/s的采样率进行采样(示波器采用刚好2倍关系的采样率一般是不推荐的,一般采用3~5倍的关系才能较为真实的还原波形),假设示波器存储深度为10MSa,那么所能采集信号的最长时间为10MSa / (602MSa/s) ≈ 16.6ms。即使用传统示波器对该类信号进行采集,只能采集10多毫秒时间的信号。如果针对载频更高的信号,如2GHz,采集时间则会更短。对于上述问题,R&S示波器采用了硬件实现的I/Q解调模块,其中最重要的部分就是DDC。通过使用该模块,可以采集尽可能长时间的调制信号。

图4 传统数字示波器对调制信号处理流程图4显示了传统示波器对于该类调制信号的处理流程。针对上述问题,载波频率为300MHz,调制带宽为2MHz,那么信号的最高频率为301MHz。根据奈奎斯特采样定理,ADC所用的采样率必须为信号最高频率的2倍及以上才能真实的还原波形。我们假设传统示波器ADC使用2倍最高频率即602MSa/s的采样率进行采样(示波器采用刚好2倍关系的采样率一般是不推荐的,一般采用3~5倍的关系才能较为真实的还原波形),假设示波器存储深度为10MSa,那么所能采集信号的最长时间为10MSa / (602MSa/s) ≈ 16.6ms。即使用传统示波器对该类信号进行采集,只能采集10多毫秒时间的信号。如果针对载频更高的信号,如2GHz,采集时间则会更短。对于上述问题,R&S示波器采用了硬件实现的I/Q解调模块,其中最重要的部分就是DDC。通过使用该模块,可以采集尽可能长时间的调制信号。 图5 R&S数字示波器对调制信号处理流程图5显示了R&S示波器对调制信号的处理流程,其中I/Q解调模块如图6所示。

图5 R&S数字示波器对调制信号处理流程图5显示了R&S示波器对调制信号的处理流程,其中I/Q解调模块如图6所示。 图6 R&S数字示波器I/Q解调模块R&S数字示波器在前端的ADC始终保持对射频信号以最高实时采样率进行采集(如10GSa/s或20GSa/s),转换成数字信号后再通过I/Q解调模块对数字化后的射频信号进行数字下变频、滤波得到频率较低的基带信号,最后通过重采样降低数据量,存储下来送到软件进行处理。I/Q解调模块主要由DDC构成,包括NCO、乘法器、低通滤波器和重采样几个部分构成,如图6所示。NCO负责生成本振频率,在“Carrier freq.”处设置。一般设置为与射频载波相同的频率,设置好后,NCO及产生两路正交频率相同的信号。两路正交信号分别与射频信号相乘,通过滤波得到正交的两路基带信号。滤波带宽可在“Rel.BW”处设置。在“Sample rate”处设置重采样率,最后经过重采样将基带信号保存下来。通过该种处理方式,一是可以省去软件中进行I/Q解调的处理过程。更重要的是,在示波器存储空间有限的情况下,可以存储分析更长时间的信号。例如针对本小节开头的问题,对于载波频率300MHz,调制带宽2MHz的信号,通过设置“Carrier freq.”即本振频率跟载波频率一样,为300MHz,那么经过下变频后信号变为基带,带宽就只有2MHz。重采样率“Sample rate”设置也以2倍关系来算,那么只需设置为2×2=4MSa/s。存储深度仍假设为10MSa,那么可采集和分析的信号时间则为10MSa / (4MSa/s) = 2.5s ! 时间长度一下就提高了150倍以上!对于如此高效的利用存储空间,有些朋友很是吃惊,也不免有些难以理解。可能会认为,即使加入了DDC结构,也还是数字信号处理,在前端仍存在着ADC。也就是说示波器仍需在前端对射频信号采样,仍需对射频信号满足2倍的奈奎斯特定理,那么计算下来,也只能存储16.6ms的信号,哪里来的2.5s呢。我们再仔细分析一下信号处理流程就能知晓其中的缘由。

图6 R&S数字示波器I/Q解调模块R&S数字示波器在前端的ADC始终保持对射频信号以最高实时采样率进行采集(如10GSa/s或20GSa/s),转换成数字信号后再通过I/Q解调模块对数字化后的射频信号进行数字下变频、滤波得到频率较低的基带信号,最后通过重采样降低数据量,存储下来送到软件进行处理。I/Q解调模块主要由DDC构成,包括NCO、乘法器、低通滤波器和重采样几个部分构成,如图6所示。NCO负责生成本振频率,在“Carrier freq.”处设置。一般设置为与射频载波相同的频率,设置好后,NCO及产生两路正交频率相同的信号。两路正交信号分别与射频信号相乘,通过滤波得到正交的两路基带信号。滤波带宽可在“Rel.BW”处设置。在“Sample rate”处设置重采样率,最后经过重采样将基带信号保存下来。通过该种处理方式,一是可以省去软件中进行I/Q解调的处理过程。更重要的是,在示波器存储空间有限的情况下,可以存储分析更长时间的信号。例如针对本小节开头的问题,对于载波频率300MHz,调制带宽2MHz的信号,通过设置“Carrier freq.”即本振频率跟载波频率一样,为300MHz,那么经过下变频后信号变为基带,带宽就只有2MHz。重采样率“Sample rate”设置也以2倍关系来算,那么只需设置为2×2=4MSa/s。存储深度仍假设为10MSa,那么可采集和分析的信号时间则为10MSa / (4MSa/s) = 2.5s ! 时间长度一下就提高了150倍以上!对于如此高效的利用存储空间,有些朋友很是吃惊,也不免有些难以理解。可能会认为,即使加入了DDC结构,也还是数字信号处理,在前端仍存在着ADC。也就是说示波器仍需在前端对射频信号采样,仍需对射频信号满足2倍的奈奎斯特定理,那么计算下来,也只能存储16.6ms的信号,哪里来的2.5s呢。我们再仔细分析一下信号处理流程就能知晓其中的缘由。 图7 一般认为的信号处理流程一般认为的信号处理流程如图7所示。对于这种结构,就如上面所理解的一样,这种情况下即使使用了DDC,仍需先将射频采集的信号先存储下来,因此还是会受高采样率的影响。对于上述例子,只能存储16.6ms的信号。但R&S示波器真正的处理流程却如图8所示。

图7 一般认为的信号处理流程一般认为的信号处理流程如图7所示。对于这种结构,就如上面所理解的一样,这种情况下即使使用了DDC,仍需先将射频采集的信号先存储下来,因此还是会受高采样率的影响。对于上述例子,只能存储16.6ms的信号。但R&S示波器真正的处理流程却如图8所示。 图8 R&S示波器信号处理流程在射频前端,ADC一直保持最高的实时采样率,比如10GSa/s,这样就不会造成信号混叠。经过采样后的数字信号直接送至DDC进行数字下变频。由于R&S示波器的DDC采用硬件实现,速度快,因此能进行实时处理,处理完后直接存储下来。通过这种实时的DDC处理,便能很好的节约存储空间,实现如上例所述的2.5s信号存储。对此,我们进行以下实验。首先通过信号源生成载波频率为3GHz的射频脉冲信号,调制脉冲宽度为0.4ms,脉冲重复周期为1ms。设置如图9所示:

图8 R&S示波器信号处理流程在射频前端,ADC一直保持最高的实时采样率,比如10GSa/s,这样就不会造成信号混叠。经过采样后的数字信号直接送至DDC进行数字下变频。由于R&S示波器的DDC采用硬件实现,速度快,因此能进行实时处理,处理完后直接存储下来。通过这种实时的DDC处理,便能很好的节约存储空间,实现如上例所述的2.5s信号存储。对此,我们进行以下实验。首先通过信号源生成载波频率为3GHz的射频脉冲信号,调制脉冲宽度为0.4ms,脉冲重复周期为1ms。设置如图9所示: 图9 载波频率3GHz的脉冲调制射频信号设置对于该信号的采集和分析,如果使用传统数字示波器,所能采集和分析的信号长度的结果等效于如图10所示:

图9 载波频率3GHz的脉冲调制射频信号设置对于该信号的采集和分析,如果使用传统数字示波器,所能采集和分析的信号长度的结果等效于如图10所示: 图10 传统数字示波器采集射频脉冲等效结果由于射频信号频率为3GHz,因此采样率至少为6GSa/s以上,我们设为10GSa/s。存储深度依然设置为10M,可以看出,此时只能采集到1ms时间的信号,也就是说尽能采集和分析一个脉冲信号。如果使用带有DDC结构的I/Q选件的R&S示波器进行采集分析,我们可以先设置本振频率为3GHz,将信号变为基带后,可以以更低的采样率进行采集,如设置成100MSa/s,存储深度也设置为10M。设置情况如图11所示:

图10 传统数字示波器采集射频脉冲等效结果由于射频信号频率为3GHz,因此采样率至少为6GSa/s以上,我们设为10GSa/s。存储深度依然设置为10M,可以看出,此时只能采集到1ms时间的信号,也就是说尽能采集和分析一个脉冲信号。如果使用带有DDC结构的I/Q选件的R&S示波器进行采集分析,我们可以先设置本振频率为3GHz,将信号变为基带后,可以以更低的采样率进行采集,如设置成100MSa/s,存储深度也设置为10M。设置情况如图11所示: 图11 R&S示波器I/Q选件设置此时进行观察,我们可以采集和分析更长时间的信号,即100ms的信号,也就是说我们可以采集和分析高达100个脉冲信号!如果重采样率设置的更低,我们能够采集和分析的信号时间还会更长。图12显示R&S示波器测试结果:

图11 R&S示波器I/Q选件设置此时进行观察,我们可以采集和分析更长时间的信号,即100ms的信号,也就是说我们可以采集和分析高达100个脉冲信号!如果重采样率设置的更低,我们能够采集和分析的信号时间还会更长。图12显示R&S示波器测试结果: 图12 R&S示波器采集射频脉冲结果综上所述,R&S示波器I/Q选件中DDC技术使得在射频信号采集和分析中,能够高效的利用有限的存储空间,采集和分析最大时间长度的信号。3.2 频谱分析中的DDC示波器频谱分析功能一般采用FFT(Fast Fourier Transformation)即快速傅里叶变换。传统数字示波器的频谱分析原理框图如图13所示。

图12 R&S示波器采集射频脉冲结果综上所述,R&S示波器I/Q选件中DDC技术使得在射频信号采集和分析中,能够高效的利用有限的存储空间,采集和分析最大时间长度的信号。3.2 频谱分析中的DDC示波器频谱分析功能一般采用FFT(Fast Fourier Transformation)即快速傅里叶变换。传统数字示波器的频谱分析原理框图如图13所示。 图13 传统数字示波器频谱分析框图模拟信号经过ADC后变成数字信号,之后选择不同的窗函数进行加窗处理,最后直接做FFT将信号变换到频域。通过该种处理方式得到的频谱范围为0Hz至最大频率(通常数值上等于ADC采样率的一半),例如ADC采样率为5GSa/s,那么FFT得到的频谱范围为0Hz至2.5GHz。如果要观测某一段的频谱,则通过软件显示放大(Zoom)的方式将频谱放大显示到该频段。这种传统示波器频谱分析方式的好处在于,所有处理过程采用软件计算,且算法简单,因此便于实现。但如果追求更快的实时频谱测量或者更高精度的频谱分析,这种传统的处理方式就会显得非常困难。由于采用全软件的处理方式以及一直是对整个频率范围(0Hz至最大频率)做计算,因此处理速度会很慢,无法做到实时或者准实时的频谱分析。另外在示波器设置方面也会很复杂,需要不断的调整时域参数(如时基、采样率等)来满足需要的频域参数设置。最重要的是,受到示波器存储深度的限制,并且通常使用的FFT点数只有几K,因此频率分辨率即最小能区分的频率大小会非常有限,通常情况下很难达到一个理想的频率分辨率。一般来讲,频率分辨率有两种解释。一种解释是,表示在FFT中,两个相邻频率点间的最小频率间隔,如公式(5)所示:f = fs / N = 1 / t (5)其中,f表示频率分辨率,fs表示ADC采样频率,N表示FFT的计算点数,t表示采集信号的时间长度,也就是捕获时间。可以看出,信号采集时间t越长,频率分辨率f越小,也就是频率分辨力就越好。第二种解释是,频率分辨率可以用分辨率带宽(RBW)来表示。RBW定义为窗函数主瓣3dB带宽,如图14所示:

图13 传统数字示波器频谱分析框图模拟信号经过ADC后变成数字信号,之后选择不同的窗函数进行加窗处理,最后直接做FFT将信号变换到频域。通过该种处理方式得到的频谱范围为0Hz至最大频率(通常数值上等于ADC采样率的一半),例如ADC采样率为5GSa/s,那么FFT得到的频谱范围为0Hz至2.5GHz。如果要观测某一段的频谱,则通过软件显示放大(Zoom)的方式将频谱放大显示到该频段。这种传统示波器频谱分析方式的好处在于,所有处理过程采用软件计算,且算法简单,因此便于实现。但如果追求更快的实时频谱测量或者更高精度的频谱分析,这种传统的处理方式就会显得非常困难。由于采用全软件的处理方式以及一直是对整个频率范围(0Hz至最大频率)做计算,因此处理速度会很慢,无法做到实时或者准实时的频谱分析。另外在示波器设置方面也会很复杂,需要不断的调整时域参数(如时基、采样率等)来满足需要的频域参数设置。最重要的是,受到示波器存储深度的限制,并且通常使用的FFT点数只有几K,因此频率分辨率即最小能区分的频率大小会非常有限,通常情况下很难达到一个理想的频率分辨率。一般来讲,频率分辨率有两种解释。一种解释是,表示在FFT中,两个相邻频率点间的最小频率间隔,如公式(5)所示:f = fs / N = 1 / t (5)其中,f表示频率分辨率,fs表示ADC采样频率,N表示FFT的计算点数,t表示采集信号的时间长度,也就是捕获时间。可以看出,信号采集时间t越长,频率分辨率f越小,也就是频率分辨力就越好。第二种解释是,频率分辨率可以用分辨率带宽(RBW)来表示。RBW定义为窗函数主瓣3dB带宽,如图14所示: 图14 RBW定义如果两个信号频率的差值小于该定义的带宽,即RBW,那么这两个频率将混在一起不能分辨。

图14 RBW定义如果两个信号频率的差值小于该定义的带宽,即RBW,那么这两个频率将混在一起不能分辨。 图15 不同RBW设置对应的不同频谱图15显示了对于同样频谱的输入信号,设置不同的RBW得到的完全不同的频谱。从左至右RBW依次增大,可以看出,主瓣宽度也是依次增大,频率分辨能力也是依次降低,到最右边时,已经完全不能区分信号中的两个频率了。由于DDC对频率分辨率的两种解释的影响是类似的,因此我们就只讨论第二种解释的情况,即RBW。RBW计算方式如公式(6)所示:RBW = RBWnorm × fs / N = RBWnorm / t (6)其中,RBWnorm为窗函数的归一化因子,如Blackman-Harris窗为1.8962,fs为采样频率,N为FFT计算点数,t为信号采集时间长度。从公式(6)可以看出,对于固定的窗函数,想要提高频率分辨力,即减小RBW,就必须增加信号的采集时间即捕获时间。从图15可以看出,对于固定的矩形窗,RBW从1MHz减小到100kHz,时基设置从100ns/div增大到1μs/div。但对于数字示波器来说,存储深度都是有限的。并且存储深度和捕获时间、采样率之间存在如下关系:存储深度 = 采样率 × 捕获时间 (7)从(7)式可以看出,对于固定的存储深度,采样率和捕获时间成反比关系。如果想要增加捕获时间,就意味着采样率会下降,如果采样率降低,就会意味着信号发生混叠的风险。即对于传统数字示波器的频谱分析,如果要提高频率分辨力,那么就会面临信号混叠的风险,或者说只能进行低频率信号的分析;如果要进行高频率信号的分析,为了保证采样率,那么频率分辨力必然不能提高。对于这种矛盾的关系,R&S示波器引入了DDC等一系列处理方式很好的解决了问题。

图15 不同RBW设置对应的不同频谱图15显示了对于同样频谱的输入信号,设置不同的RBW得到的完全不同的频谱。从左至右RBW依次增大,可以看出,主瓣宽度也是依次增大,频率分辨能力也是依次降低,到最右边时,已经完全不能区分信号中的两个频率了。由于DDC对频率分辨率的两种解释的影响是类似的,因此我们就只讨论第二种解释的情况,即RBW。RBW计算方式如公式(6)所示:RBW = RBWnorm × fs / N = RBWnorm / t (6)其中,RBWnorm为窗函数的归一化因子,如Blackman-Harris窗为1.8962,fs为采样频率,N为FFT计算点数,t为信号采集时间长度。从公式(6)可以看出,对于固定的窗函数,想要提高频率分辨力,即减小RBW,就必须增加信号的采集时间即捕获时间。从图15可以看出,对于固定的矩形窗,RBW从1MHz减小到100kHz,时基设置从100ns/div增大到1μs/div。但对于数字示波器来说,存储深度都是有限的。并且存储深度和捕获时间、采样率之间存在如下关系:存储深度 = 采样率 × 捕获时间 (7)从(7)式可以看出,对于固定的存储深度,采样率和捕获时间成反比关系。如果想要增加捕获时间,就意味着采样率会下降,如果采样率降低,就会意味着信号发生混叠的风险。即对于传统数字示波器的频谱分析,如果要提高频率分辨力,那么就会面临信号混叠的风险,或者说只能进行低频率信号的分析;如果要进行高频率信号的分析,为了保证采样率,那么频率分辨力必然不能提高。对于这种矛盾的关系,R&S示波器引入了DDC等一系列处理方式很好的解决了问题。 图16 R&S数字示波器频谱分析框图图16显示了R&S示波器的频谱分析流程,图17显示了频谱分析设置框图。

图16 R&S数字示波器频谱分析框图图16显示了R&S示波器的频谱分析流程,图17显示了频谱分析设置框图。 图17 R&S数字示波器频谱分析设置与传统数字示波器相比,R&S示波器引入了DDC模块,使信号在FFT之前先下变频到基带。设置中心频率Center frequency等效于设置本振频率,使信号下变频到基带,因此对基带信号进行重采样时,即使用较低的采样频率也不会造成信号混叠,从而在有限的存储空间中能采集最长时间的信号,因此频率分辨率(RBW)能够得到有效的保证。通过设置频率跨度Frequency span,可以在硬件上将FFT的计算范围缩小到所设定的带宽内,而不用对整个频率范围都进行FFT计算,从而提高处理速度。此外,FFT的计算方式也采用分段重叠的计算方式,从而能够更好的体现出频谱的细节。总之,与传统数字示波器频谱分析相比,采用R&S示波器频谱分析结构主要具有如下几点好处: 由于采用硬件处理等方式,频谱分析速度快,能做到实时的频谱分析; 频谱分析设置同频谱分析仪类似,直接对频谱参数进行设置,而不再需要进行复杂的时域参数调整; 具有大的动态范围; 即本文讨论的重点,由于采用了DDC结构,可以将信号先下变频到基带,再以较低的采样频率对其进行重采样,从而在有限的存储空间内能够采集最长时间的信号,根据公式(6)可以很好的保证频率分辨率(RBW)。即不用再在信号频率与RBW之间纠结折衷的方案。对此我们进行以下实验。使用信号源产生频率为3GHz的单频正弦波信号。如果使用传统示波器频谱分析方法,采样率必须设置为6GSa/s以上信号才不至于混叠,那么根据公式(6)和(7),在有限的存储空间内必不能得到很好的RBW。但如果使用R&S示波器频谱分析方法,设置如图18所示:

图17 R&S数字示波器频谱分析设置与传统数字示波器相比,R&S示波器引入了DDC模块,使信号在FFT之前先下变频到基带。设置中心频率Center frequency等效于设置本振频率,使信号下变频到基带,因此对基带信号进行重采样时,即使用较低的采样频率也不会造成信号混叠,从而在有限的存储空间中能采集最长时间的信号,因此频率分辨率(RBW)能够得到有效的保证。通过设置频率跨度Frequency span,可以在硬件上将FFT的计算范围缩小到所设定的带宽内,而不用对整个频率范围都进行FFT计算,从而提高处理速度。此外,FFT的计算方式也采用分段重叠的计算方式,从而能够更好的体现出频谱的细节。总之,与传统数字示波器频谱分析相比,采用R&S示波器频谱分析结构主要具有如下几点好处: 由于采用硬件处理等方式,频谱分析速度快,能做到实时的频谱分析; 频谱分析设置同频谱分析仪类似,直接对频谱参数进行设置,而不再需要进行复杂的时域参数调整; 具有大的动态范围; 即本文讨论的重点,由于采用了DDC结构,可以将信号先下变频到基带,再以较低的采样频率对其进行重采样,从而在有限的存储空间内能够采集最长时间的信号,根据公式(6)可以很好的保证频率分辨率(RBW)。即不用再在信号频率与RBW之间纠结折衷的方案。对此我们进行以下实验。使用信号源产生频率为3GHz的单频正弦波信号。如果使用传统示波器频谱分析方法,采样率必须设置为6GSa/s以上信号才不至于混叠,那么根据公式(6)和(7),在有限的存储空间内必不能得到很好的RBW。但如果使用R&S示波器频谱分析方法,设置如图18所示: 图18 R&S数字示波器频谱分析设置中心频率设为3GHz,RBW设为5kHz,窗函数采用Blackman Harris窗。频谱分析结果如图19所示。我们注意到,由于采用了DDC结构,采样率设置为了2.5GSa/s,并不需要满足信号频率的2倍以上关系,因为此时的采样率在频谱分析中实际为重采样率。在频域测量结果中可以看出,信号频率为3GHz,与信号源输出频率一致。因此,可以看出使用R&S示波器频谱分析结构,即使对于高频率的信号,仍然能够有很好的频率分辨率。

图18 R&S数字示波器频谱分析设置中心频率设为3GHz,RBW设为5kHz,窗函数采用Blackman Harris窗。频谱分析结果如图19所示。我们注意到,由于采用了DDC结构,采样率设置为了2.5GSa/s,并不需要满足信号频率的2倍以上关系,因为此时的采样率在频谱分析中实际为重采样率。在频域测量结果中可以看出,信号频率为3GHz,与信号源输出频率一致。因此,可以看出使用R&S示波器频谱分析结构,即使对于高频率的信号,仍然能够有很好的频率分辨率。 图19 R&S数字示波器频谱分析结果04小结通过以上讨论可以看出,R&S数字示波器采用DDC技术,无论是在射频信号采集分析(I/Q解调)还是在频域分析中,都能最大限度的利用示波器宝贵的存储空间,将信号的多域联合分析发挥的淋漓尽致。特别推荐互相鄙视的“模电”和“数电”约了一架,结果发现……

图19 R&S数字示波器频谱分析结果04小结通过以上讨论可以看出,R&S数字示波器采用DDC技术,无论是在射频信号采集分析(I/Q解调)还是在频域分析中,都能最大限度的利用示波器宝贵的存储空间,将信号的多域联合分析发挥的淋漓尽致。特别推荐互相鄙视的“模电”和“数电”约了一架,结果发现…… VCC、 VDD、VEE、VSS 电压理解

VCC、 VDD、VEE、VSS 电压理解 涨姿势!高手带你全面了解嵌入式C语言可靠性设计

涨姿势!高手带你全面了解嵌入式C语言可靠性设计

相关文章:

- 泰克推出为中国高院设计的数字中文示波器(05-08)

- 示波器部分旋钮或开关的作用(05-08)

- 示波器的两种反应特性(05-08)

- 请问怎样用示波器测试小于1毫秒的时间?(05-08)

- 选择数字示波器要注意哪些方面(05-08)

- 示波器的基本结构(05-08)

射频专业培训教程推荐