四大主流的高级封装标准

05-08

转载自:微信公众号半导体新闻现在,主流的高级封装标准包括:1、三星主推的Wide-IO标准

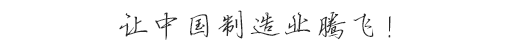

转载自:微信公众号半导体新闻现在,主流的高级封装标准包括:1、三星主推的Wide-IO标准 Wide-IO技术目前已经到了第二代,可以实现最多512bit的内存接口位宽,内存接口操作频率最高可达1GHz,总的内存带宽可达68GBps,是最先进的DDR4接口带宽(34GBps)的两倍。Wide-IO在内存接口操作频率并不高,其主要目标市场是要求低功耗的移动设备。 2、AMD,NVIDIA和海力士主推的HBM标准HBM(High-Bandwidth Memory,高带宽内存)标准主要针对显卡市场,它的接口操作频率和带宽要高于Wide-IO技术,当然功耗也会更高。HBM使用3DIC技术把多块内存芯片堆叠在一起,并使用2.5D技术把堆叠内存芯片和GPU在载板上实现互联。目前AMD在2015年推出的FIJI旗舰显卡首先使用HBM标准,显存带宽可达512 GBps,而显卡霸主Nvidia也紧追其后,在2016年Pascal显卡中预期使用HBM标准实现1 TBps的显存带宽。

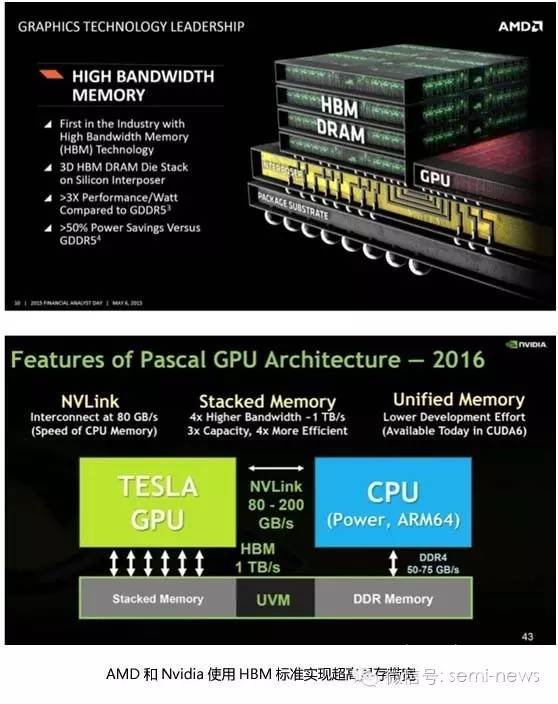

Wide-IO技术目前已经到了第二代,可以实现最多512bit的内存接口位宽,内存接口操作频率最高可达1GHz,总的内存带宽可达68GBps,是最先进的DDR4接口带宽(34GBps)的两倍。Wide-IO在内存接口操作频率并不高,其主要目标市场是要求低功耗的移动设备。 2、AMD,NVIDIA和海力士主推的HBM标准HBM(High-Bandwidth Memory,高带宽内存)标准主要针对显卡市场,它的接口操作频率和带宽要高于Wide-IO技术,当然功耗也会更高。HBM使用3DIC技术把多块内存芯片堆叠在一起,并使用2.5D技术把堆叠内存芯片和GPU在载板上实现互联。目前AMD在2015年推出的FIJI旗舰显卡首先使用HBM标准,显存带宽可达512 GBps,而显卡霸主Nvidia也紧追其后,在2016年Pascal显卡中预期使用HBM标准实现1 TBps的显存带宽。 3、美光主推HMC技术HMC(Hybrid Memory Cube)标准由美光主推,目标市场是高端服务器市场,尤其是针对多处理器架构。HMC使用堆叠的DRAM芯片实现更大的内存带宽。另外HMC通过3DIC异质集成技术把内存控制器(memory controller)集成到DRAM堆叠封装里。以往内存控制器都做在处理器里,所以在高端服务器里,当需要使用大量内存模块时,内存控制器的设计非常复杂。现在把内存控制器集成到内存模块内,则内存控制器的设计就大大地简化了。最后,HMC使用高速串行接口(SerDes)来实现高速接口,适合处理器和内存距离较远的情况(例如处理器和内存在两张不同的PCB板上)。相较而言,Wide-IO和HBM都要求处理器和内存在同一个封装内。

3、美光主推HMC技术HMC(Hybrid Memory Cube)标准由美光主推,目标市场是高端服务器市场,尤其是针对多处理器架构。HMC使用堆叠的DRAM芯片实现更大的内存带宽。另外HMC通过3DIC异质集成技术把内存控制器(memory controller)集成到DRAM堆叠封装里。以往内存控制器都做在处理器里,所以在高端服务器里,当需要使用大量内存模块时,内存控制器的设计非常复杂。现在把内存控制器集成到内存模块内,则内存控制器的设计就大大地简化了。最后,HMC使用高速串行接口(SerDes)来实现高速接口,适合处理器和内存距离较远的情况(例如处理器和内存在两张不同的PCB板上)。相较而言,Wide-IO和HBM都要求处理器和内存在同一个封装内。 Wide-IO标准、HBM标准、HMC技术都和内存相关,下表是有关Wide-IO, HMC, HBM及DDR标准比较。

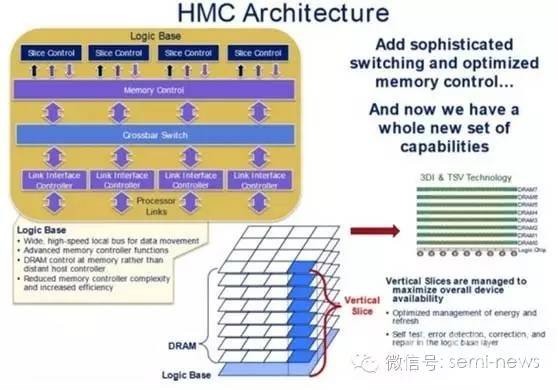

Wide-IO标准、HBM标准、HMC技术都和内存相关,下表是有关Wide-IO, HMC, HBM及DDR标准比较。 Wide-IO, HMC, HBM及DDR标准比较4、TSMC主推的CoWoS和InFO技术CoWoS(Chip-on-Wafer-on-Substrate)和InFO(Integrated Fan Out)是台积电推出的 2.5D封装技术,称为晶圆级封装。台积电的2.5D封装技术把芯片封装到硅载片上,并使用硅载片上的高密度走线进行互联。CoWoS针对高端市场,连线数量和封装尺寸都比较大。InFO针对性价比市场,封装尺寸较小,连线数量也比较少。目前InFO技术已经得到业界认可,苹果在iPhone7中使用的A10处理器即将采用InFO技术。

Wide-IO, HMC, HBM及DDR标准比较4、TSMC主推的CoWoS和InFO技术CoWoS(Chip-on-Wafer-on-Substrate)和InFO(Integrated Fan Out)是台积电推出的 2.5D封装技术,称为晶圆级封装。台积电的2.5D封装技术把芯片封装到硅载片上,并使用硅载片上的高密度走线进行互联。CoWoS针对高端市场,连线数量和封装尺寸都比较大。InFO针对性价比市场,封装尺寸较小,连线数量也比较少。目前InFO技术已经得到业界认可,苹果在iPhone7中使用的A10处理器即将采用InFO技术。 InFO和CoWoS技术插播一则小广告本联盟投稿微信97915500,优质内容免费推送

InFO和CoWoS技术插播一则小广告本联盟投稿微信97915500,优质内容免费推送 文章整理自网络,如有侵权请联系微信97915500芯榜(IC大数据专家) 唯有大数据才能拯救中国半导体

文章整理自网络,如有侵权请联系微信97915500芯榜(IC大数据专家) 唯有大数据才能拯救中国半导体 半导体圈(icquan)这里才是半导体人的人脉圈子。100+微信群等着你.

半导体圈(icquan)这里才是半导体人的人脉圈子。100+微信群等着你. 半导体行业观察(icbank)半导体行业观察:半导体行业第一垂直媒体【www.icbank.cc】

半导体行业观察(icbank)半导体行业观察:半导体行业第一垂直媒体【www.icbank.cc】 半导体行业联盟(icunion)中国最大的非盈利组织联盟,10万人共同关注.

半导体行业联盟(icunion)中国最大的非盈利组织联盟,10万人共同关注. 合作方式1.合作推广(微信:97915500)2.有偿投稿/爆料(邮箱: 416000888@qq.com).个人公众号了

合作方式1.合作推广(微信:97915500)2.有偿投稿/爆料(邮箱: 416000888@qq.com).个人公众号了

相关文章:

- IC封装术语解析(05-08)

- protel元件封装总结(05-08)

- 0402封装二极管用于单端混频器的型号?(05-08)

- LTCC基板与封装的一体化制造(05-08)

- 请教各位——用那个软件设计封装?(05-08)

- 用于GHz芯片级封装的高密度插座(05-08)

射频专业培训教程推荐