HFSS:关于interpolating频率扫描方式的疑惑?

遇到了一个不知道是不是正常的“问题”:

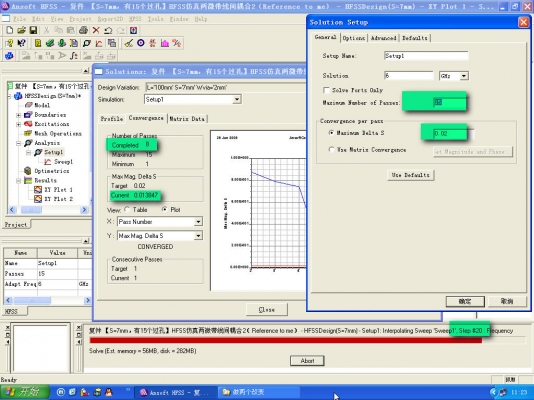

使用插值扫描,求解步数和精度设置,都已经满足设置条件了,可是软件仍然在继续分析,为什么?

1、红色进度条处出现的step#20 等等,是代表什么意义?是计算步数吗?

2、与Edit sweep中的max solution所设置的数值有关系吗?

我理解 按照你的设置count 500 ,step#20 应该是正常的,最大应该到500,不知对否?

没有收敛的话会继续算的,除非到了你设置的值

是有點怪,你的 Delta S 已經小於 0.02了,按理應該結束了,為什麼呢?

可以先看一下 [profile],看看最後是否有 Interpolating sweep converged.

會不會是你的 project 有用中文名稱的問題?

TO marshal_hyh:呵呵,这个我也不知道

TO 00d44: 看收敛,一共有几个标准呢? 我只知道有两个啊

TO honejing:耐着性子等到最终分析完成了,倒是有Interpolating sweep converged的字样(没完成之前倒是没注意看这个),可是结果却与我预想的不一样,呵呵,也不知道是不是“中间的看似多出来的那些分析”导致的呢?

PS:之前我也有好几个算例,也使用中文名字了,结果与我预想的基本一致,貌似不是中文名字的事啊

那就把結果貼上來看看吧!

TO honejing:

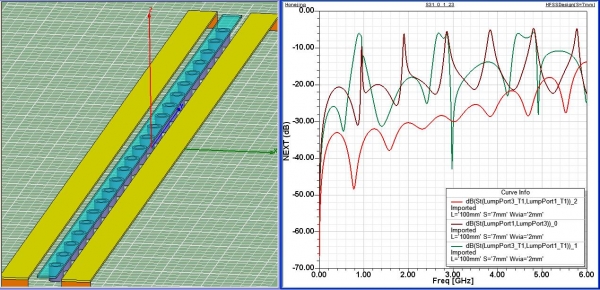

图片是S31参数,

计算时间13个小时,最终倒也是收敛了,

仿真的是加过孔保护带减小串扰的算例,加了25个过孔(本意是想消除谐振尖峰的),可在一些频点上还是有谐振的存在,

honejing,有这方面的设计经验吗?共同研究下

从lz的截图来看,是初始设置中心频率点6G,最大15步,最小1步,目标是小于0.02。实际分析6GHz中,算了8步已经达到0.013847<0.02。

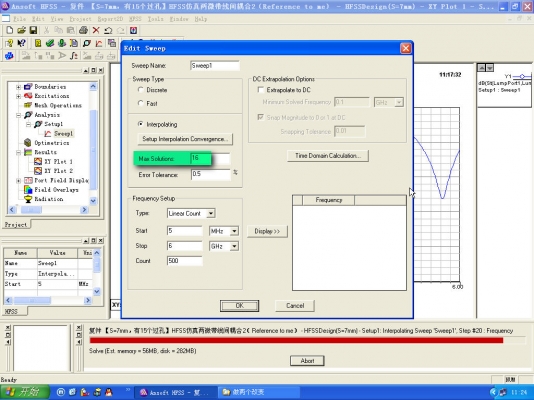

然后在扫描频率的时候是选择插值扫频,5MHz~6GHz &500count(我觉得这个5MHz是不是有点太小了呢?!),然后要求在插值中是最多插值16个频率点(0.5%容差)。

实际分析中插值点越多花时间越长。特别是响应曲线特别不平坦的时候为了达到要求的容差,插值就越多。这样就会远大于之前分析中心频率6GHz时候的时间啦。

三个扫频方式中

第一个是离散扫频,就是你设置了多少个扫频点就要算多少次的。原则上是最慢的

最快就是第二个fast sweep,只是算一个频率点然后外推。

最后一个是插值扫频,是兼顾速度和精度的一个折中方案。

所以建议用fast,一般算阻抗的话在中心频率6GHz ,计算1GHz~11GHz 得到的结果精度还算可以接受的

另外建议在利用软件的时候都尽量用字母组合的名字!

TO mrtsui:

1、你的意思是说,之所以在精度收敛条件都已满足的情况下,仿真还在进行,

是因为还没有满足设定的插值收敛容差,是吗?

那这个收敛容差有没有什么设置的经验规律可循呢?(我都是按默认了,针对不同模型,算的时间可能就会很长)

2、Fast扫描,计算一个频率点然后外推,这一个频率点是指在setup中设置的求解点频吧?

PS:这个容差什么时候满足0.5%(举软件默认的数值为例),在进度条中或者在哪我们能看到吗?

我可以猜的出來你想做什麼,若從頻域來看結果,你會覺得疑惑,但是這樣的S31,

應該是正確的,你可能疑惑為什麼有加保护带 (Guard trace) 反而比沒有的還差。

注意在低頻段 (1-2GHz以內) NEXT 應該是有比較好的,至於更高頻的諧振點就是

加Guard trace又沒有好好接地的副作用,若把萃取出來的S參數拿到時域跑電壓波形,

你可以比較容易比出來少的過孔與足夠的過孔的差異。

所以,加Guard trace 又不打足夠的過孔,一定是禍害,它可能比留空還糟糕。

也許可以搜一下這篇論文 : "Using via fences for crosstalk reduction in PCB circuit"

TO honejing:

呵呵,感觉和你挺有默契的啊!

这篇文章我看过了,也按照作者的例子仿真过,可是作者提出加via fence会增加串扰的那个模型,就是他的那个Fig.5(c)了,我设置的参数和他的只差0.0几个毫米而已(我取了整数,比如他的地为1.575mm,我取1.6mm等等),仿真3vias时,结果差不太多,可以接受,可是仿真25vias时,并不像他所给出的Fig.6(b、c)那样啊,其结果与3vias时差不多啊!

PS:看别的IEEE文章,有人得出的结论是:有via有fence的情况下,过孔数量的改变(改变过孔间距获得)对串扰幅度的影响几乎不变啊!(当然了,两者的模型是不同的,到现在我也没弄明白到底那篇IEEE是对的!)

honejing是否练习过这个模型?特别是加25vias的情况?

To llqs123:

沒有實際做過,但若你可以把 project 放上來,也許我可以抽空跑跑看,也許可以發現哪裡有問題。

你的問題是,你只是把 Substrate 挖了個洞,實際並沒有導體把 via fence 連結到 GND plane,

你只要把現在挖的洞先用PEC 圓柱體填滿,再換選材料Vacuum,再畫一個小一點的同心圓柱體,然後

兩個 object 相減,就可以相當於 via 的效果,(若直接用實體PEC圓柱上下連接也行,只是結果會一些小差異)。由於修改及跑的時間有些長,我只做了一個 via 的驗證,0.5GHz 已有-6dB的改善,其他的你就自己試試,相信會有你想要的結果。

另外上次所提的那篇論文 "Using via fences for crosstalk reduction in PCB circuit" 我只看過部份的

結論圖,沒有全文,若是你有電子檔,能否貢獻一下呢?

The result,

Q1:是的,继续仿真是在仿真次数不大于你设定的最多次数,而且所观察数据曲线容差还大于之前设定的容差值的情况下产生!

Q2:这个问题我目前没有做过仔细评估,不好回答你。若是这个问题对你很重要的话建议你自己做一个仿真评估,无非就是多好几度电啦!电脑不懂要工资的,呵呵。但是有一点你可以基本相信,那就是Ansoft HFSS的默认设置在大部分情况下是可以用的!这也是她之所以强的原因之一。

不知这个回答是否可以?

预祝你能成功解决这个困惑。 /share

TO mrtsui:

感谢你的回复!

看来需要以后在仿真过程中,一点一点的试验、发现及总结了,呵呵!

相关文章:

- 宇宙窗口的频率是多少(05-08)

- 请问:如何在同一张图里看不同模型在同一频率的方向图(05-08)

- 问个关于CST中仿真频率设置的问题(05-08)

- 在30G以上的频率中CST如何馈电(05-08)

- HFSS中如何得到天线最大增益频率曲线(05-08)

- 求助一个频率搬移的问题(05-08)