|

Ansoft Designer / Ansys Designer 在线帮助文档: Ansoft Designer / Ansys Designer 在线帮助文档:

System Simulator >

Discrete Time Analysis >

Linear Electrical Discrete Time Simulation with Convolution >

Step 3: Computing the total (signal plus noise) discrete time output voltages of an electrical sub-design

Step 3: Computing the total (signal plus noise)

discrete time output voltages of an electrical sub-design

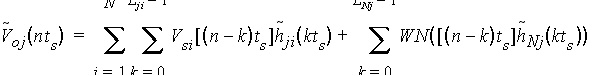

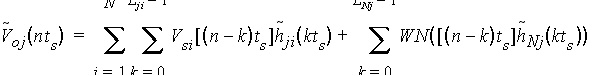

After extracting the discrete time impulse and noise

responses, the total discrete time complex voltage envelope at the jth

output port is computed using the convolution integral (in discrete

form):

where:

n =

0,1,2,…

ts = Simulation time step

of the input signals.

WNj = Unity-variance discrete

white Gaussian noise generated for the jth external port using a random

seed. This noise is generated independently of other external ports.

Note

|

Setting the parameter

fs

and the control parameter MIN_BW

for discrete time analysis is critical for meaningful discrete time

simulations of mixed mode systems. This will be discussed in more detail

later (see Setting

Discrete Time Simulation Control Parameters - Convolution).

|

Note

|

The inputs to

a linear electrical sub-design may have different carrier frequencies

as long as the maximum frequency carrier separation does not exceed

half the sampling frequency of the input signals.

|

Note

|

Different inputs

to a linear electrical sub-design are not allowed to have different

sampling frequencies (i.e., different simulation time step). If the

simulator detects this problem, an error message will be displayed during

analysis.

|

HFSS视频教程

ADS视频教程

CST视频教程

Ansoft Designer 中文教程

|